| ID |

Date |

Author |

Category |

Subject |

|

43

|

Sat Mar 28 18:11:13 2020 |

Alex, Yuri | General | no beam in the ESR | Yuri and Sergey (on phone) have investigated extensively the problem with having no beam in the ESR. The FRS has been checked and seems OK. The ESR is fine as well.

The problem seems to be the timing. Ths SIS and the ESR seem to be completely out of synchronization. The on-call service for the control system has been called. |

|

178

|

Thu Nov 19 09:14:40 2020 |

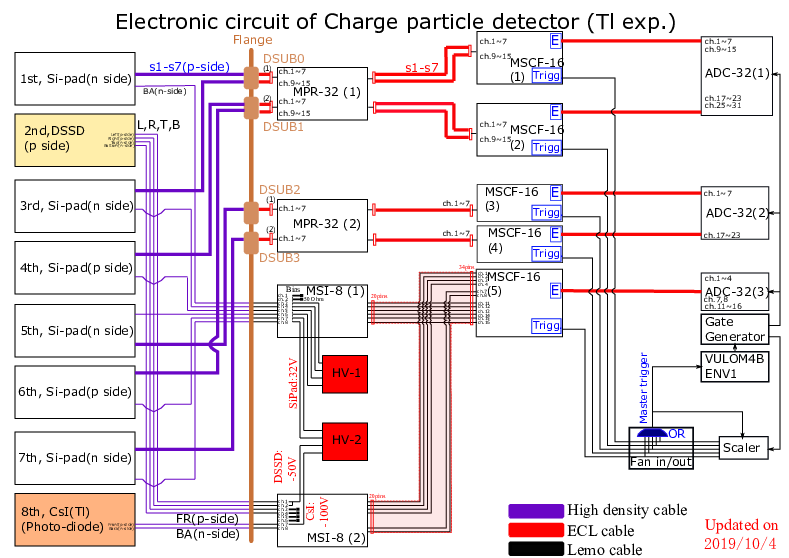

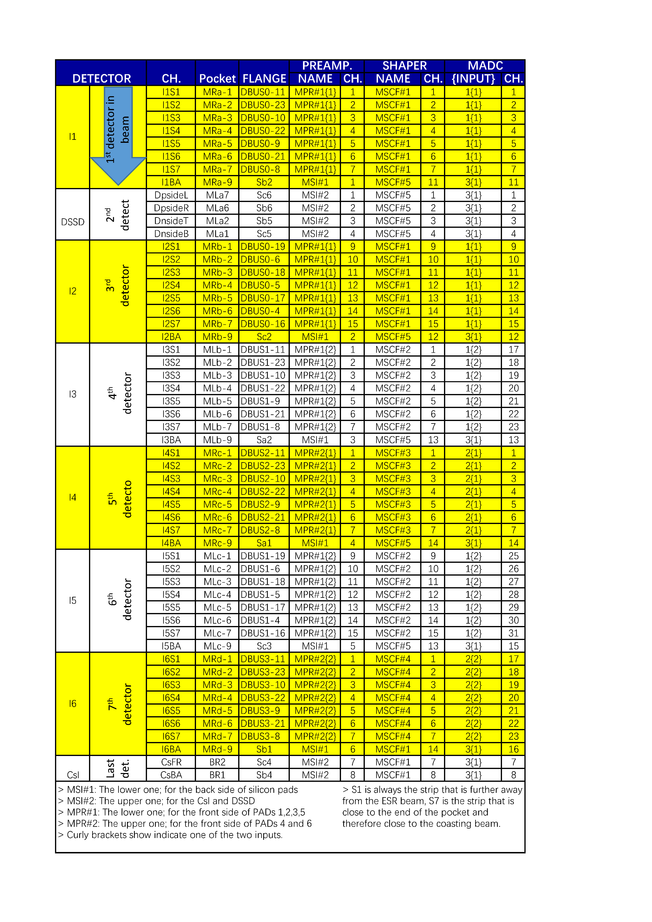

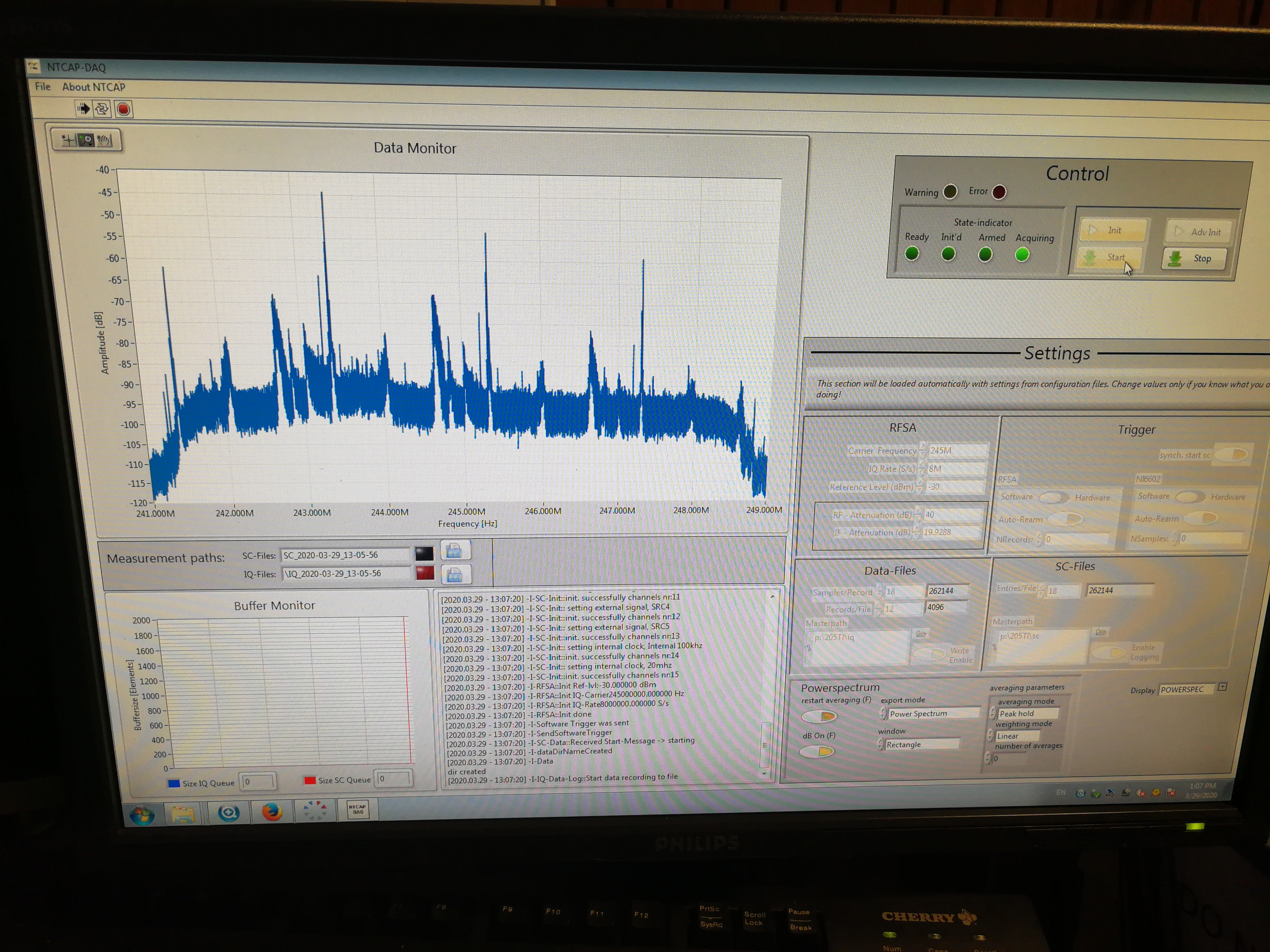

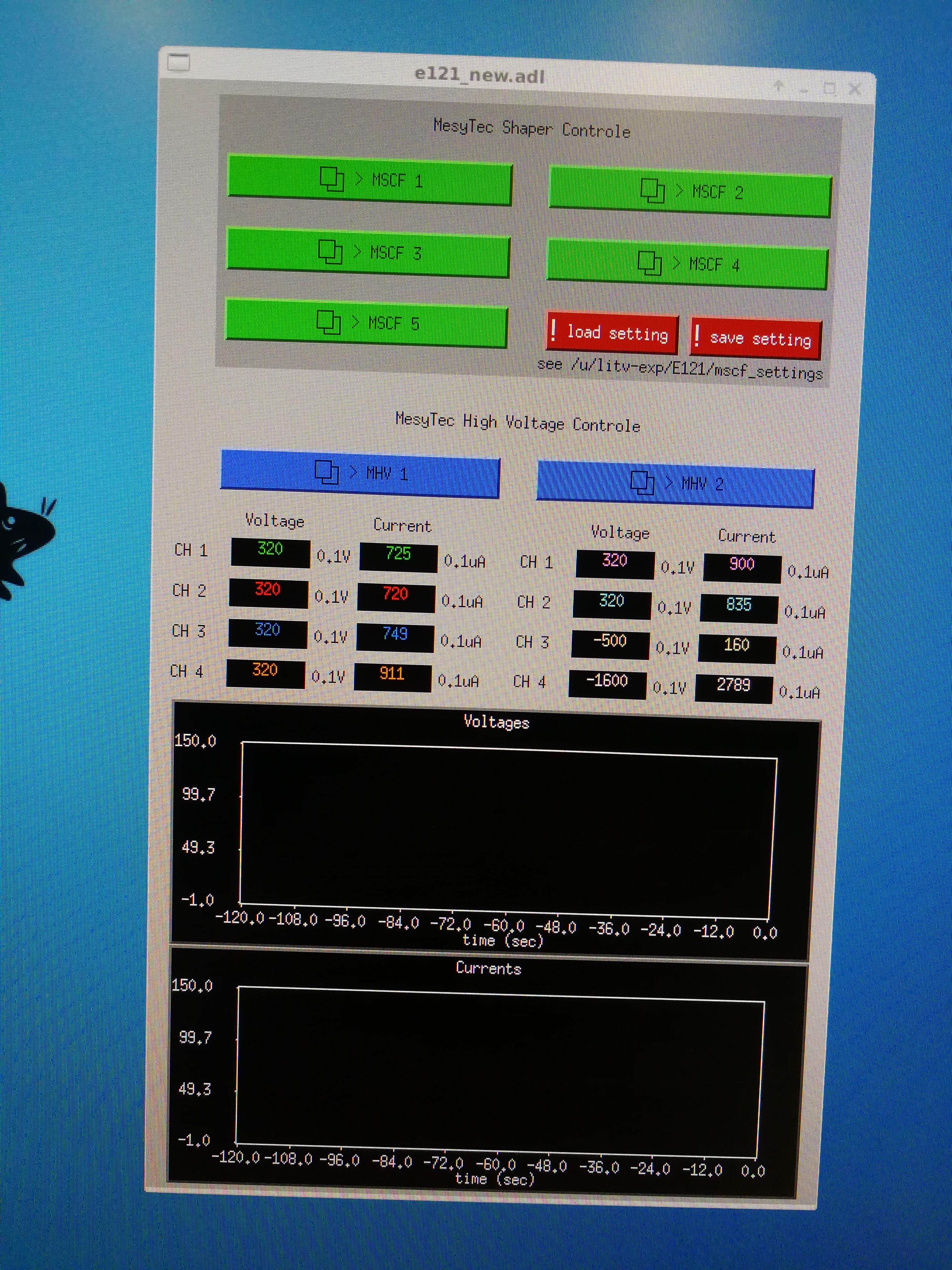

Jan | Detectors | remote MSCF settings for CsISiPHOS | Attached is a list of all set values for the 5 MSCF shaper modules.

This was done prior to run0251, which served as a final benchmark for those settings.

See: https://elog.gsi.de/esr/E121/62

And https://elog.gsi.de/esr/E121/104

The det. to MSCF assignment is the following:

MSCF 1: Si-pad 1 + 2 p-side/strips (ch. 1-7 + ch. 9-15)

MSCF 2: Si-pad 3 + 4 p-side/strips (ch. 1-7 + ch. 9-15)

MSCF 3: Si-pad 5 p-side/strips (ch. 1-7)

MSCF 4: Si-pad 6 p-side/strips (ch. 1-7)

MSCF 5: DSSD (ch. 1 - 4); CsI (ch. 7 & 8); Si-pad n-sides (ch. 11 - 16)

Note that only the pre-amplification stage of the MSI-8 amplifiers were used for all channels. |

| Attachment 1: setting.1585477986

|

1585477986

Sun Mar 29 12:33:06 CEST 2020

ringpi:mrcc:mscf1:getGainCommon 15

ringpi:mrcc:mscf1:getShapingTimeCommon 2

ringpi:mrcc:mscf1:getThresholdCommon 244

ringpi:mrcc:mscf1:getPzCommon 100

ringpi:mrcc:mscf2:getGainCommon 15

ringpi:mrcc:mscf2:getShapingTimeCommon 2

ringpi:mrcc:mscf2:getThresholdCommon 244

ringpi:mrcc:mscf2:getPzCommon 100

ringpi:mrcc:mscf3:getGainCommon 15

ringpi:mrcc:mscf3:getShapingTimeCommon 2

ringpi:mrcc:mscf3:getThresholdCommon 244

ringpi:mrcc:mscf3:getPzCommon 100

ringpi:mrcc:mscf4:getGainCommon 15

ringpi:mrcc:mscf4:getShapingTimeCommon 2

ringpi:mrcc:mscf4:getThresholdCommon 244

ringpi:mrcc:mscf4:getPzCommon 100

ringpi:mrcc:mscf5:getGainCommon 5

ringpi:mrcc:mscf5:getShapingTimeCommon 2

ringpi:mrcc:mscf5:getThresholdCommon 150

ringpi:mrcc:mscf5:getPzCommon 100

ringpi:mrcc:mscf1:getGain1 15

ringpi:mrcc:mscf1:getGain2 15

ringpi:mrcc:mscf1:getGain3 15

ringpi:mrcc:mscf1:getGain4 15

ringpi:mrcc:mscf1:getShapingTime1 2

ringpi:mrcc:mscf1:getShapingTime2 2

ringpi:mrcc:mscf1:getShapingTime3 2

ringpi:mrcc:mscf1:getShapingTime4 2

ringpi:mrcc:mscf2:getGain1 15

ringpi:mrcc:mscf2:getGain2 15

ringpi:mrcc:mscf2:getGain3 15

ringpi:mrcc:mscf2:getGain4 15

ringpi:mrcc:mscf2:getShapingTime1 2

ringpi:mrcc:mscf2:getShapingTime2 2

ringpi:mrcc:mscf2:getShapingTime3 2

ringpi:mrcc:mscf2:getShapingTime4 2

ringpi:mrcc:mscf3:getGain1 15

ringpi:mrcc:mscf3:getGain2 15

ringpi:mrcc:mscf3:getGain3 15

ringpi:mrcc:mscf3:getGain4 15

ringpi:mrcc:mscf3:getShapingTime1 2

ringpi:mrcc:mscf3:getShapingTime2 2

ringpi:mrcc:mscf3:getShapingTime3 2

ringpi:mrcc:mscf3:getShapingTime4 2

ringpi:mrcc:mscf4:getGain1 15

ringpi:mrcc:mscf4:getGain2 15

ringpi:mrcc:mscf4:getGain3 0

ringpi:mrcc:mscf4:getGain4 0

ringpi:mrcc:mscf4:getShapingTime1 2

ringpi:mrcc:mscf4:getShapingTime2 2

ringpi:mrcc:mscf4:getShapingTime3 2

ringpi:mrcc:mscf4:getShapingTime4 2

ringpi:mrcc:mscf5:getGain1 8

ringpi:mrcc:mscf5:getGain2 3

ringpi:mrcc:mscf5:getGain3 6

ringpi:mrcc:mscf5:getGain4 6

ringpi:mrcc:mscf5:getShapingTime1 2

ringpi:mrcc:mscf5:getShapingTime2 2

ringpi:mrcc:mscf5:getShapingTime3 2

ringpi:mrcc:mscf5:getShapingTime4 2

ringpi:mrcc:mscf1:getThreshold1 20

ringpi:mrcc:mscf1:getThreshold2 20

ringpi:mrcc:mscf1:getThreshold3 20

ringpi:mrcc:mscf1:getThreshold4 20

ringpi:mrcc:mscf1:getThreshold5 20

ringpi:mrcc:mscf1:getThreshold6 20

ringpi:mrcc:mscf1:getThreshold7 0

ringpi:mrcc:mscf1:getThreshold8 0

ringpi:mrcc:mscf1:getThreshold9 20

ringpi:mrcc:mscf1:getThreshold10 20

ringpi:mrcc:mscf1:getThreshold11 20

ringpi:mrcc:mscf1:getThreshold12 20

ringpi:mrcc:mscf1:getThreshold13 20

ringpi:mrcc:mscf1:getThreshold14 0

ringpi:mrcc:mscf1:getThreshold15 0

ringpi:mrcc:mscf1:getThreshold16 0

ringpi:mrcc:mscf1:getPz1 100

ringpi:mrcc:mscf1:getPz2 100

ringpi:mrcc:mscf1:getPz3 100

ringpi:mrcc:mscf1:getPz4 128

ringpi:mrcc:mscf1:getPz5 100

ringpi:mrcc:mscf1:getPz6 100

ringpi:mrcc:mscf1:getPz7 0

ringpi:mrcc:mscf1:getPz8 0

ringpi:mrcc:mscf1:getPz9 100

ringpi:mrcc:mscf1:getPz10 100

ringpi:mrcc:mscf1:getPz11 100

ringpi:mrcc:mscf1:getPz12 100

ringpi:mrcc:mscf1:getPz13 128

ringpi:mrcc:mscf1:getPz14 0

ringpi:mrcc:mscf1:getPz15 0

ringpi:mrcc:mscf1:getPz16 0

ringpi:mrcc:mscf2:getThreshold1 20

ringpi:mrcc:mscf2:getThreshold2 20

ringpi:mrcc:mscf2:getThreshold3 20

ringpi:mrcc:mscf2:getThreshold4 20

ringpi:mrcc:mscf2:getThreshold5 20

ringpi:mrcc:mscf2:getThreshold6 0

ringpi:mrcc:mscf2:getThreshold7 0

ringpi:mrcc:mscf2:getThreshold8 0

ringpi:mrcc:mscf2:getThreshold9 20

ringpi:mrcc:mscf2:getThreshold10 20

ringpi:mrcc:mscf2:getThreshold11 20

ringpi:mrcc:mscf2:getThreshold12 20

ringpi:mrcc:mscf2:getThreshold13 0

ringpi:mrcc:mscf2:getThreshold14 0

ringpi:mrcc:mscf2:getThreshold15 0

ringpi:mrcc:mscf2:getThreshold16 0

ringpi:mrcc:mscf2:getPz1 128

ringpi:mrcc:mscf2:getPz2 128

ringpi:mrcc:mscf2:getPz3 100

ringpi:mrcc:mscf2:getPz4 128

ringpi:mrcc:mscf2:getPz5 100

ringpi:mrcc:mscf2:getPz6 100

ringpi:mrcc:mscf2:getPz7 0

ringpi:mrcc:mscf2:getPz8 0

ringpi:mrcc:mscf2:getPz9 100

ringpi:mrcc:mscf2:getPz10 100

ringpi:mrcc:mscf2:getPz11 100

ringpi:mrcc:mscf2:getPz12 100

ringpi:mrcc:mscf2:getPz13 0

ringpi:mrcc:mscf2:getPz14 0

ringpi:mrcc:mscf2:getPz15 0

ringpi:mrcc:mscf2:getPz16 0

ringpi:mrcc:mscf3:getThreshold1 20

ringpi:mrcc:mscf3:getThreshold2 20

ringpi:mrcc:mscf3:getThreshold3 20

ringpi:mrcc:mscf3:getThreshold4 20

ringpi:mrcc:mscf3:getThreshold5 20

ringpi:mrcc:mscf3:getThreshold6 0

ringpi:mrcc:mscf3:getThreshold7 0

ringpi:mrcc:mscf3:getThreshold8 0

ringpi:mrcc:mscf3:getThreshold9 20

ringpi:mrcc:mscf3:getThreshold10 20

ringpi:mrcc:mscf3:getThreshold11 20

ringpi:mrcc:mscf3:getThreshold12 20

ringpi:mrcc:mscf3:getThreshold13 0

ringpi:mrcc:mscf3:getThreshold14 0

ringpi:mrcc:mscf3:getThreshold15 0

ringpi:mrcc:mscf3:getThreshold16 0

ringpi:mrcc:mscf3:getPz1 128

ringpi:mrcc:mscf3:getPz2 128

ringpi:mrcc:mscf3:getPz3 128

ringpi:mrcc:mscf3:getPz4 128

ringpi:mrcc:mscf3:getPz5 128

ringpi:mrcc:mscf3:getPz6 0

ringpi:mrcc:mscf3:getPz7 0

ringpi:mrcc:mscf3:getPz8 0

ringpi:mrcc:mscf3:getPz9 128

ringpi:mrcc:mscf3:getPz10 128

ringpi:mrcc:mscf3:getPz11 128

ringpi:mrcc:mscf3:getPz12 128

ringpi:mrcc:mscf3:getPz13 0

ringpi:mrcc:mscf3:getPz14 0

ringpi:mrcc:mscf3:getPz15 0

ringpi:mrcc:mscf3:getPz16 0

ringpi:mrcc:mscf4:getThreshold1 244

ringpi:mrcc:mscf4:getThreshold2 244

ringpi:mrcc:mscf4:getThreshold3 244

ringpi:mrcc:mscf4:getThreshold4 244

ringpi:mrcc:mscf4:getThreshold5 244

ringpi:mrcc:mscf4:getThreshold6 244

ringpi:mrcc:mscf4:getThreshold7 244

ringpi:mrcc:mscf4:getThreshold8 244

ringpi:mrcc:mscf4:getThreshold9 244

ringpi:mrcc:mscf4:getThreshold10 244

ringpi:mrcc:mscf4:getThreshold11 244

ringpi:mrcc:mscf4:getThreshold12 244

ringpi:mrcc:mscf4:getThreshold13 244

ringpi:mrcc:mscf4:getThreshold14 244

ringpi:mrcc:mscf4:getThreshold15 244

ringpi:mrcc:mscf4:getThreshold16 244

ringpi:mrcc:mscf4:getPz1 100

ringpi:mrcc:mscf4:getPz2 100

ringpi:mrcc:mscf4:getPz3 100

ringpi:mrcc:mscf4:getPz4 100

ringpi:mrcc:mscf4:getPz5 100

ringpi:mrcc:mscf4:getPz6 0

ringpi:mrcc:mscf4:getPz7 0

ringpi:mrcc:mscf4:getPz8 0

ringpi:mrcc:mscf4:getPz9 100

ringpi:mrcc:mscf4:getPz10 100

ringpi:mrcc:mscf4:getPz11 100

ringpi:mrcc:mscf4:getPz12 100

ringpi:mrcc:mscf4:getPz13 0

ringpi:mrcc:mscf4:getPz14 0

ringpi:mrcc:mscf4:getPz15 0

ringpi:mrcc:mscf4:getPz16 0

ringpi:mrcc:mscf5:getThreshold1 50

ringpi:mrcc:mscf5:getThreshold2 50

ringpi:mrcc:mscf5:getThreshold3 50

ringpi:mrcc:mscf5:getThreshold4 50

ringpi:mrcc:mscf5:getThreshold5 150

ringpi:mrcc:mscf5:getThreshold6 150

ringpi:mrcc:mscf5:getThreshold7 150

ringpi:mrcc:mscf5:getThreshold8 150

ringpi:mrcc:mscf5:getThreshold9 150

ringpi:mrcc:mscf5:getThreshold10 150

ringpi:mrcc:mscf5:getThreshold11 150

ringpi:mrcc:mscf5:getThreshold12 150

ringpi:mrcc:mscf5:getThreshold13 150

ringpi:mrcc:mscf5:getThreshold14 150

ringpi:mrcc:mscf5:getThreshold15 150

ringpi:mrcc:mscf5:getThreshold16 150

ringpi:mrcc:mscf5:getPz1 100

ringpi:mrcc:mscf5:getPz2 100

ringpi:mrcc:mscf5:getPz3 100

ringpi:mrcc:mscf5:getPz4 100

ringpi:mrcc:mscf5:getPz5 100

ringpi:mrcc:mscf5:getPz6 100

ringpi:mrcc:mscf5:getPz7 100

ringpi:mrcc:mscf5:getPz8 100

ringpi:mrcc:mscf5:getPz9 100

ringpi:mrcc:mscf5:getPz10 100

ringpi:mrcc:mscf5:getPz11 100

ringpi:mrcc:mscf5:getPz12 100

ringpi:mrcc:mscf5:getPz13 100

ringpi:mrcc:mscf5:getPz14 100

ringpi:mrcc:mscf5:getPz15 100

ringpi:mrcc:mscf5:getPz16 100

ringpi:mrcc:mscf1:getSingleChMode 0

ringpi:mrcc:mscf2:getSingleChMode 0

ringpi:mrcc:mscf3:getSingleChMode 0

ringpi:mrcc:mscf4:getSingleChMode 0

ringpi:mrcc:mscf5:getSingleChMode 1

ringpi:mrcc:mscf1:getRcMode 1

ringpi:mrcc:mscf2:getRcMode 1

ringpi:mrcc:mscf3:getRcMode 1

ringpi:mrcc:mscf4:getRcMode 1

ringpi:mrcc:mscf5:getRcMode 1

ringpi:mrcc:mscf1:getAutoPZ 0

ringpi:mrcc:mscf2:getAutoPZ 0

ringpi:mrcc:mscf3:getAutoPZ 0

ringpi:mrcc:mscf4:getAutoPZ 1

ringpi:mrcc:mscf5:getAutoPZ 0

ringpi:mrcc:mscf1:getMultiplicityHi 8

ringpi:mrcc:mscf2:getMultiplicityHi 1

ringpi:mrcc:mscf3:getMultiplicityHi 1

ringpi:mrcc:mscf4:getMultiplicityHi 1

ringpi:mrcc:mscf5:getMultiplicityHi 4

ringpi:mrcc:mscf1:getMultiplicityLo 8

ringpi:mrcc:mscf2:getMultiplicityLo 0

ringpi:mrcc:mscf3:getMultiplicityLo 0

ringpi:mrcc:mscf4:getMultiplicityLo 0

ringpi:mrcc:mscf5:getMultiplicityLo 4

ringpi:mrcc:mscf1:getSumTrgThresh 0

ringpi:mrcc:mscf2:getSumTrgThresh 0

ringpi:mrcc:mscf3:getSumTrgThresh 0

ringpi:mrcc:mscf4:getSumTrgThresh 0

ringpi:mrcc:mscf5:getSumTrgThresh 0

ringpi:mrcc:mscf1:getBlrOn 1

ringpi:mrcc:mscf2:getBlrOn 1

ringpi:mrcc:mscf3:getBlrOn 1

ringpi:mrcc:mscf4:getBlrOn 1

ringpi:mrcc:mscf5:getBlrOn 1

ringpi:mrcc:mscf1:getCoincTime 121

ringpi:mrcc:mscf2:getCoincTime 0

ringpi:mrcc:mscf3:getCoincTime 0

ringpi:mrcc:mscf4:getCoincTime 0

ringpi:mrcc:mscf5:getCoincTime 0

ringpi:mrcc:mscf1:getThreshOffset 0

ringpi:mrcc:mscf2:getThreshOffset 0

ringpi:mrcc:mscf3:getThreshOffset 0

ringpi:mrcc:mscf4:getThreshOffset 0

ringpi:mrcc:mscf5:getThreshOffset 0

ringpi:mrcc:mscf1:getShaperOffset 0

ringpi:mrcc:mscf2:getShaperOffset 0

ringpi:mrcc:mscf3:getShaperOffset 0

ringpi:mrcc:mscf4:getShaperOffset 0

ringpi:mrcc:mscf5:getShaperOffset 0

ringpi:mrcc:mscf1:getBlrThresh 20

ringpi:mrcc:mscf2:getBlrThresh 20

ringpi:mrcc:mscf3:getBlrThresh 25

ringpi:mrcc:mscf4:getBlrThresh 25

ringpi:mrcc:mscf5:getBlrThresh 25

ringpi:mrcc:mscf1:getECLDelay 0

ringpi:mrcc:mscf2:getECLDelay 0

ringpi:mrcc:mscf3:getECLDelay 0

ringpi:mrcc:mscf4:getECLDelay 0

ringpi:mrcc:mscf5:getECLDelay 0

|

| Attachment 2: det_mapping.png

|

|

|

44

|

Sun Mar 29 09:40:35 2020 |

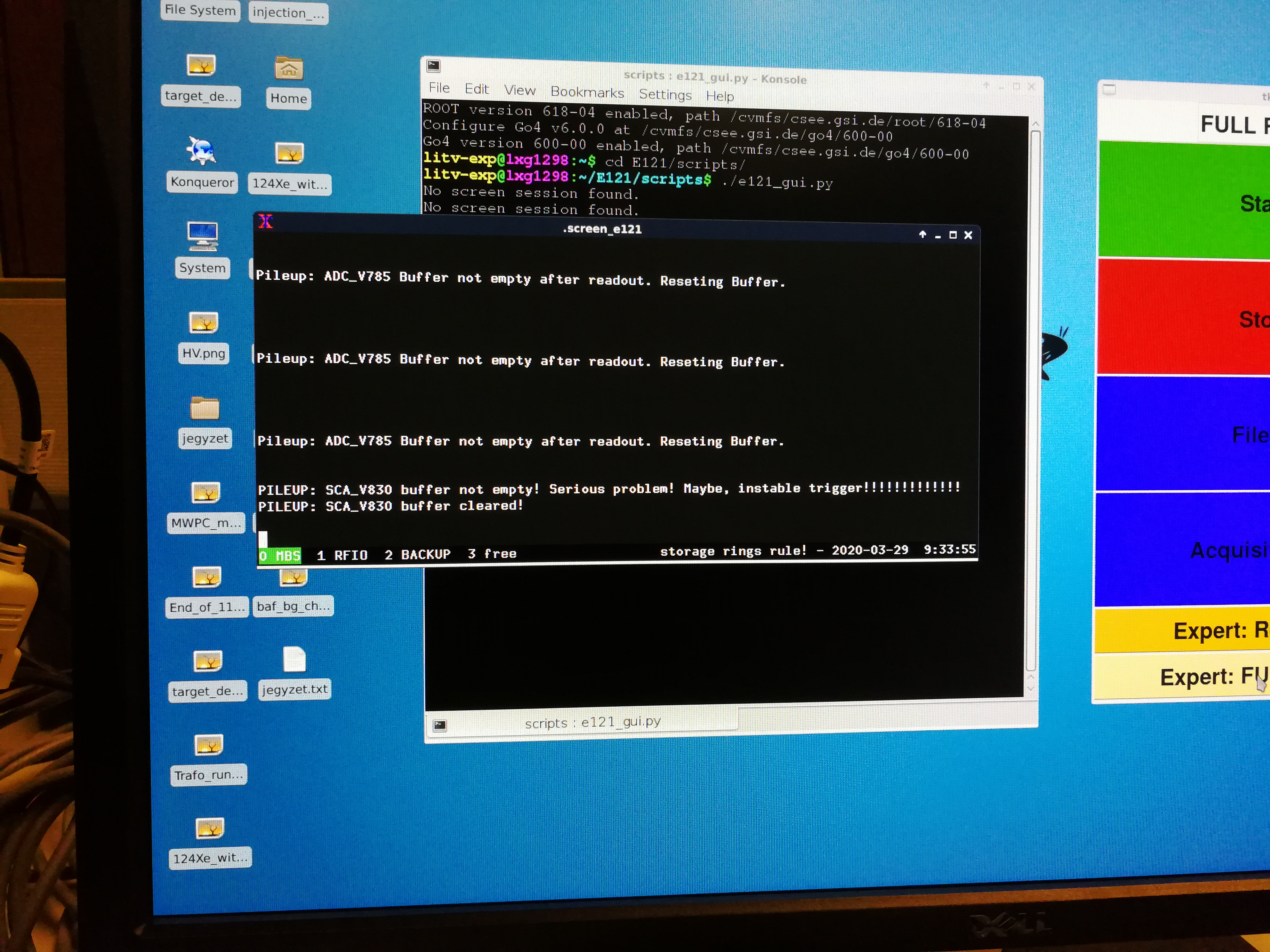

ruijiu | DAQ | restart go4 | go4 crush up.

the problem is

due to mbs.

restart mbs.

see an error.

restart again.

the mbs and go4

are working

working. |

| Attachment 1: IMG_20200329_093354.jpg

|

|

|

177

|

Thu Nov 5 15:13:43 2020 |

Jan | Analysis | root script example | Attached is an example root script/macro that shows how to use scripts for analysis.

Usage:

1. change INPUT and OUTPUT preprocessor variables in e121_analysis.c pointing to your desired input and output root-files.

2. open root and type: root [1] .L e121_analysis.C++

root [2] run() 3. check plots popping up and output files

Hints:

in e121_analysis.C use #include "e121_raw.h" for the original channel names/mapping (e.g. ADC1_1,...)

and use#include "e121_mapped.h" for named channels (e.g. e_csi[0] or e_dssd_top) |

| Attachment 1: e121_analysis.C

|

#define e121_analysis_cxx

// INPUT FILES

#define INPUT1 "/data.local1/E121/root-files/part1/e121_run_0253.root"

//#define INPUT2 ""

//#define INPUT3 ""

//#define INPUT4 ""

//#define INPUT5 ""

//#define INPUT6 ""

//#define INPUT7 ""

//#define INPUT8 ""

//#define INPUT9 ""

//#define INPUT10 ""

//OUTPUT FILE

#define OUTPUT "run253.ana.root"

#include <TH2.h>

#include <TStyle.h>

#include <TCanvas.h>

#include <cmath>

#include <string>

#include <cstdlib>

#include <cstdio>

#include <ctime>

#include <fstream>

#include <iostream>

#include <stdint.h>

#include "TROOT.h"

#include "TAttText.h"

#include "TAxis.h"

#include "TCanvas.h"

#include "TChain.h"

#include "TCut.h"

#include "TF1.h"

#include "TFile.h"

#include "TGraph.h"

#include "TGraphAsymmErrors.h"

#include "TGraphErrors.h"

#include "TH1.h"

#include "THistPainter.h"

#include "TKey.h"

#include "TLatex.h"

#include "TLegend.h"

#include "TMath.h"

#include "TMatrixD.h"

#include "TMinuit.h"

#include "TMultiGraph.h"

#include "TNtuple.h"

#include "TPave.h"

#include "TPaveText.h"

#include "TPoint.h"

#include "TRandom.h"

#include "TRint.h"

#include "TString.h"

#include "TTree.h"

#include "TH1F.h"

#include "TH2F.h"

#include "TSystem.h"

#include "TProfile.h"

#include "TVirtualFitter.h"

#include "TLegend.h"

#include "TColor.h"

#include "TBranch.h"

#include "TList.h"

using namespace std;

void loop(TChain *fChain)

{

if (fChain == 0) return;

//#include "e121_raw.h" // use this for raw mapping of channels

#include "e121_mapped.h" // use this for mapped channel names

///////////////////////////

// histogram definitions //

///////////////////////////

// energy

TList *e_histo= new TList();

TH1D *h_e_pad_1[7];

TH1D *h_e_pad_2[7];

TH1D *h_e_pad_3[7];

TH1D *h_e_pad_4[7];

TH1D *h_e_pad_5[7];

TH1D *h_e_pad_6[7];

TH1D *h_e_pad_n[7];

TH1D *h_e_pad_n_lo[7];

TH1D *h_e_pad_n_hi[7];

char chnumber[300];

for (int i=0;i<7;i++)

{

sprintf(chnumber,"e_pad_1_strip_%d",i);

h_e_pad_1[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_1[i]);

sprintf(chnumber,"e_pad_2_strip_%d",i);

h_e_pad_2[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_2[i]);

sprintf(chnumber,"e_pad_3_strip_%d",i);

h_e_pad_3[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_3[i]);

sprintf(chnumber,"e_pad_4_strip_%d",i);

h_e_pad_4[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_4[i]);

sprintf(chnumber,"e_pad_5_strip_%d",i);

h_e_pad_5[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_5[i]);

sprintf(chnumber,"e_pad_6_strip_%d",i);

h_e_pad_6[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_6[i]);

sprintf(chnumber,"e_pad_%d_n-side",i);

h_e_pad_n[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n[i]);

sprintf(chnumber,"e_pad_%d_n-side_lo",i);

h_e_pad_n_lo[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n_lo[i]);

sprintf(chnumber,"e_pad_%d_n-side_hi",i);

h_e_pad_n_hi[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n_hi[i]);

}

TH1D *h_e_dssd_left=new TH1D("e_dssd_left","e_dssd_left",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_left);

TH1D *h_e_dssd_right=new TH1D("e_dssd_right","e_dssd_right",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_right);

TH1D *h_e_dssd_top=new TH1D("e_dssd_top","e_dssd_top",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_top);

TH1D *h_e_dssd_bottom=new TH1D("e_dssd_bottom","e_dssd_bottom",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_bottom);

TH1D *h_e_csi[2];

h_e_csi[0]=new TH1D("e_csi_0","e_csi_0",4096,0.5,4096.5);

e_histo->Add(h_e_csi[0]);

h_e_csi[1]=new TH1D("e_csi_1","e_csi_1",4096,0.5,4096.5);

e_histo->Add(h_e_csi[1]);

// position

// time

// scaler

TList *sc_histo= new TList();

Int_t sc_bins = 500;

TGraph *g_sc_si=new TGraph();

g_sc_si->SetNameTitle("g_sc_si", "rate Si OR");

sc_histo->Add(g_sc_si);

TGraph *g_sc_mwpc=new TGraph();

g_sc_mwpc->SetNameTitle("g_sc_mwpc", "rate MWPC anode");

sc_histo->Add(g_sc_mwpc);

TGraph *g_sc_target=new TGraph();

g_sc_target->SetNameTitle("g_sc_target", "target density");

sc_histo->Add(g_sc_target);

TGraph *g_sc_trafo=new TGraph();

g_sc_trafo->SetNameTitle("g_sc_trafo", "ESR ion current");

sc_histo->Add(g_sc_trafo);

TGraph *g_sc_inhibit=new TGraph();

g_sc_inhibit->SetNameTitle("g_sc_inhibit", "target inhibit");

sc_histo->Add(g_sc_inhibit);

TGraph *g_sc_clock=new TGraph();

g_sc_clock->SetNameTitle("g_sc_clock", "1.5 MHz clock");

sc_histo->Add(g_sc_clock);

ULong64_t sc_si_sum = 0;

ULong64_t sc_mwpc_sum = 0;

ULong64_t sc_clock_sum = 0;

ULong64_t sc_target_sum = 0;

ULong64_t sc_trafo_sum = 0;

ULong64_t sc_inhibit_sum = 0;

Int_t sc_interval = 1; //interval time [sec] for scaler plotting

Double_t clock_ref = 1.5e6; // clock reference rate = 1.5 MHz

Double_t t_diff = 0;

Double_t t_elapsed = 0;

// get number of events to process

Long64_t nentries = fChain->GetEntries();

Long64_t nbytes = 0, nb = 0;

//////////////////////

// EVENT LOOP START //

//////////////////////

for (Long64_t i=0; i<nentries;i++)

// for (Long64_t i=0; i<10000;i++)

{

nb = fChain->GetEntry(i); nbytes += nb;

// event countdown

if ((float(i)/100000.)==int(i/100000)){cout << "event: " << i << " \tof " << nentries << endl;}

//////////////////////

//scaler processing //

//////////////////////

sc_si_sum += sc_silicon_or;

sc_mwpc_sum += sc_mwpc_anode;

sc_clock_sum += sc_clock;

sc_target_sum += sc_target;

sc_trafo_sum += sc_trafo;

sc_inhibit_sum += sc_inhibit;

t_elapsed += (double)(sc_clock/clock_ref);

t_diff = (double)(sc_clock_sum/clock_ref);

// fill the scaler sums to histo for very interval

if( !((int)t_diff % sc_interval) && (int)t_diff > 0 )

//if( true )

{

if ( (int)t_diff <= 2*sc_interval ) //exclude large time intervals >> crap data

{

// cout << "time: " << t_elapsed << " trafo:" << sc_trafo_sum;

// cout << " diff: " << t_diff << " modulo: " << ((int)t_diff % sc_interval) << endl;

g_sc_si->SetPoint(g_sc_si->GetN() ,t_elapsed, sc_si_sum);

g_sc_mwpc->SetPoint(g_sc_mwpc->GetN() ,t_elapsed, sc_mwpc_sum);

g_sc_target->SetPoint(g_sc_target->GetN() ,t_elapsed, sc_target_sum);

g_sc_trafo->SetPoint(g_sc_trafo->GetN() ,t_elapsed, sc_trafo_sum);

g_sc_inhibit->SetPoint(g_sc_inhibit->GetN(),t_elapsed, sc_inhibit_sum);

g_sc_clock->SetPoint(g_sc_clock->GetN() ,t_elapsed, sc_clock_sum);

}

sc_si_sum = 0;

sc_mwpc_sum = 0;

sc_clock_sum = 0;

sc_target_sum = 0;

sc_trafo_sum = 0;

sc_inhibit_sum = 0;

}

////////////////////

// energy spectra //

////////////////////

if(TRIGGER==1)

{

for (int i=0;i<7;i++)

{

h_e_pad_1[i]->Fill(e_pad_1[i]);

h_e_pad_2[i]->Fill(e_pad_2[i]);

h_e_pad_3[i]->Fill(e_pad_3[i]);

h_e_pad_4[i]->Fill(e_pad_4[i]);

h_e_pad_5[i]->Fill(e_pad_5[i]);

h_e_pad_6[i]->Fill(e_pad_6[i]);

if ( i > 0 )

{

h_e_pad_n[i]->Fill(e_pad_n[i]);

if ( t_elapsed >= 30 && t_elapsed <= 100 ) h_e_pad_n_hi[i]->Fill(e_pad_n[i]);

if ( t_elapsed >= 250 && t_elapsed <= 350 ) h_e_pad_n_lo[i]->Fill(e_pad_n[i]);

}

}

}

}

////////////////////

// EVENT LOOP END //

////////////////////

// write output file

TFile *outfile = TFile::Open(OUTPUT, "RECREATE");

e_histo->Write("energy", TObject::kSingleKey);

sc_histo->Write("scaler", TObject::kSingleKey);

outfile->Close();

cout << "\033[0;32m" << OUTPUT << " is created!\033[0m" << endl;

// direct plotting (optional)

TCanvas *c_test = new TCanvas("test","test", 1000, 1200);

c_test->Divide(1,5);

c_test->cd(1);

g_sc_si->SetFillColor(15);

g_sc_si->Draw("AB");

c_test->cd(2);

g_sc_mwpc->SetFillColor(15);

g_sc_mwpc->Draw("AB");

c_test->cd(3);

g_sc_target->SetFillColor(15);

g_sc_target->Draw("AB");

c_test->cd(4);

g_sc_trafo->SetFillColor(15);

g_sc_trafo->Draw("AB");

c_test->cd(5);

... 108 more lines ...

|

| Attachment 2: e121_mapped.h

|

//////////////////////////////////////////////////////////

// This class has been automatically generated on

// Wed Nov 4 09:54:00 2020 by ROOT version 6.18/04

// from TTree h101/CWNtuple

// found on file: /data.local1/E121/root-files/part1/e121_run_0252.root

//////////////////////////////////////////////////////////

// Declaration of leaf types

// DAQ

UInt_t TRIGGER; //

UInt_t EVENTNO; //

UInt_t TB_SI_IN;

UInt_t TB_SI_RED;

UInt_t TB_MWPC_IN;

UInt_t TB_MWPC_RED;

// ADCs

UInt_t e_pad_1[7];

UInt_t e_pad_2[7];

UInt_t e_pad_3[7];

UInt_t e_pad_4[7];

UInt_t e_pad_5[7];

UInt_t e_pad_6[7];

UInt_t e_pad_n[7];

UInt_t e_dssd_top, e_dssd_bottom, e_dssd_left, e_dssd_right;

UInt_t e_csi[2];

//TDCs

UInt_t t_mwpc_x1, t_mwpc_x2, t_mwpc_y1, t_mwpc_y2, t_mwpc_anode, t_mwpc_raw;

UInt_t t_master_trig, t_trig_1, t_trig_2;

//Scalers

UInt_t sc_master_trig;

UInt_t sc_silicon_or;

UInt_t sc_mwpc_raw;

UInt_t sc_u_cool;

UInt_t sc_i_cool;

UInt_t sc_trafo;

UInt_t sc_inhibit;

UInt_t sc_mwpc_anode;

UInt_t sc_mwpc_x1;

UInt_t sc_mwpc_x2;

UInt_t sc_mwpc_y1;

UInt_t sc_mwpc_y2;

UInt_t sc_clock;

UInt_t sc_target;

UInt_t sc_trig_1;

UInt_t sc_trig_2;

// Set branch addresses

fChain->SetBranchAddress("TRIGGER", &TRIGGER);

fChain->SetBranchAddress("EVENTNO", &EVENTNO);

fChain->SetBranchAddress("ADC1_1", &e_pad_1[0]);

fChain->SetBranchAddress("ADC1_2", &e_pad_1[1]);

fChain->SetBranchAddress("ADC1_3", &e_pad_1[2]);

fChain->SetBranchAddress("ADC1_4", &e_pad_1[3]);

fChain->SetBranchAddress("ADC1_5", &e_pad_1[4]);

fChain->SetBranchAddress("ADC1_6", &e_pad_1[5]);

fChain->SetBranchAddress("ADC1_7", &e_pad_1[6]);

//fChain->SetBranchAddress("ADC1_8", &);

fChain->SetBranchAddress("ADC1_9", &e_pad_2[0]);

fChain->SetBranchAddress("ADC1_10", &e_pad_2[1]);

fChain->SetBranchAddress("ADC1_11", &e_pad_2[2]);

fChain->SetBranchAddress("ADC1_12", &e_pad_2[3]);

fChain->SetBranchAddress("ADC1_13", &e_pad_2[4]);

fChain->SetBranchAddress("ADC1_14", &e_pad_2[5]);

fChain->SetBranchAddress("ADC1_15", &e_pad_2[6]);

// fChain->SetBranchAddress("ADC1_16", &);

fChain->SetBranchAddress("ADC1_17", &e_pad_3[0]);

fChain->SetBranchAddress("ADC1_18", &e_pad_3[1]);

fChain->SetBranchAddress("ADC1_19", &e_pad_3[2]);

fChain->SetBranchAddress("ADC1_20", &e_pad_3[3]);

fChain->SetBranchAddress("ADC1_21", &e_pad_3[4]);

fChain->SetBranchAddress("ADC1_22", &e_pad_3[5]);

fChain->SetBranchAddress("ADC1_23", &e_pad_3[6]);

// fChain->SetBranchAddress("ADC1_24", &);

fChain->SetBranchAddress("ADC1_25", &e_pad_4[0]);

fChain->SetBranchAddress("ADC1_26", &e_pad_4[1]);

fChain->SetBranchAddress("ADC1_27", &e_pad_4[2]);

fChain->SetBranchAddress("ADC1_28", &e_pad_4[3]);

fChain->SetBranchAddress("ADC1_29", &e_pad_4[4]);

fChain->SetBranchAddress("ADC1_30", &e_pad_4[5]);

fChain->SetBranchAddress("ADC1_31", &e_pad_4[6]);

// fChain->SetBranchAddress("ADC1_32", &);

fChain->SetBranchAddress("ADC2_1", &e_pad_5[0]);

fChain->SetBranchAddress("ADC2_2", &e_pad_5[1]);

fChain->SetBranchAddress("ADC2_3", &e_pad_5[2]);

fChain->SetBranchAddress("ADC2_4", &e_pad_5[3]);

fChain->SetBranchAddress("ADC2_5", &e_pad_5[4]);

fChain->SetBranchAddress("ADC2_6", &e_pad_5[5]);

fChain->SetBranchAddress("ADC2_7", &e_pad_5[6]);

// fChain->SetBranchAddress("ADC2_8", &);

// fChain->SetBranchAddress("ADC2_9", &);

// fChain->SetBranchAddress("ADC2_10", &);

// fChain->SetBranchAddress("ADC2_11", &);

// fChain->SetBranchAddress("ADC2_12", &);

// fChain->SetBranchAddress("ADC2_13", &);

// fChain->SetBranchAddress("ADC2_14", &);

// fChain->SetBranchAddress("ADC2_15", &);

// fChain->SetBranchAddress("ADC2_16", &);

fChain->SetBranchAddress("ADC2_17", &e_pad_6[0]);

fChain->SetBranchAddress("ADC2_18", &e_pad_6[1]);

fChain->SetBranchAddress("ADC2_19", &e_pad_6[2]);

fChain->SetBranchAddress("ADC2_20", &e_pad_6[3]);

fChain->SetBranchAddress("ADC2_21", &e_pad_6[4]);

fChain->SetBranchAddress("ADC2_22", &e_pad_6[5]);

fChain->SetBranchAddress("ADC2_23", &e_pad_6[6]);

// fChain->SetBranchAddress("ADC2_24", &);

// fChain->SetBranchAddress("ADC2_25", &);

// fChain->SetBranchAddress("ADC2_26", &);

// fChain->SetBranchAddress("ADC2_27", &);

// fChain->SetBranchAddress("ADC2_28", &);

// fChain->SetBranchAddress("ADC2_29", &);

// fChain->SetBranchAddress("ADC2_30", &);

// fChain->SetBranchAddress("ADC2_31", &);

// fChain->SetBranchAddress("ADC2_32", &);

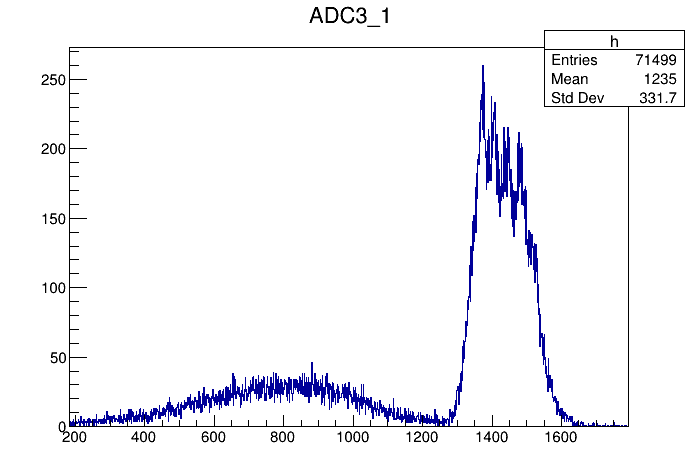

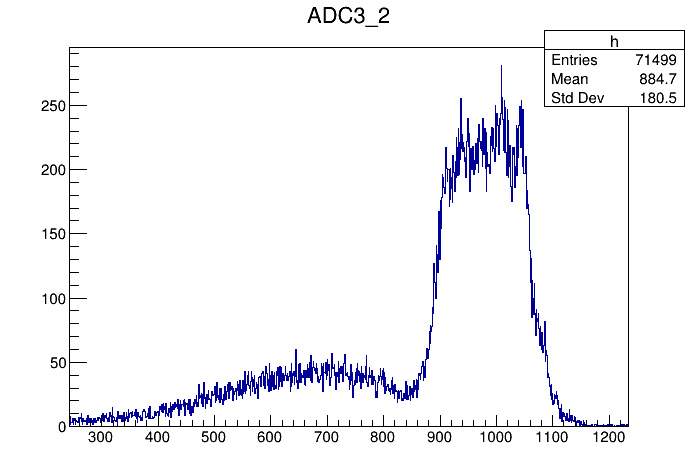

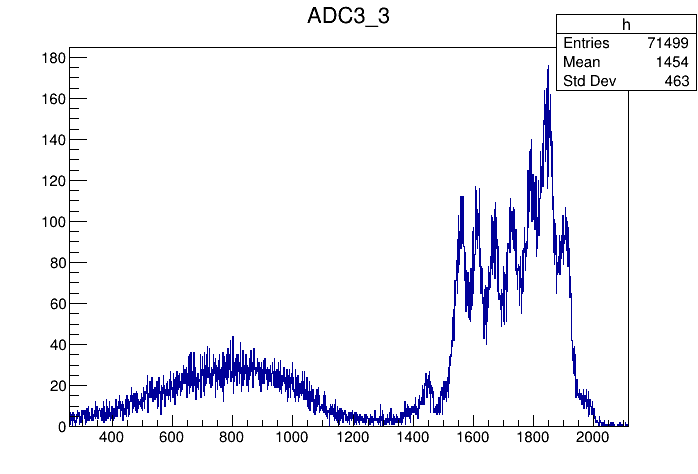

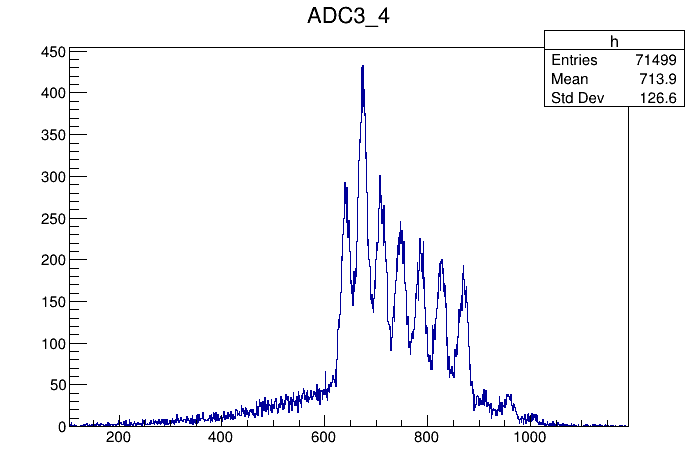

fChain->SetBranchAddress("ADC3_1", &e_dssd_left);

fChain->SetBranchAddress("ADC3_2", &e_dssd_right);

fChain->SetBranchAddress("ADC3_3", &e_dssd_top);

fChain->SetBranchAddress("ADC3_4", &e_dssd_bottom);

// fChain->SetBranchAddress("ADC3_5", &);

// fChain->SetBranchAddress("ADC3_6", &);

fChain->SetBranchAddress("ADC3_7", &e_csi[0]);

fChain->SetBranchAddress("ADC3_8", &e_csi[1]);

// fChain->SetBranchAddress("ADC3_9", &);

// fChain->SetBranchAddress("ADC3_10", &);

fChain->SetBranchAddress("ADC3_11", &e_pad_n[1]);

fChain->SetBranchAddress("ADC3_12", &e_pad_n[2]);

fChain->SetBranchAddress("ADC3_13", &e_pad_n[3]);

fChain->SetBranchAddress("ADC3_14", &e_pad_n[4]);

fChain->SetBranchAddress("ADC3_15", &e_pad_n[5]);

fChain->SetBranchAddress("ADC3_16", &e_pad_n[6]);

// fChain->SetBranchAddress("ADC3_17", &);

// fChain->SetBranchAddress("ADC3_18", &);

// fChain->SetBranchAddress("ADC3_19", &);

// fChain->SetBranchAddress("ADC3_20", &);

// fChain->SetBranchAddress("ADC3_21", &);

// fChain->SetBranchAddress("ADC3_22", &);

// fChain->SetBranchAddress("ADC3_23", &);

// fChain->SetBranchAddress("ADC3_24", &);

// fChain->SetBranchAddress("ADC3_25", &);

// fChain->SetBranchAddress("ADC3_26", &);

// fChain->SetBranchAddress("ADC3_27", &);

// fChain->SetBranchAddress("ADC3_28", &);

// fChain->SetBranchAddress("ADC3_29", &);

// fChain->SetBranchAddress("ADC3_30", &);

// fChain->SetBranchAddress("ADC3_31", &);

// fChain->SetBranchAddress("ADC3_32", &);

fChain->SetBranchAddress("SC1", &sc_master_trig);

fChain->SetBranchAddress("SC2", &sc_silicon_or);

fChain->SetBranchAddress("SC3", &sc_mwpc_raw);

fChain->SetBranchAddress("SC4", &sc_u_cool);

fChain->SetBranchAddress("SC5", &sc_i_cool);

fChain->SetBranchAddress("SC6", &sc_trafo);

fChain->SetBranchAddress("SC7", &sc_inhibit);

fChain->SetBranchAddress("SC8", &sc_mwpc_anode);

fChain->SetBranchAddress("SC9", &sc_mwpc_x1);

fChain->SetBranchAddress("SC10", &sc_mwpc_x2);

fChain->SetBranchAddress("SC11", &sc_mwpc_y1);

fChain->SetBranchAddress("SC12", &sc_mwpc_y2);

fChain->SetBranchAddress("SC13", &sc_clock);

fChain->SetBranchAddress("SC14", &sc_target);

fChain->SetBranchAddress("SC15", &sc_trig_1);

fChain->SetBranchAddress("SC16", &sc_trig_2);

// fChain->SetBranchAddress("SC17", &);

// fChain->SetBranchAddress("SC18", &);

// fChain->SetBranchAddress("SC19", &);

// fChain->SetBranchAddress("SC20", &);

// fChain->SetBranchAddress("SC21", &);

// fChain->SetBranchAddress("SC22", &);

// fChain->SetBranchAddress("SC23", &);

// fChain->SetBranchAddress("SC24", &);

// fChain->SetBranchAddress("SC25", &);

// fChain->SetBranchAddress("SC26", &);

// fChain->SetBranchAddress("SC27", &);

// fChain->SetBranchAddress("SC28", &);

// fChain->SetBranchAddress("SC29", &);

// fChain->SetBranchAddress("SC30", &);

// fChain->SetBranchAddress("SC31", &);

// fChain->SetBranchAddress("SC32", &);

fChain->SetBranchAddress("TDC1", &t_mwpc_anode);

fChain->SetBranchAddress("TDC2", &t_mwpc_x1);

fChain->SetBranchAddress("TDC3", &t_mwpc_x2);

fChain->SetBranchAddress("TDC4", &t_mwpc_y1);

fChain->SetBranchAddress("TDC5", &t_mwpc_y2);

fChain->SetBranchAddress("TDC6", &t_mwpc_raw);

// fChain->SetBranchAddress("TDC7", &t_);

fChain->SetBranchAddress("TDC8", &t_master_trig);

fChain->SetBranchAddress("TDC9", &t_trig_1);

fChain->SetBranchAddress("TDC10", &t_trig_2);

fChain->SetBranchAddress("TB_SI_IN", &TB_SI_IN);

fChain->SetBranchAddress("TB_SI_RED", &TB_SI_RED);

fChain->SetBranchAddress("TB_MWPC_IN", &TB_MWPC_IN);

fChain->SetBranchAddress("TB_MWPC_RED", &TB_MWPC_RED);

|

| Attachment 3: e121_raw.h

|

//////////////////////////////////////////////////////////

// This class has been automatically generated on

// Wed Nov 4 09:54:00 2020 by ROOT version 6.18/04

// from TTree h101/CWNtuple

// found on file: /data.local1/E121/root-files/part1/e121_run_0252.root

//////////////////////////////////////////////////////////

// Declaration of leaf types

UInt_t TRIGGER; //

UInt_t EVENTNO; //

UInt_t ADC1_1;

UInt_t ADC1_2;

UInt_t ADC1_3;

UInt_t ADC1_4;

UInt_t ADC1_5;

UInt_t ADC1_6;

UInt_t ADC1_7;

UInt_t ADC1_8;

UInt_t ADC1_9;

UInt_t ADC1_10;

UInt_t ADC1_11;

UInt_t ADC1_12;

UInt_t ADC1_13;

UInt_t ADC1_14;

UInt_t ADC1_15;

UInt_t ADC1_16;

UInt_t ADC1_17;

UInt_t ADC1_18;

UInt_t ADC1_19;

UInt_t ADC1_20;

UInt_t ADC1_21;

UInt_t ADC1_22;

UInt_t ADC1_23;

UInt_t ADC1_24;

UInt_t ADC1_25;

UInt_t ADC1_26;

UInt_t ADC1_27;

UInt_t ADC1_28;

UInt_t ADC1_29;

UInt_t ADC1_30;

UInt_t ADC1_31;

UInt_t ADC1_32;

UInt_t ADC2_1;

UInt_t ADC2_2;

UInt_t ADC2_3;

UInt_t ADC2_4;

UInt_t ADC2_5;

UInt_t ADC2_6;

UInt_t ADC2_7;

UInt_t ADC2_8;

UInt_t ADC2_9;

UInt_t ADC2_10;

UInt_t ADC2_11;

UInt_t ADC2_12;

UInt_t ADC2_13;

UInt_t ADC2_14;

UInt_t ADC2_15;

UInt_t ADC2_16;

UInt_t ADC2_17;

UInt_t ADC2_18;

UInt_t ADC2_19;

UInt_t ADC2_20;

UInt_t ADC2_21;

UInt_t ADC2_22;

UInt_t ADC2_23;

UInt_t ADC2_24;

UInt_t ADC2_25;

UInt_t ADC2_26;

UInt_t ADC2_27;

UInt_t ADC2_28;

UInt_t ADC2_29;

UInt_t ADC2_30;

UInt_t ADC2_31;

UInt_t ADC2_32;

UInt_t ADC3_1;

UInt_t ADC3_2;

UInt_t ADC3_3;

UInt_t ADC3_4;

UInt_t ADC3_5;

UInt_t ADC3_6;

UInt_t ADC3_7;

UInt_t ADC3_8;

UInt_t ADC3_9;

UInt_t ADC3_10;

UInt_t ADC3_11;

UInt_t ADC3_12;

UInt_t ADC3_13;

UInt_t ADC3_14;

UInt_t ADC3_15;

UInt_t ADC3_16;

UInt_t ADC3_17;

UInt_t ADC3_18;

UInt_t ADC3_19;

UInt_t ADC3_20;

UInt_t ADC3_21;

UInt_t ADC3_22;

UInt_t ADC3_23;

UInt_t ADC3_24;

UInt_t ADC3_25;

UInt_t ADC3_26;

UInt_t ADC3_27;

UInt_t ADC3_28;

UInt_t ADC3_29;

UInt_t ADC3_30;

UInt_t ADC3_31;

UInt_t ADC3_32;

UInt_t SC1;

UInt_t SC2;

UInt_t SC3;

UInt_t SC4;

UInt_t SC5;

UInt_t SC6;

UInt_t SC7;

UInt_t SC8;

UInt_t SC9;

UInt_t SC10;

UInt_t SC11;

UInt_t SC12;

UInt_t SC13;

UInt_t SC14;

UInt_t SC15;

UInt_t SC16;

UInt_t SC17;

UInt_t SC18;

UInt_t SC19;

UInt_t SC20;

UInt_t SC21;

UInt_t SC22;

UInt_t SC23;

UInt_t SC24;

UInt_t SC25;

UInt_t SC26;

UInt_t SC27;

UInt_t SC28;

UInt_t SC29;

UInt_t SC30;

UInt_t SC31;

UInt_t SC32;

UInt_t TDC1;

UInt_t TDC2;

UInt_t TDC3;

UInt_t TDC4;

UInt_t TDC5;

UInt_t TDC6;

UInt_t TDC7;

UInt_t TDC8;

UInt_t TDC9;

UInt_t TDC10;

UInt_t TB_SI_IN;

UInt_t TB_SI_RED;

UInt_t TB_MWPC_IN;

UInt_t TB_MWPC_RED;

// Set branch addresses

fChain->SetBranchAddress("TRIGGER", &TRIGGER );

fChain->SetBranchAddress("EVENTNO", &EVENTNO );

fChain->SetBranchAddress("ADC1_1", &ADC1_1 );

fChain->SetBranchAddress("ADC1_2", &ADC1_2 );

fChain->SetBranchAddress("ADC1_3", &ADC1_3 );

fChain->SetBranchAddress("ADC1_4", &ADC1_4 );

fChain->SetBranchAddress("ADC1_5", &ADC1_5 );

fChain->SetBranchAddress("ADC1_6", &ADC1_6 );

fChain->SetBranchAddress("ADC1_7", &ADC1_7 );

fChain->SetBranchAddress("ADC1_8", &ADC1_8 );

fChain->SetBranchAddress("ADC1_9", &ADC1_9 );

fChain->SetBranchAddress("ADC1_10", &ADC1_10 );

fChain->SetBranchAddress("ADC1_11", &ADC1_11 );

fChain->SetBranchAddress("ADC1_12", &ADC1_12 );

fChain->SetBranchAddress("ADC1_13", &ADC1_13 );

fChain->SetBranchAddress("ADC1_14", &ADC1_14 );

fChain->SetBranchAddress("ADC1_15", &ADC1_15 );

fChain->SetBranchAddress("ADC1_16", &ADC1_16 );

fChain->SetBranchAddress("ADC1_17", &ADC1_17 );

fChain->SetBranchAddress("ADC1_18", &ADC1_18 );

fChain->SetBranchAddress("ADC1_19", &ADC1_19 );

fChain->SetBranchAddress("ADC1_20", &ADC1_20 );

fChain->SetBranchAddress("ADC1_21", &ADC1_21 );

fChain->SetBranchAddress("ADC1_22", &ADC1_22 );

fChain->SetBranchAddress("ADC1_23", &ADC1_23 );

fChain->SetBranchAddress("ADC1_24", &ADC1_24 );

fChain->SetBranchAddress("ADC1_25", &ADC1_25 );

fChain->SetBranchAddress("ADC1_26", &ADC1_26 );

fChain->SetBranchAddress("ADC1_27", &ADC1_27 );

fChain->SetBranchAddress("ADC1_28", &ADC1_28 );

fChain->SetBranchAddress("ADC1_29", &ADC1_29 );

fChain->SetBranchAddress("ADC1_30", &ADC1_30 );

fChain->SetBranchAddress("ADC1_31", &ADC1_31 );

fChain->SetBranchAddress("ADC1_32", &ADC1_32 );

fChain->SetBranchAddress("ADC2_1", &ADC2_1 );

fChain->SetBranchAddress("ADC2_2", &ADC2_2 );

fChain->SetBranchAddress("ADC2_3", &ADC2_3 );

fChain->SetBranchAddress("ADC2_4", &ADC2_4 );

fChain->SetBranchAddress("ADC2_5", &ADC2_5 );

fChain->SetBranchAddress("ADC2_6", &ADC2_6 );

fChain->SetBranchAddress("ADC2_7", &ADC2_7 );

fChain->SetBranchAddress("ADC2_8", &ADC2_8 );

fChain->SetBranchAddress("ADC2_9", &ADC2_9 );

fChain->SetBranchAddress("ADC2_10", &ADC2_10 );

fChain->SetBranchAddress("ADC2_11", &ADC2_11 );

fChain->SetBranchAddress("ADC2_12", &ADC2_12 );

fChain->SetBranchAddress("ADC2_13", &ADC2_13 );

fChain->SetBranchAddress("ADC2_14", &ADC2_14 );

fChain->SetBranchAddress("ADC2_15", &ADC2_15 );

fChain->SetBranchAddress("ADC2_16", &ADC2_16 );

fChain->SetBranchAddress("ADC2_17", &ADC2_17 );

fChain->SetBranchAddress("ADC2_18", &ADC2_18 );

fChain->SetBranchAddress("ADC2_19", &ADC2_19 );

fChain->SetBranchAddress("ADC2_20", &ADC2_20 );

fChain->SetBranchAddress("ADC2_21", &ADC2_21 );

fChain->SetBranchAddress("ADC2_22", &ADC2_22 );

fChain->SetBranchAddress("ADC2_23", &ADC2_23 );

fChain->SetBranchAddress("ADC2_24", &ADC2_24 );

fChain->SetBranchAddress("ADC2_25", &ADC2_25 );

fChain->SetBranchAddress("ADC2_26", &ADC2_26 );

fChain->SetBranchAddress("ADC2_27", &ADC2_27 );

fChain->SetBranchAddress("ADC2_28", &ADC2_28 );

fChain->SetBranchAddress("ADC2_29", &ADC2_29 );

fChain->SetBranchAddress("ADC2_30", &ADC2_30 );

fChain->SetBranchAddress("ADC2_31", &ADC2_31 );

fChain->SetBranchAddress("ADC2_32", &ADC2_32 );

fChain->SetBranchAddress("ADC3_1", &ADC3_1 );

fChain->SetBranchAddress("ADC3_2", &ADC3_2 );

fChain->SetBranchAddress("ADC3_3", &ADC3_3 );

fChain->SetBranchAddress("ADC3_4", &ADC3_4 );

fChain->SetBranchAddress("ADC3_5", &ADC3_5 );

fChain->SetBranchAddress("ADC3_6", &ADC3_6 );

fChain->SetBranchAddress("ADC3_7", &ADC3_7 );

fChain->SetBranchAddress("ADC3_8", &ADC3_8 );

fChain->SetBranchAddress("ADC3_9", &ADC3_9 );

fChain->SetBranchAddress("ADC3_10", &ADC3_10 );

fChain->SetBranchAddress("ADC3_11", &ADC3_11 );

fChain->SetBranchAddress("ADC3_12", &ADC3_12 );

fChain->SetBranchAddress("ADC3_13", &ADC3_13 );

fChain->SetBranchAddress("ADC3_14", &ADC3_14 );

fChain->SetBranchAddress("ADC3_15", &ADC3_15 );

fChain->SetBranchAddress("ADC3_16", &ADC3_16 );

fChain->SetBranchAddress("ADC3_17", &ADC3_17 );

fChain->SetBranchAddress("ADC3_18", &ADC3_18 );

fChain->SetBranchAddress("ADC3_19", &ADC3_19 );

fChain->SetBranchAddress("ADC3_20", &ADC3_20 );

fChain->SetBranchAddress("ADC3_21", &ADC3_21 );

fChain->SetBranchAddress("ADC3_22", &ADC3_22 );

fChain->SetBranchAddress("ADC3_23", &ADC3_23 );

fChain->SetBranchAddress("ADC3_24", &ADC3_24 );

fChain->SetBranchAddress("ADC3_25", &ADC3_25 );

fChain->SetBranchAddress("ADC3_26", &ADC3_26 );

fChain->SetBranchAddress("ADC3_27", &ADC3_27 );

fChain->SetBranchAddress("ADC3_28", &ADC3_28 );

fChain->SetBranchAddress("ADC3_29", &ADC3_29 );

fChain->SetBranchAddress("ADC3_30", &ADC3_30 );

fChain->SetBranchAddress("ADC3_31", &ADC3_31 );

fChain->SetBranchAddress("ADC3_32", &ADC3_32 );

fChain->SetBranchAddress("SC1", &SC1 );

fChain->SetBranchAddress("SC2", &SC2 );

fChain->SetBranchAddress("SC3", &SC3 );

fChain->SetBranchAddress("SC4", &SC4 );

fChain->SetBranchAddress("SC5", &SC5 );

fChain->SetBranchAddress("SC6", &SC6 );

fChain->SetBranchAddress("SC7", &SC7 );

fChain->SetBranchAddress("SC8", &SC8 );

fChain->SetBranchAddress("SC9", &SC9 );

fChain->SetBranchAddress("SC10", &SC10 );

fChain->SetBranchAddress("SC11", &SC11 );

fChain->SetBranchAddress("SC12", &SC12 );

fChain->SetBranchAddress("SC13", &SC13 );

fChain->SetBranchAddress("SC14", &SC14 );

fChain->SetBranchAddress("SC15", &SC15 );

fChain->SetBranchAddress("SC16", &SC16 );

fChain->SetBranchAddress("SC17", &SC17 );

fChain->SetBranchAddress("SC18", &SC18 );

fChain->SetBranchAddress("SC19", &SC19 );

fChain->SetBranchAddress("SC20", &SC20 );

fChain->SetBranchAddress("SC21", &SC21 );

fChain->SetBranchAddress("SC22", &SC22 );

fChain->SetBranchAddress("SC23", &SC23 );

fChain->SetBranchAddress("SC24", &SC24 );

fChain->SetBranchAddress("SC25", &SC25 );

fChain->SetBranchAddress("SC26", &SC26 );

fChain->SetBranchAddress("SC27", &SC27 );

fChain->SetBranchAddress("SC28", &SC28 );

fChain->SetBranchAddress("SC29", &SC29 );

fChain->SetBranchAddress("SC30", &SC30 );

fChain->SetBranchAddress("SC31", &SC31 );

fChain->SetBranchAddress("SC32", &SC32 );

fChain->SetBranchAddress("TDC1", &TDC1 );

fChain->SetBranchAddress("TDC2", &TDC2 );

fChain->SetBranchAddress("TDC3", &TDC3 );

fChain->SetBranchAddress("TDC4", &TDC4 );

fChain->SetBranchAddress("TDC5", &TDC5 );

fChain->SetBranchAddress("TDC6", &TDC6 );

fChain->SetBranchAddress("TDC7", &TDC7 );

fChain->SetBranchAddress("TDC8", &TDC8 );

fChain->SetBranchAddress("TDC9", &TDC9 );

fChain->SetBranchAddress("TDC10", &TDC10 );

fChain->SetBranchAddress("TB_SI_IN", &TB_SI_IN);

fChain->SetBranchAddress("TB_SI_RED", &TB_SI_RED);

fChain->SetBranchAddress("TB_MWPC_IN", &TB_MWPC_IN);

fChain->SetBranchAddress("TB_MWPC_RED", &TB_MWPC_RED);

|

|

50

|

Sun Mar 29 13:04:32 2020 |

Ragan, RuiJiu | Runs | run file: 1298 | The Tl fragments are being stacked (almost ~20 staacks) and tried to store nicely in ESR.

The plan is to see the number of contaminants on the inner detector (CsISiPHOS) after the gas jet is on (Ar gas jet) and minimise this number for different FRS settings !!

P.S. Prayers have magical powers :) :) |

| Attachment 1: 61308F61-2C4C-4651-8C74-608E4E585B14.jpeg

|

|

| Attachment 2: EB5CA42A-B8DC-4892-8357-9006A1C3BAC0.jpeg

|

|

|

62

|

Sun Mar 29 23:48:12 2020 |

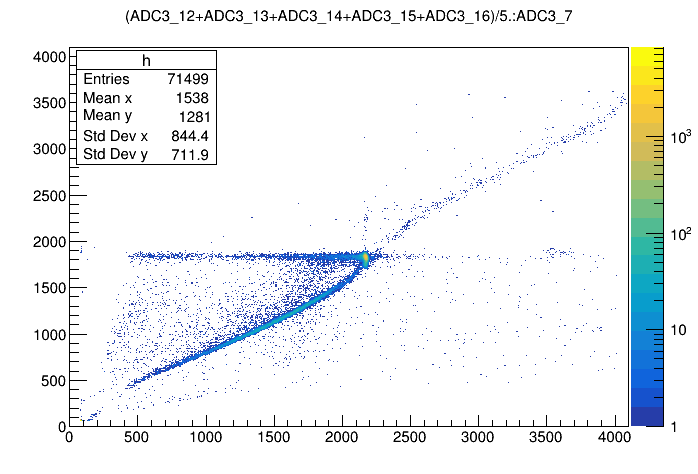

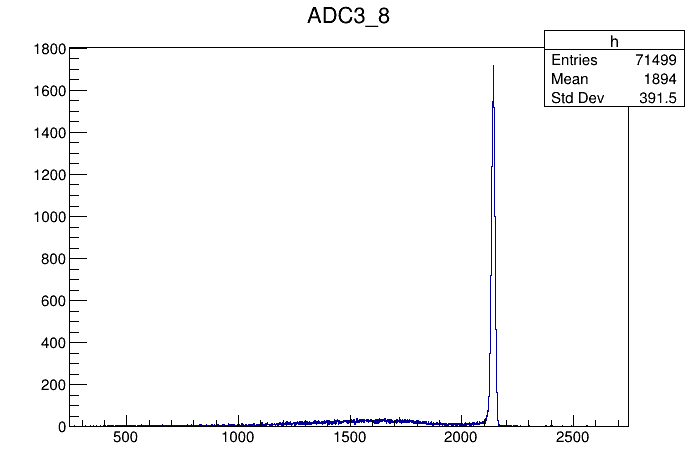

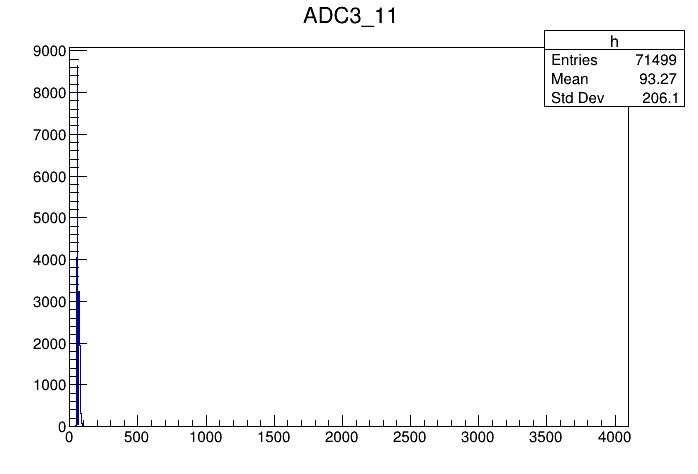

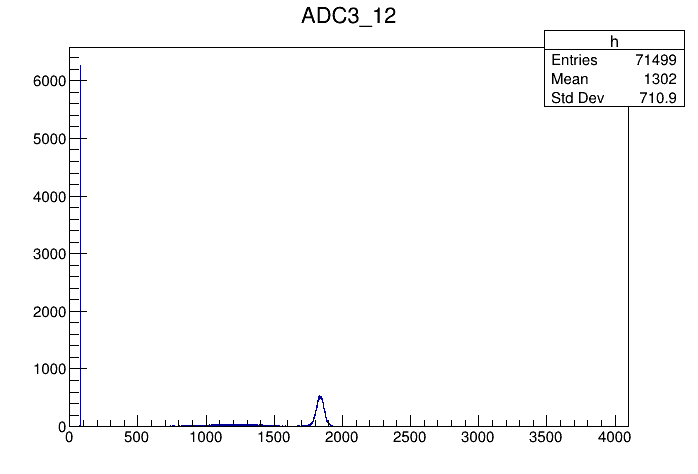

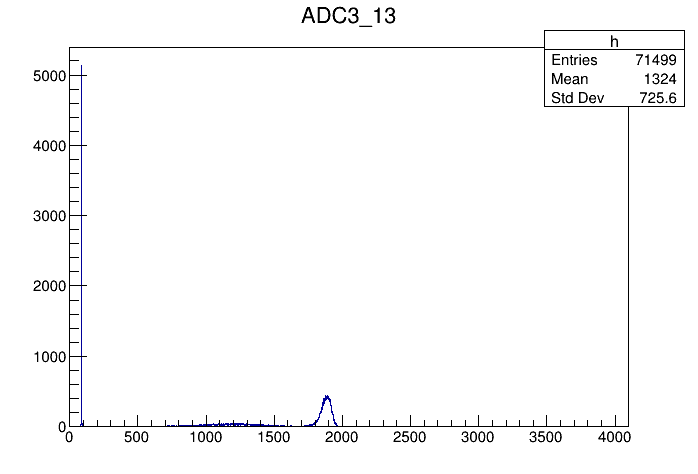

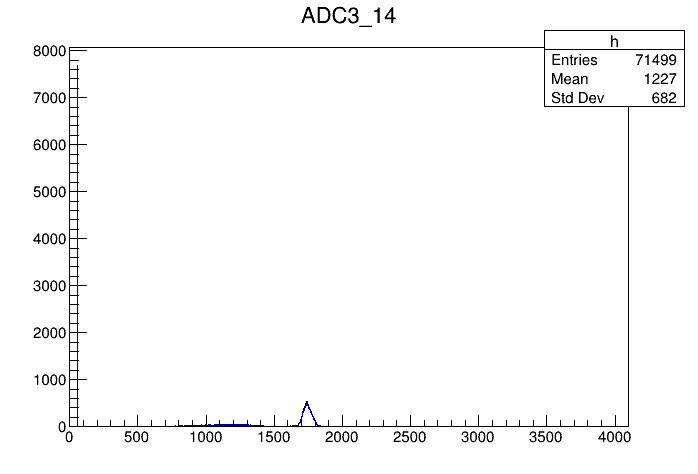

Jan | Analysis | run0251: E_spectra for CsISiPhos | This is a collection of energy spectra of the CsISiPhos detectors from run0251 with primary beam.

There is no good spectra for n-side of Si-pad 1! |

| Attachment 1: dE_vs_E.png

|

|

| Attachment 2: dE_vs_E_peak.png

|

|

| Attachment 3: E_dssd1.png

|

|

| Attachment 4: E_dssd2.png

|

|

| Attachment 5: E_dssd3.png

|

|

| Attachment 6: E_dssd4.png

|

|

| Attachment 7: E_CsI1.png

|

|

| Attachment 8: E_CsI2.png

|

|

| Attachment 9: E_pad1_n.png

|

|

| Attachment 10: E_pad2_n.png

|

|

| Attachment 11: E_pad3_n.png

|

|

| Attachment 12: E_pad4_n.png

|

|

| Attachment 13: E_pad5_n.png

|

|

| Attachment 14: E_pad6_n.png

|

|

|

104

|

Mon Mar 30 23:30:35 2020 |

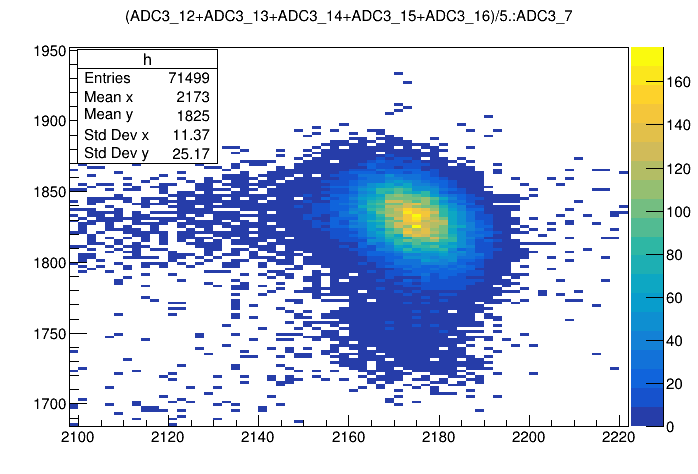

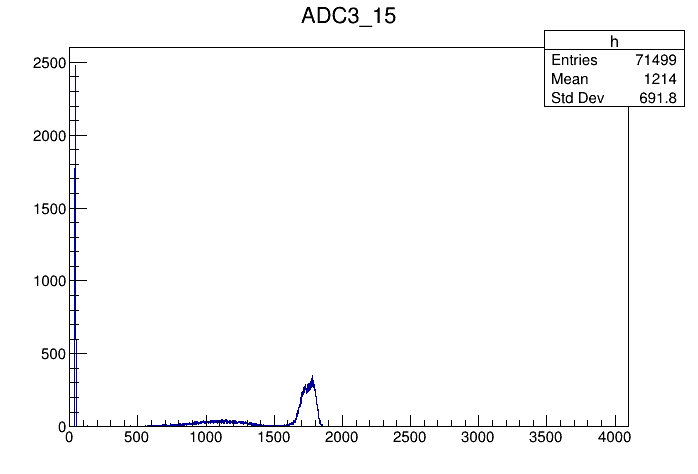

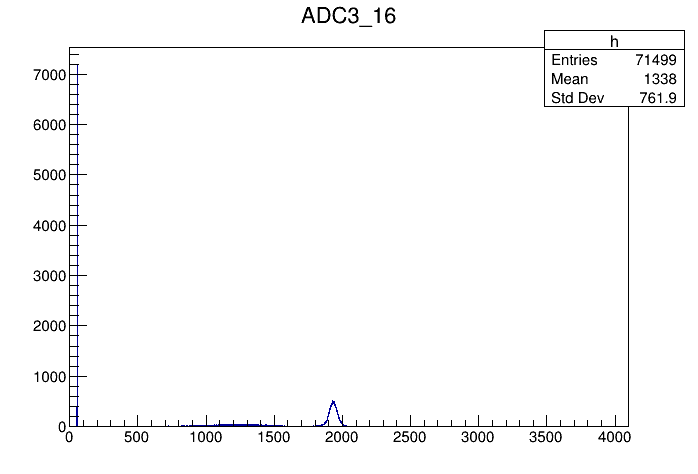

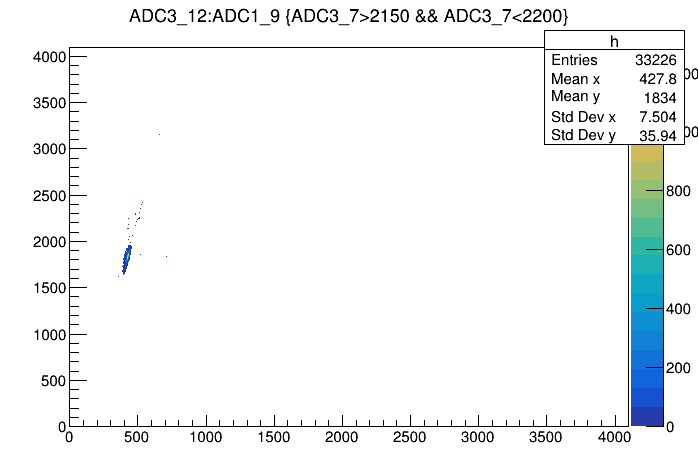

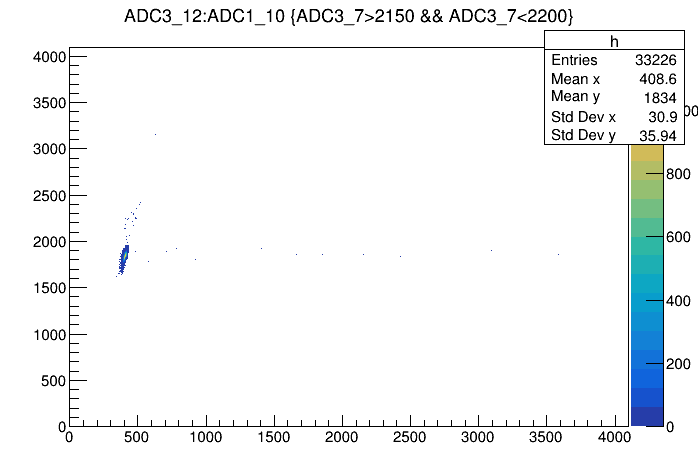

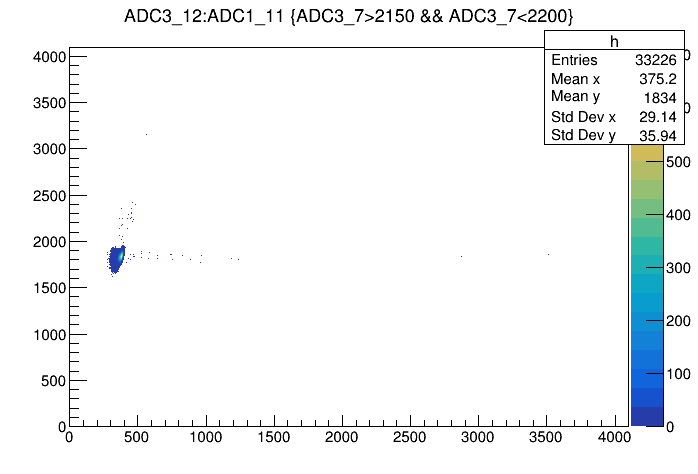

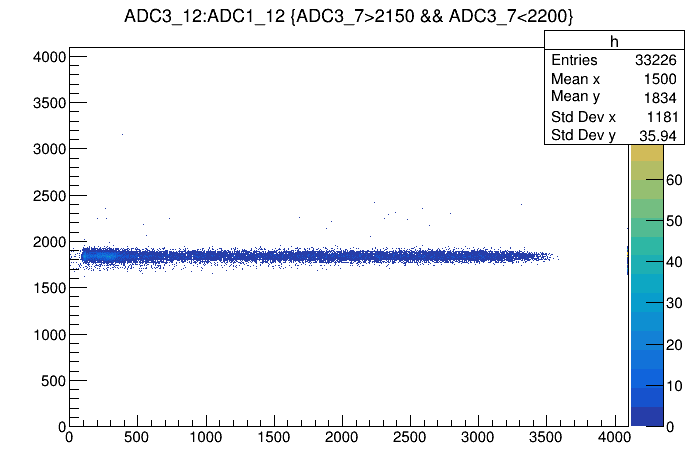

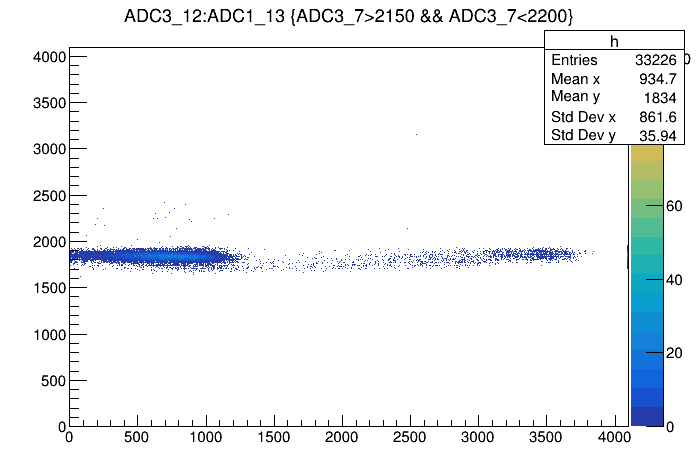

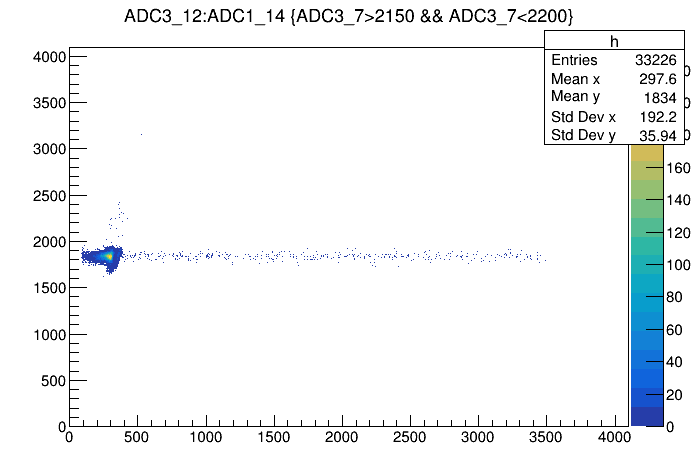

Jan | Analysis | run251 - Si-pad performance & status | Attached are plots for Si-pad 2 with hits from ionization of 206Pb81+ at the target.

The plots are representative for all Si-pads, the pattern is always the same!

y-axis: E n-side

x-axis: E p-side strip

condition: E_gate on peak in CsI

While strips 1, 2 and 7 look fine, strips 3 and 6 show already signs of degradation.

For strips 4 and 5, it is clearly visible that something is wrong.

Those are the central strips, which probably see the most rate.

The same dataset was analyzed here: https://elog.gsi.de/esr/E121/62

This might be a hint to a radiation damage or to the fact that we operate at too low bias voltage (32 Volt).

Maybe it recovers if we increase bias to 60 Volt. |

| Attachment 1: 251_Epad2_n_vs_p1.png

|

|

| Attachment 2: 251_Epad2_n_vs_p2.png

|

|

| Attachment 3: 251_Epad2_n_vs_p3.png

|

|

| Attachment 4: 251_Epad2_n_vs_p4.png

|

|

| Attachment 5: 251_Epad2_n_vs_p5.png

|

|

| Attachment 6: 251_Epad2_n_vs_p6.png

|

|

| Attachment 7: 251_Epad2_n_vs_p7.png

|

|

|

120

|

Thu Apr 2 12:52:25 2020 |

ruijiu | General | setup FRS with 2 g/cm2 degrader. | Yuri sets up FRS with 2 g/cm2 degrader (previous one is 1 g/cm2). The ESR is not changed. The contamination should be less now. |

|

3

|

Wed Dec 5 17:29:24 2018 |

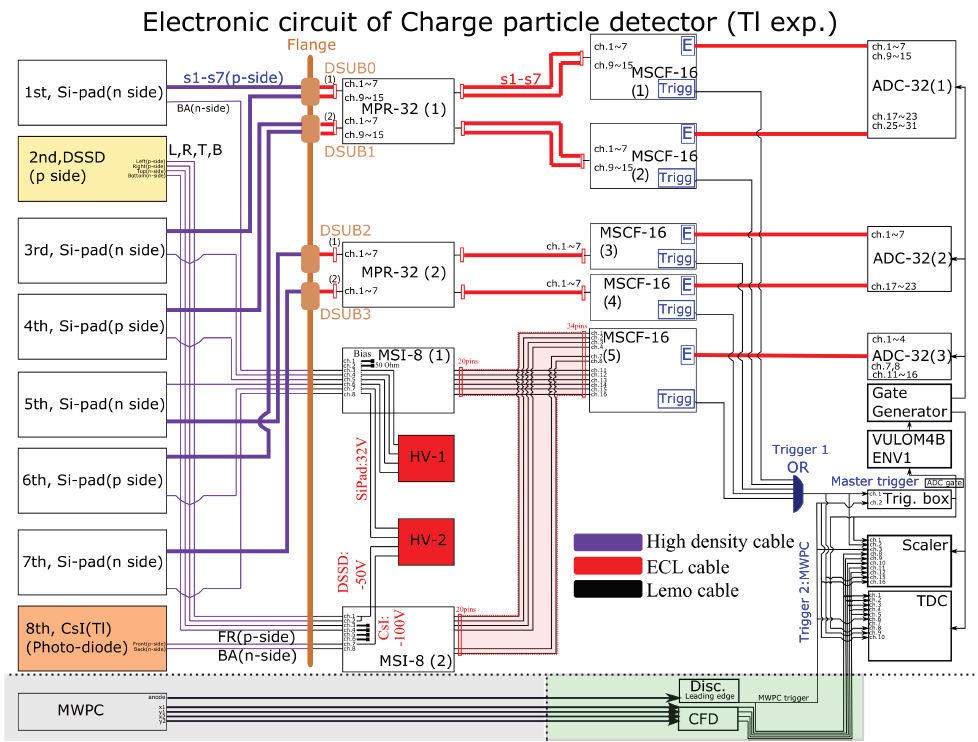

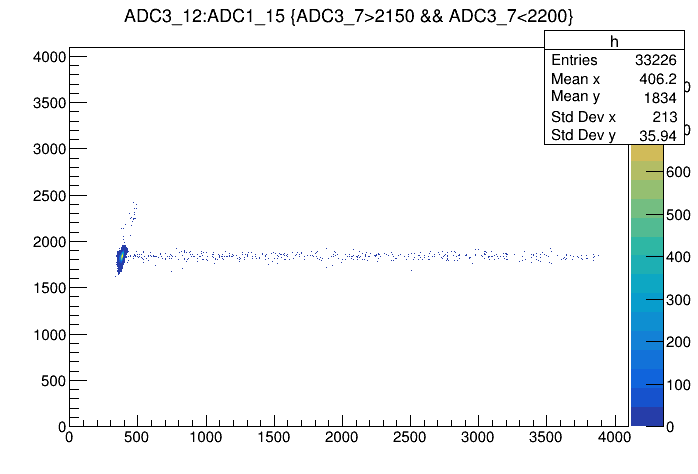

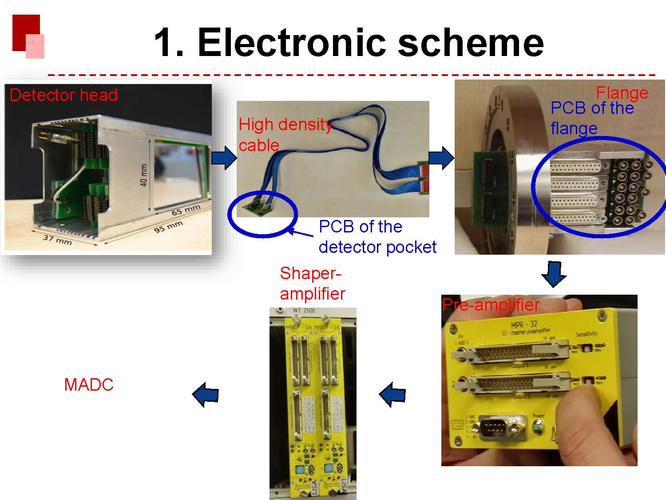

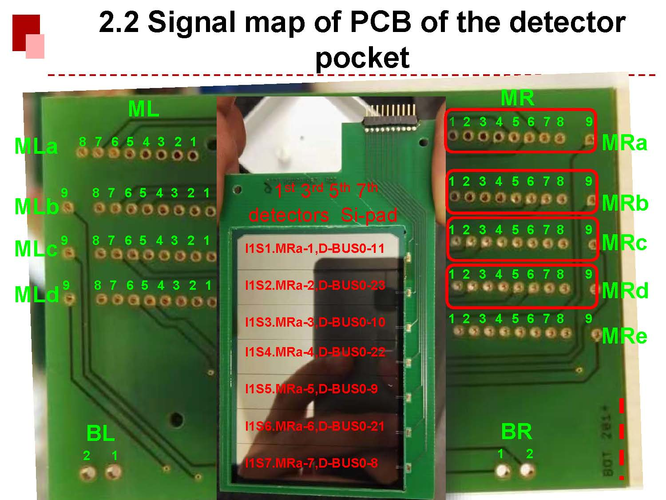

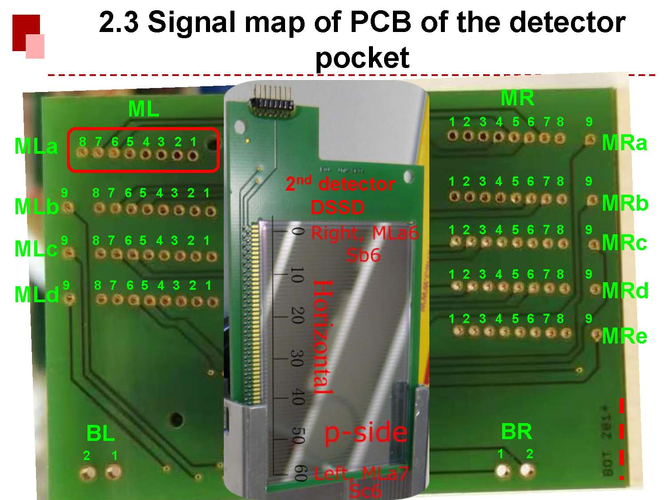

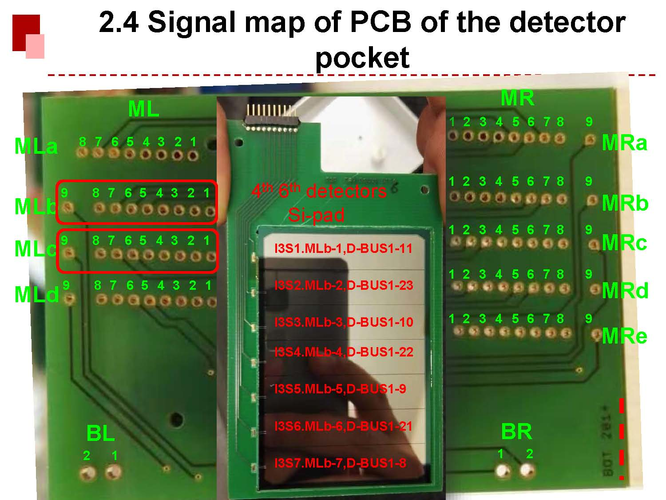

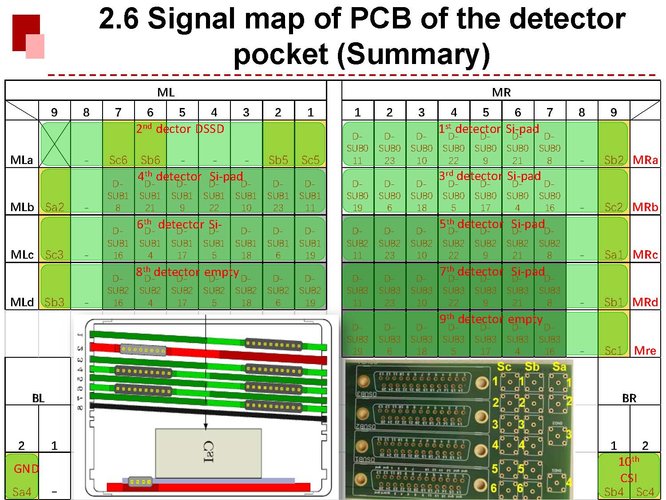

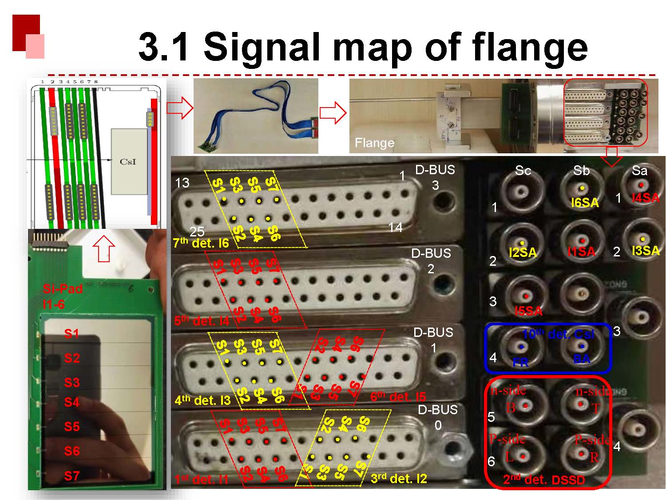

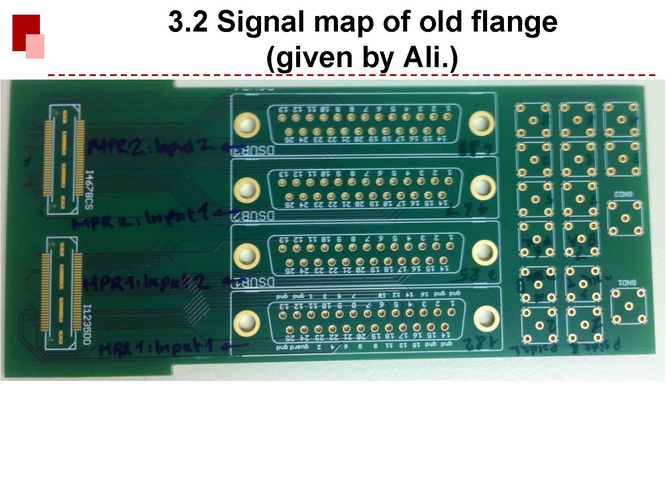

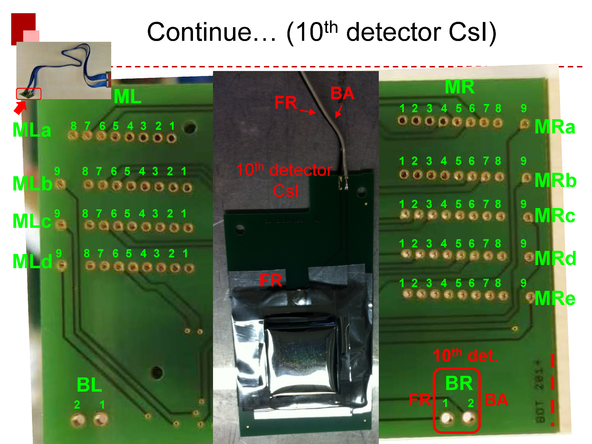

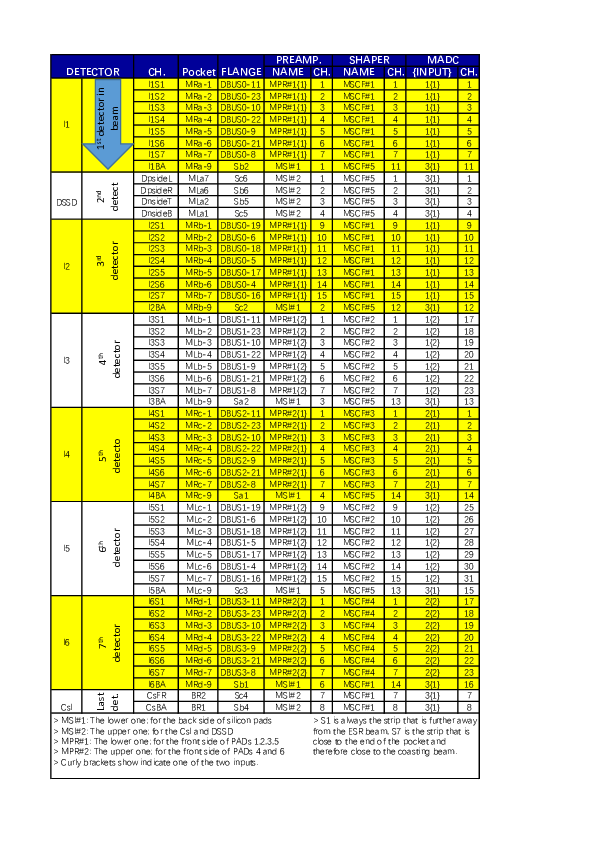

Chen, Sidhu | Detectors | signal map | Description:

Here is a summary of signal map. The charged particle detector includes 6 layers of Si-Pad, 1 DSSD and 1 CsI.

All these detectors are installed inside the detector pocket. All signals are connected to one PCB which is attached on the pocket, then are connected

to the PCB of the flange by high density cable. This document descripts the signal map on the PCB of the detector

pocket and flange.

The signal maps of the PCB of the detector pocket are shown as follow:

|

|

51

|

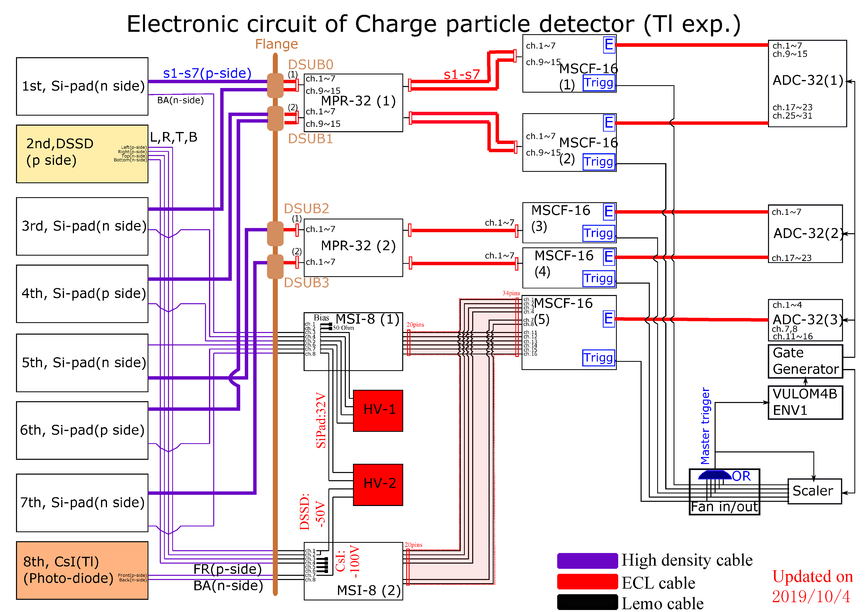

Sun Mar 29 13:05:36 2020 |

ruijiu | DAQ | start ntcap | IQ_2020-03-29_13-05-

56

SC_2020-03-29_13-05-

56 |

| Attachment 1: IMG_20200329_130438.jpg

|

|

|

37

|

Sat Mar 28 15:07:40 2020 |

ruijiu | DAQ | start run | |

|

38

|

Sat Mar 28 15:19:23 2020 |

ruijiu | | start run e121_run_0236.lmd | store 206Pb81+ beam inside ESR and measure its halflife.

The HV of detector is off.

Start DAQ to record the ESR current in lmd file.

Nik is optimizing the gas jet target. So this file is still test run. |

|

46

|

Sun Mar 29 10:09:14 2020 |

ruijiu | | start run e121_run_0237.lmd | Sergey and Yuri are tuning Tl beam. The particle number in ers is about 1e4. I(SIS)=5e8

run stop: after few minutes (garbage data) |

|

48

|

Sun Mar 29 11:12:00 2020 |

Ragan | Runs | start run e121_run_0239.lmd | Sergey and Yuri are tuning Tl beam. The particle number in ers is about 1e4. I(SIS)=5e8

some events on MWPC can be seen ! |

|

98

|

Mon Mar 30 14:24:46 2020 |

ruijiu | DAQ | stop taking data. | 1. stop run0272.lmd.

2. stop NTCAP.

NTCAp file:

SC_2020-03-30_09-28-14

IQ_2020-03-30_09-28-14

(saved in drive: p) |

|

45

|

Sun Mar 29 09:57:26 2020 |

ruijiu | Detectors | the HV of charged particle detector | MHV1 MHV2

ch1:1st Sipad 4th

Sipad

ch2:2nd Sipad 6th

Sipad

ch3:3rd Sipad DSSD

ch4:4th Sipad CsI |

| Attachment 1: IMG_20200329_095014.jpg

|

|

|

111

|

Wed Apr 1 01:02:24 2020 |

ruijiu | Detectors | the detector cable is disconnected. | |

|

100

|

Mon Mar 30 15:03:58 2020 |

ruijiu Tino, Yuri, Lasoro, Nik and Uli | Detectors | the gas bottle is empty. | The gas bottle was empty. Tino replaced

the previous old bottle with 50 bar gas left.

Yuri is getting new gas bottles.

Yuri got a new gas bottle. We repalced

the the new gas bottle. There is 200

bar gas left now.

The old gas bottle with 50 bar gas

left was kept inside ESR.

The empty gas bottle was removed from

ESR.

The outlet volve was decreased by 30 degree.

Since the value is almost 0, we can not read the value of outlet volve. |

| Attachment 1: IMG_20200330_152735_mh1585575780057.jpg

|

|

|

101

|

Mon Mar 30 16:25:05 2020 |

ruijiu | Detectors | turn down the HV | turn down the hv and pull out the detector.

suggest by

Hi everybody,

is there now much more rate on the detectors?

Perhaps it helps to turn down the bias for a while and to take the detectors out of the beam, by pulling the pocket out?

And then see if the leakage current comes down again.

good luck, Thomas

***********************************************

Dr. Thomas Faestermann | Tel: +49-89-2723868

Physik Department E12 |

Techn. Univ. Muenchen | Mob: +49-1626193388 |

|

10

|

Wed Jun 26 16:20:31 2019 |

Jan | DAQ | unpacker: lmd > root | I have written an unpacker for the lmd data taken with the current daq-system for E121.

The crate configuration is as follows:

ADC1 channels 1-32 (Caen 785)

ADC2 channels 1-32 (Caen 785)

ADC3 channels 1-32 (Caen 785)

SCALER channels 1-32 (Caen 830)

The unpacker binary can be found here

/u/litv-exp/unpacker/unpackexps/E121/E121

The current spec file is attached.

To convert lmd-files to root-files, please use it as follows:litv-exp@lxg___: E121_unpacker /path/to/file.lmd --ntuple=RAW,/path/to/new_file.root |

| Attachment 1: E121.spec

|

// -*- C++ -*-

ADC(start)

{

MEMBER(DATA12 data[32]);

list(0 <= ch < 32)

{

UINT32 item NOENCODE

{

0_15: channel;

16_27: value;

28_31: 0;

ENCODE(data[channel - start], (value=value));

}

}

}

SCALER(start)

{

MEMBER(DATA32 data[32]);

list(0 <= ch < 32)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel / 2) - start], (value=(high.value << 16) | low.value));

}

}

SUBEVENT(ESR)

{

adc[0] = ADC(start = 0);

adc[1] = ADC(start = 32);

adc[2] = ADC(start = 64);

select optional {

scaler[0] = SCALER(start = 0x100);

}

}

EVENT

{

esr = ESR(type = 10, subtype = 1);

}

#include "det_mapping.hh"

|

| Attachment 2: det_mapping.hh

|

SIGNAL( ADC1_1, esr.adc[0].data[0],

ADC1_32, esr.adc[0].data[31], DATA12);

SIGNAL( ADC2_1, esr.adc[1].data[0],

ADC2_32, esr.adc[1].data[31], DATA12);

SIGNAL( ADC3_1, esr.adc[2].data[0],

ADC3_32, esr.adc[2].data[31], DATA12);

//SIGNAL( SC_1, esr.scaler[0].data[0],

// SC_32, esr.scaler[0].data[31],DATA32);

|

|