| ID |

Date |

Author |

Category |

Subject |

|

38

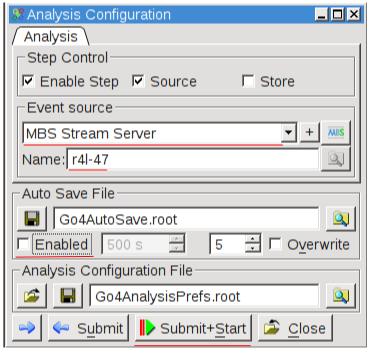

|

Sat Mar 28 15:19:23 2020 |

ruijiu | | start run e121_run_0236.lmd | store 206Pb81+ beam inside ESR and measure its halflife.

The HV of detector is off.

Start DAQ to record the ESR current in lmd file.

Nik is optimizing the gas jet target. So this file is still test run. |

|

46

|

Sun Mar 29 10:09:14 2020 |

ruijiu | | start run e121_run_0237.lmd | Sergey and Yuri are tuning Tl beam. The particle number in ers is about 1e4. I(SIS)=5e8

run stop: after few minutes (garbage data) |

|

52

|

Sun Mar 29 13:43:46 2020 |

| | | |

| Attachment 1: 5765BDDD-C10A-44AD-AF85-07134B06F34E.jpeg

|

|

|

53

|

Sun Mar 29 14:01:45 2020 |

ruijiu | | beam position on DSSD | move the detector 1cm

outside.from 60mm to

70mm.

left direction is

outside. right direction

is

inside(close to beam).

the spot is moving from

left to right. |

| Attachment 1: IMG_20200329_140003.jpg

|

|

|

54

|

Sun Mar 29 14:29:13 2020 |

ruijiu | | e121_run_00240.lmd | s6 positon at 50mm. |

|

171

|

Thu Apr 9 11:47:28 2020 |

ruijiu | | backup data | 2020.4.8 12:00Started copying

data。

2020.4.9 11:52 Copied 6.3TB

data. The copy speed is 65-67MB/s.

2020.4.15 Bring the two USB hard disk to my office and connect them to lxg1298 computer.

Send email |

| Attachment 1: IMG_20200409_113155.jpg

|

|

|

55

|

Sun Mar 29 18:41:31 2020 |

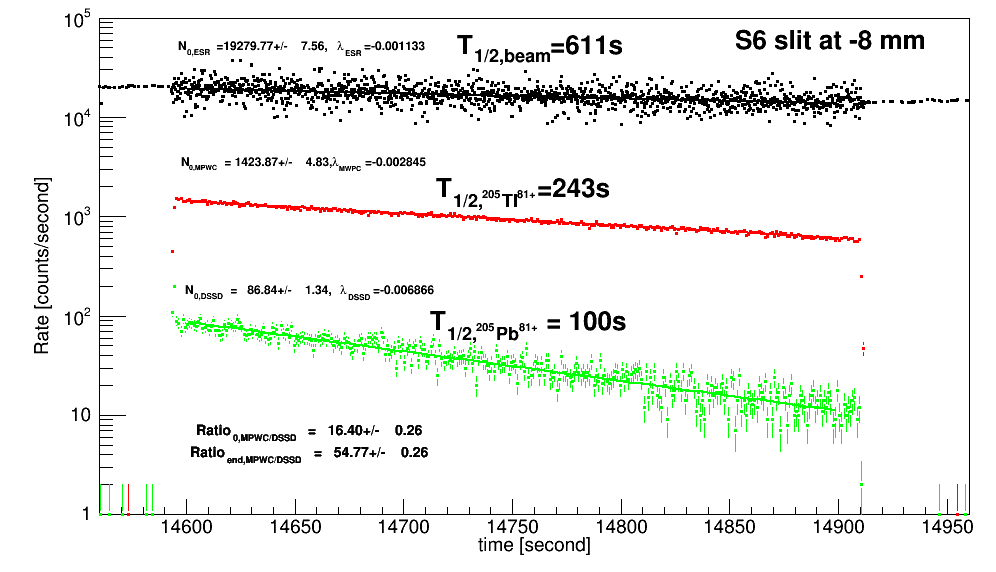

ruijiu | Analysis | Ratio between MPWC rate and DSSD rate | slit Ratio error

-1 18.64 0.4

-2 18.18 0.38

-3 20.85 0.5

-4 18.15 0.34

-5 17.44 0.31

-6 17.38 0.32

-7 17.82 0.32

-8 16.41 0.27

-9 18.51 0.37 |

| Attachment 1: ratio.png

|

|

|

58

|

Sun Mar 29 21:02:43 2020 |

ruijiu | Analysis | decay line of 205Tl beam | decay line of 205Tl beam with Ar gas jet target on and S6 slit at -8mm

Ar gas density~1e12 atoms/cm2 |

| Attachment 1: main_s6_neg8_202003292059.png

|

|

| Attachment 2: main_s6_neg8_202003292059.root

|

|

60

|

Sun Mar 29 21:39:27 2020 |

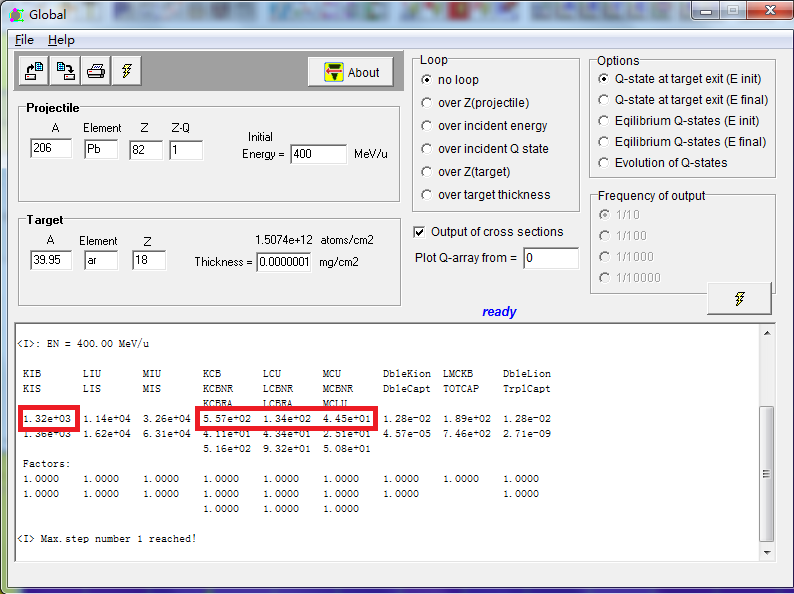

ruijiu | Analysis | Ionization cross section and capture cross section for h-206Pb + Ar | Ionization cross section = 1320 barn.

Capture cross section = 557+137+44.5=735.5.

sigma_Ion/sigma_cap=1.79 |

| Attachment 1: 202003292141.png

|

|

|

62

|

Sun Mar 29 23:48:12 2020 |

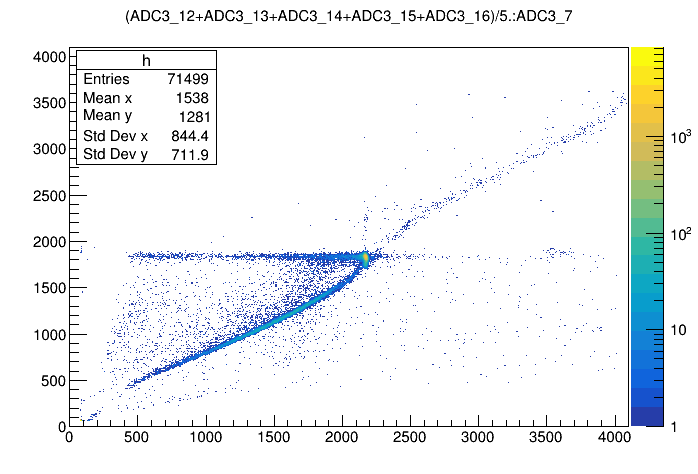

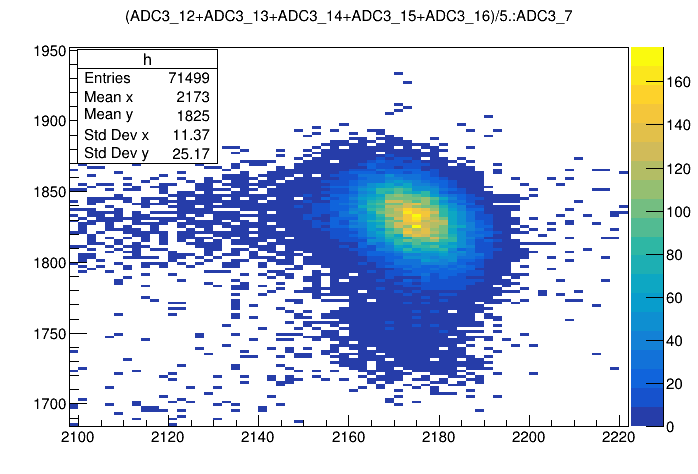

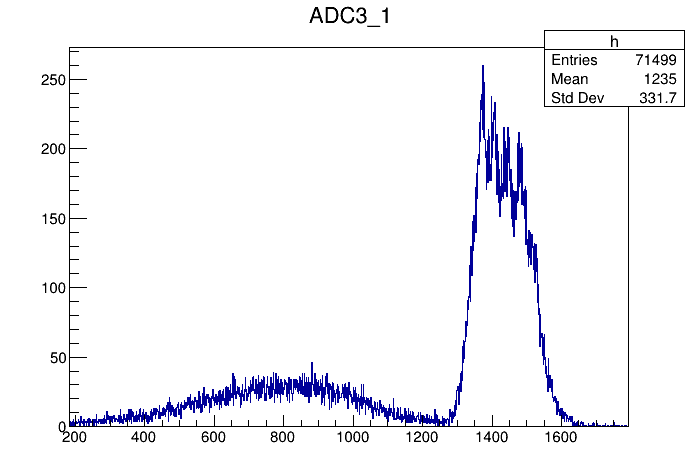

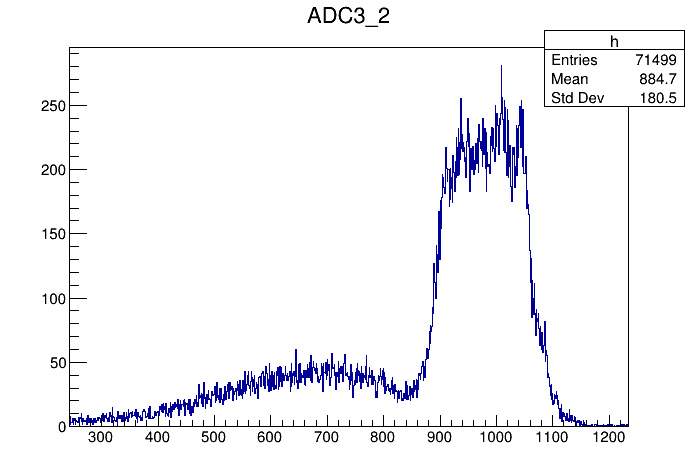

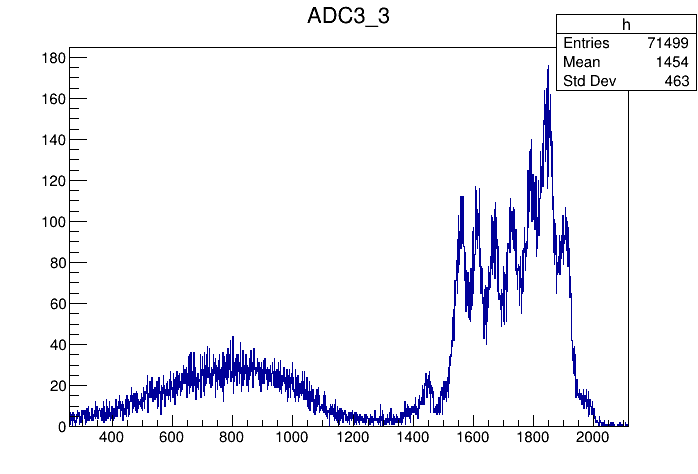

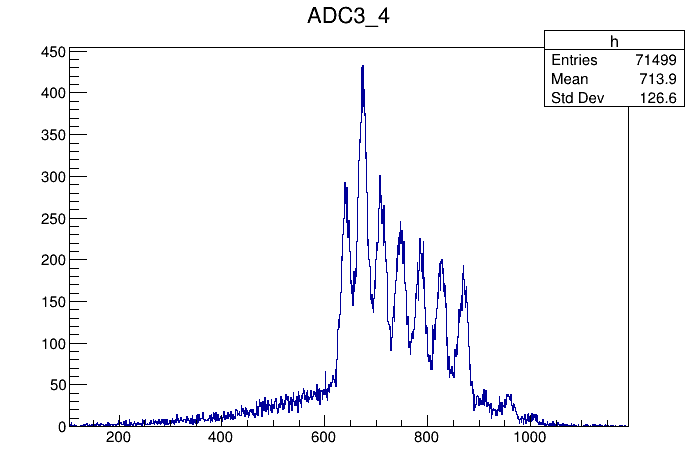

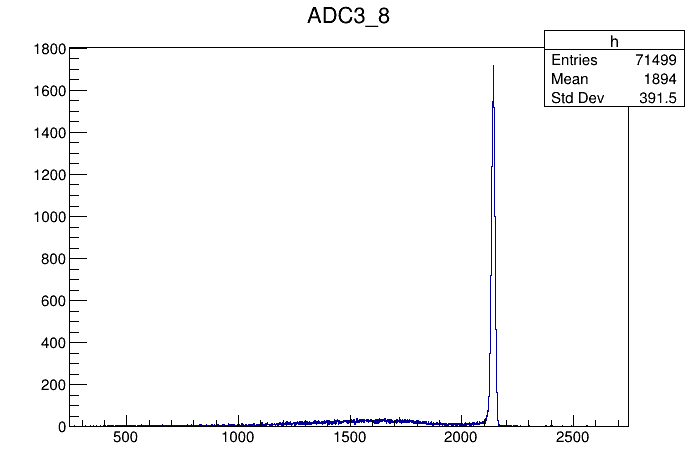

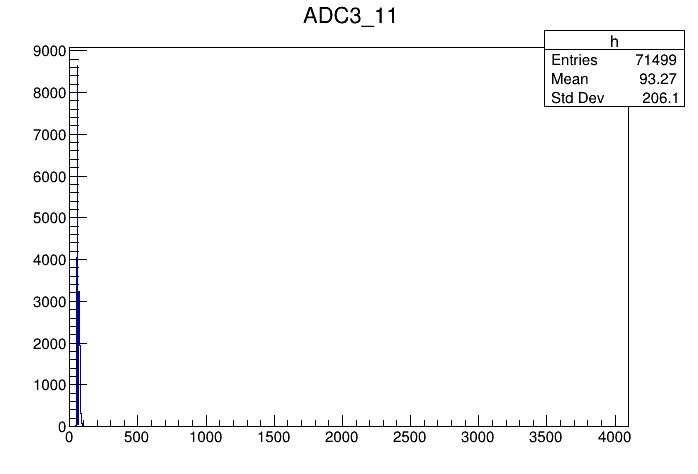

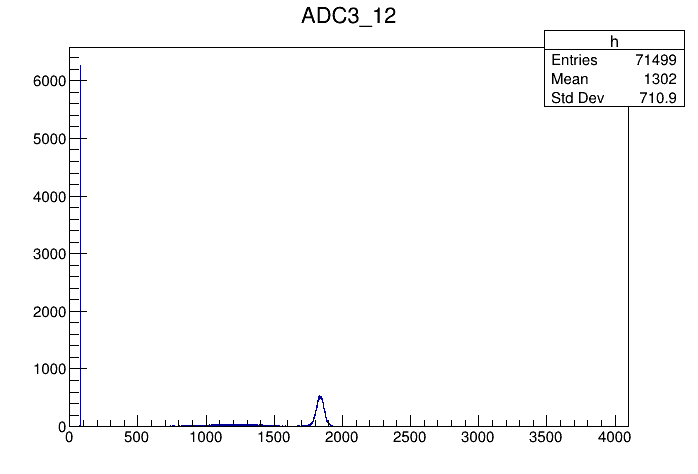

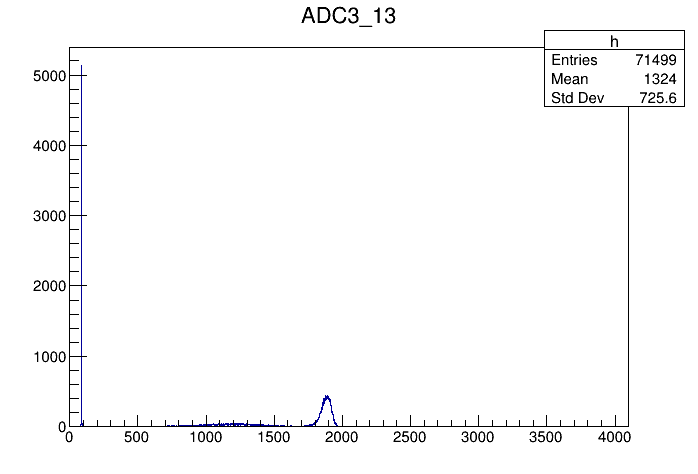

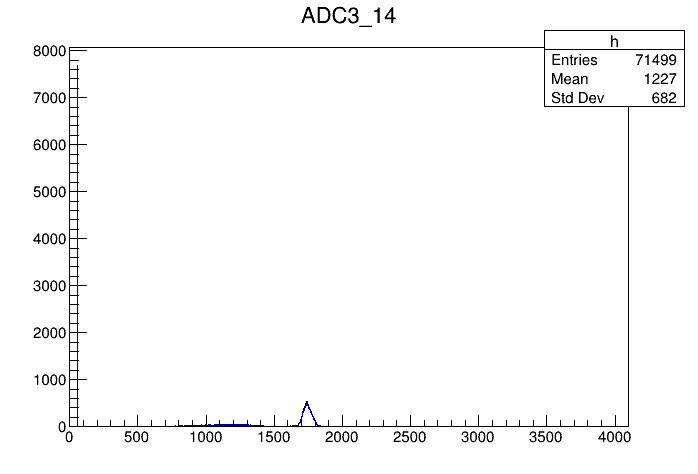

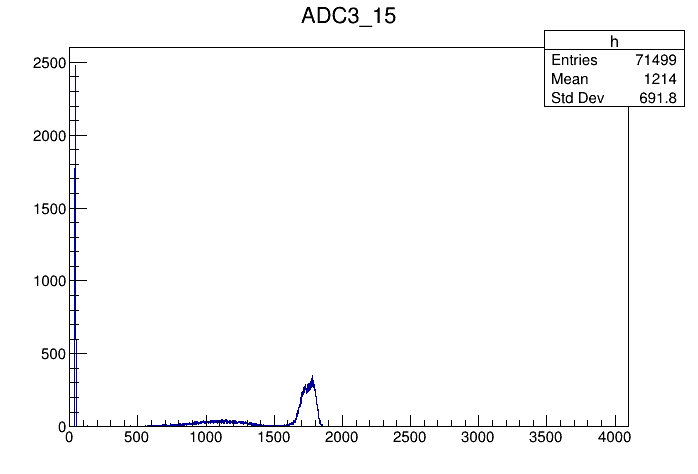

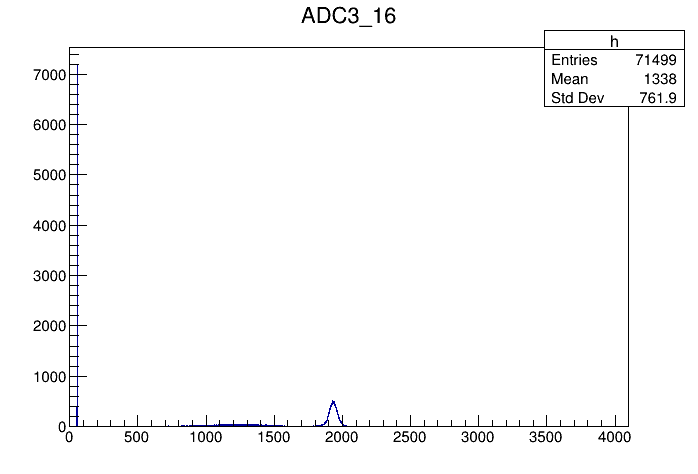

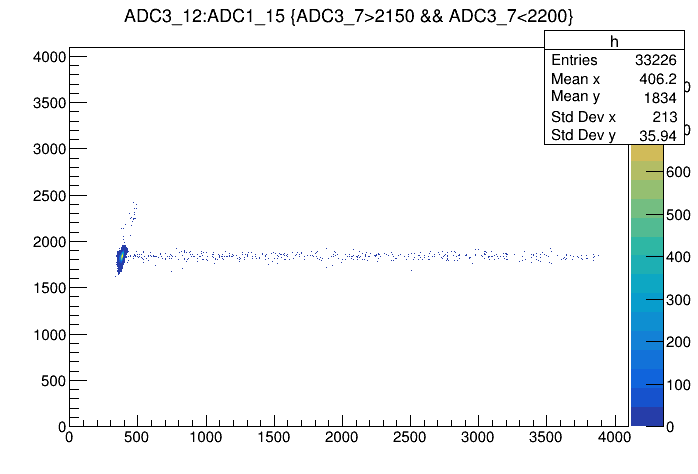

Jan | Analysis | run0251: E_spectra for CsISiPhos | This is a collection of energy spectra of the CsISiPhos detectors from run0251 with primary beam.

There is no good spectra for n-side of Si-pad 1! |

| Attachment 1: dE_vs_E.png

|

|

| Attachment 2: dE_vs_E_peak.png

|

|

| Attachment 3: E_dssd1.png

|

|

| Attachment 4: E_dssd2.png

|

|

| Attachment 5: E_dssd3.png

|

|

| Attachment 6: E_dssd4.png

|

|

| Attachment 7: E_CsI1.png

|

|

| Attachment 8: E_CsI2.png

|

|

| Attachment 9: E_pad1_n.png

|

|

| Attachment 10: E_pad2_n.png

|

|

| Attachment 11: E_pad3_n.png

|

|

| Attachment 12: E_pad4_n.png

|

|

| Attachment 13: E_pad5_n.png

|

|

| Attachment 14: E_pad6_n.png

|

|

|

102

|

Mon Mar 30 16:37:53 2020 |

ruijiu | Analysis | | |

|

104

|

Mon Mar 30 23:30:35 2020 |

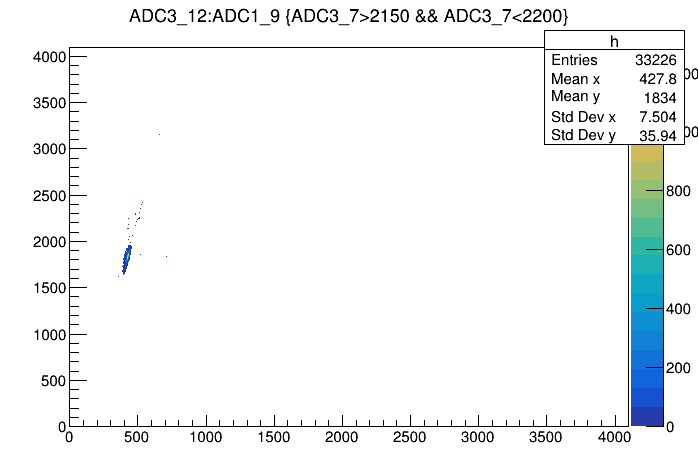

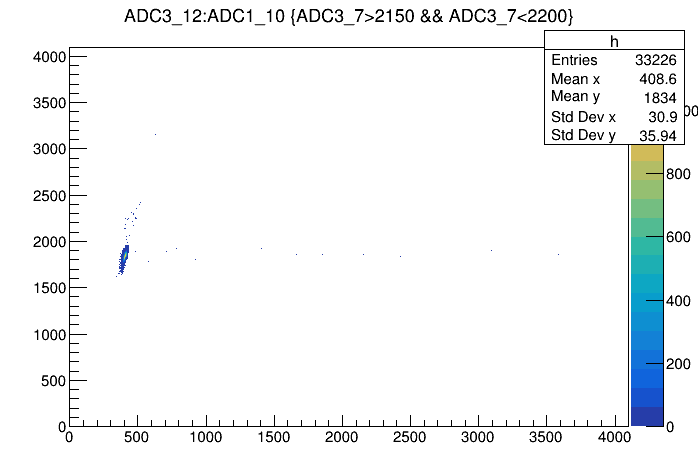

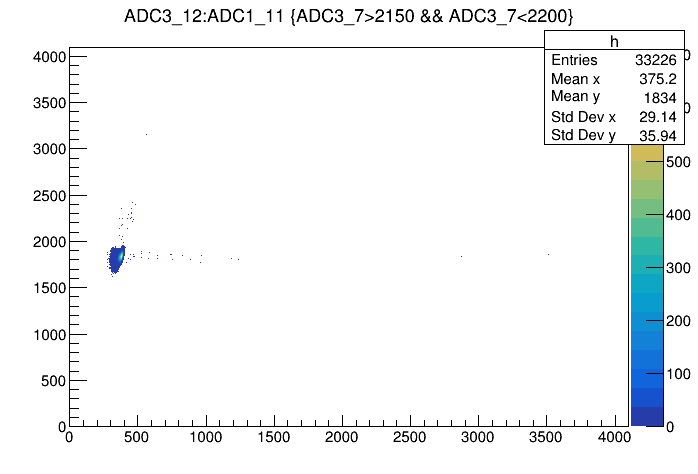

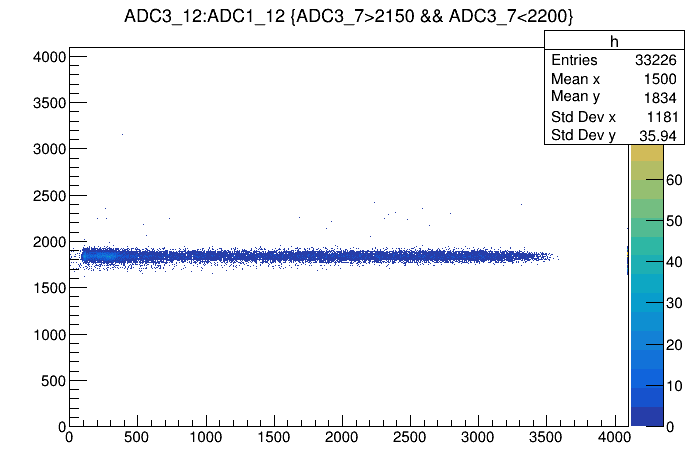

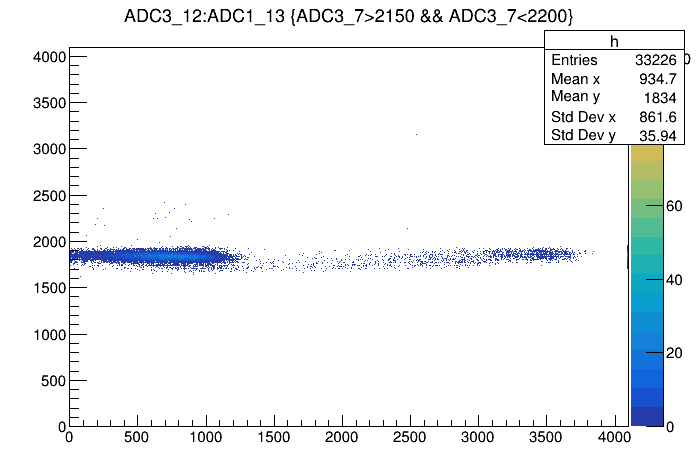

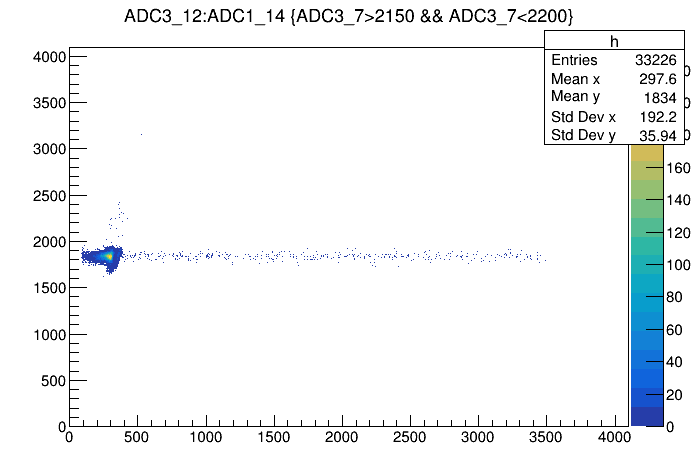

Jan | Analysis | run251 - Si-pad performance & status | Attached are plots for Si-pad 2 with hits from ionization of 206Pb81+ at the target.

The plots are representative for all Si-pads, the pattern is always the same!

y-axis: E n-side

x-axis: E p-side strip

condition: E_gate on peak in CsI

While strips 1, 2 and 7 look fine, strips 3 and 6 show already signs of degradation.

For strips 4 and 5, it is clearly visible that something is wrong.

Those are the central strips, which probably see the most rate.

The same dataset was analyzed here: https://elog.gsi.de/esr/E121/62

This might be a hint to a radiation damage or to the fact that we operate at too low bias voltage (32 Volt).

Maybe it recovers if we increase bias to 60 Volt. |

| Attachment 1: 251_Epad2_n_vs_p1.png

|

|

| Attachment 2: 251_Epad2_n_vs_p2.png

|

|

| Attachment 3: 251_Epad2_n_vs_p3.png

|

|

| Attachment 4: 251_Epad2_n_vs_p4.png

|

|

| Attachment 5: 251_Epad2_n_vs_p5.png

|

|

| Attachment 6: 251_Epad2_n_vs_p6.png

|

|

| Attachment 7: 251_Epad2_n_vs_p7.png

|

|

|

106

|

Tue Mar 31 15:30:43 2020 |

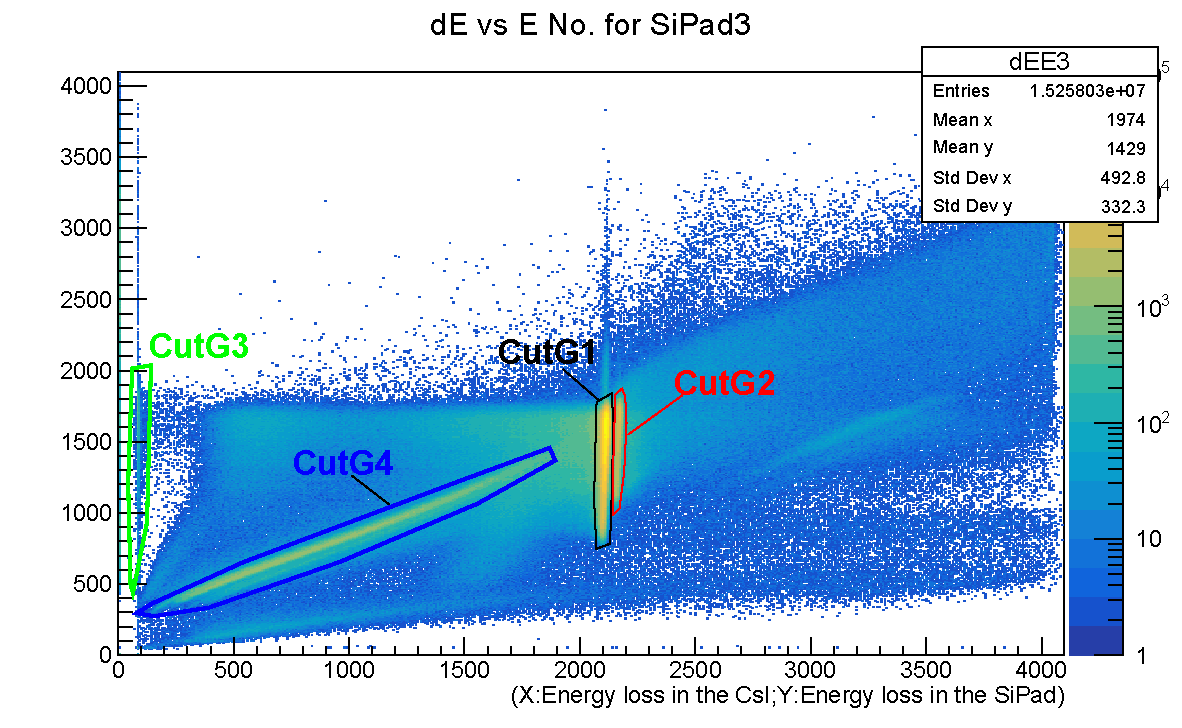

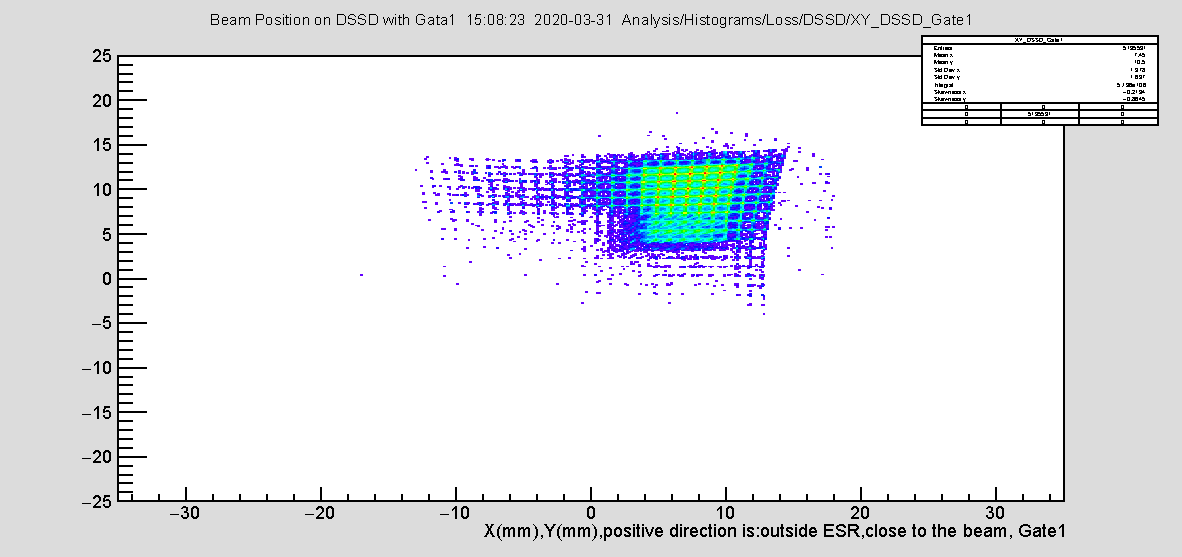

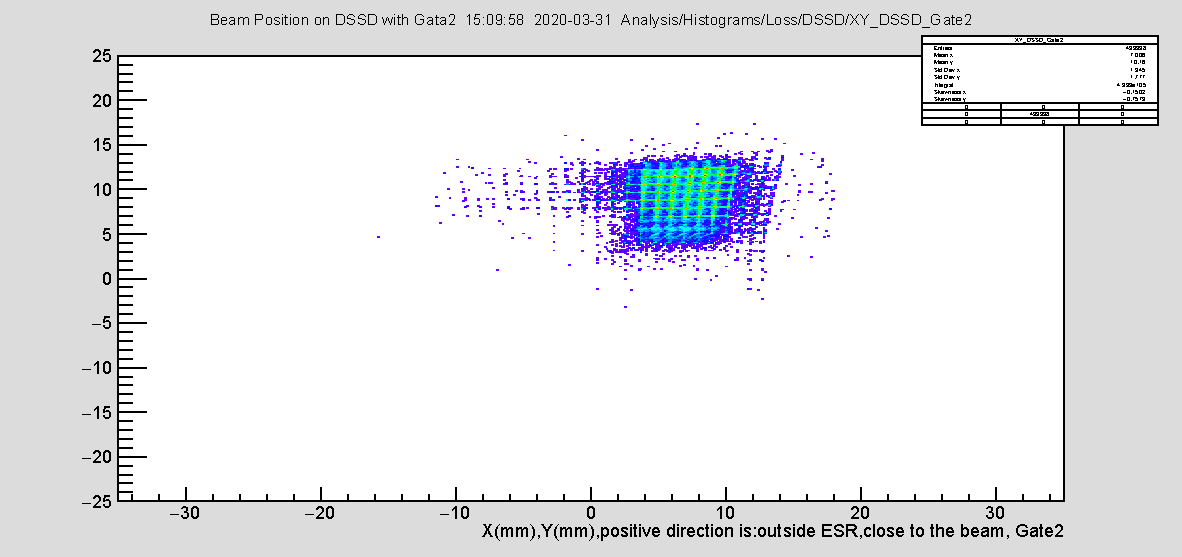

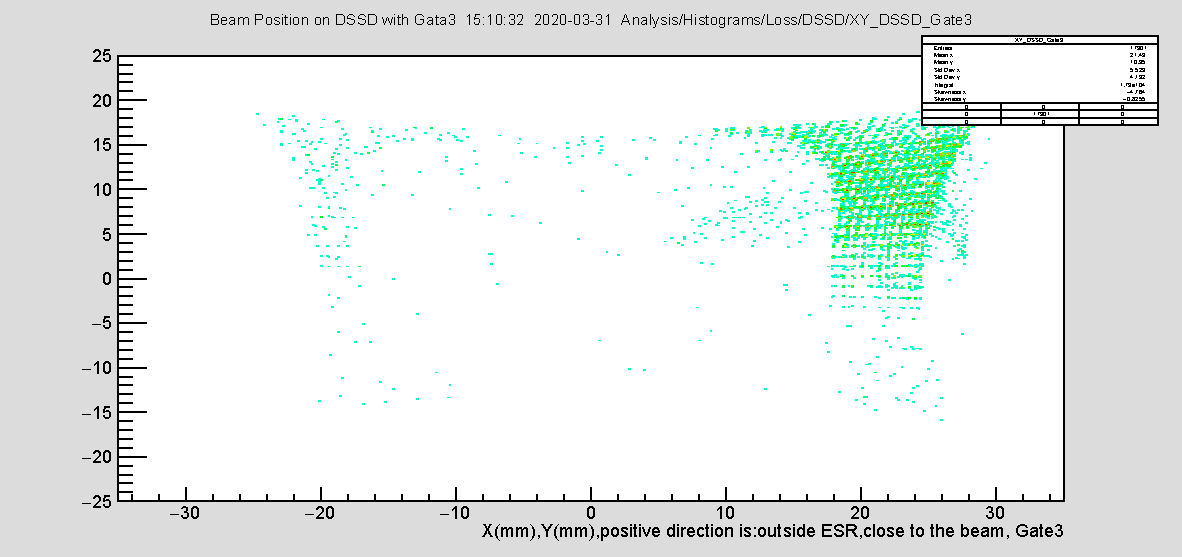

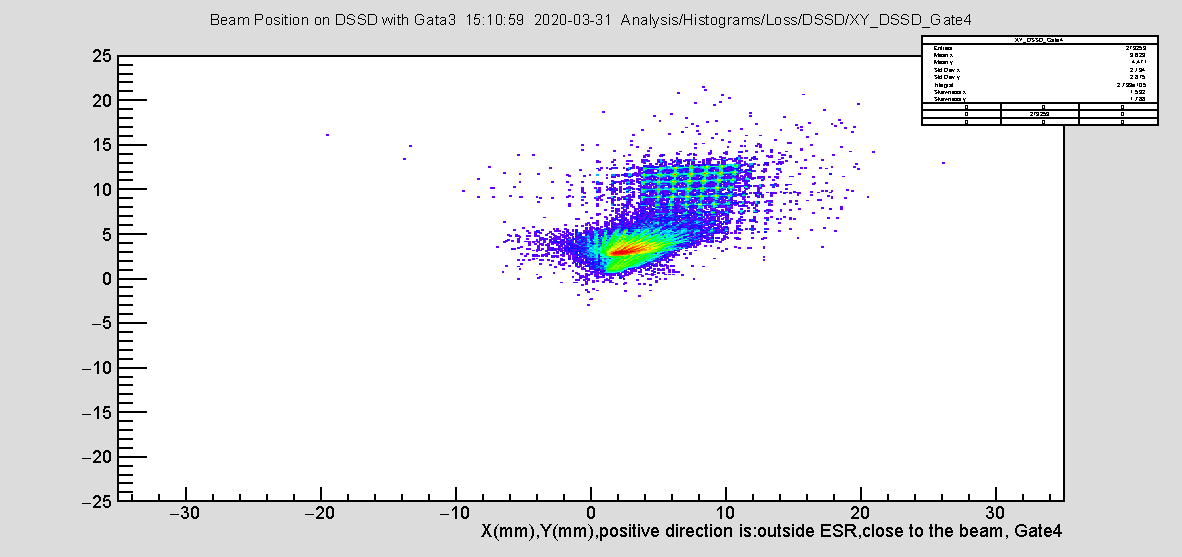

ruijiu | Analysis | The beam position on DSSD with different conditions on on the dEE spectrum | I analyzed the first measurement with 206Pb81+ beam, run 250-267. |

| Attachment 1: 202003311453.png

|

|

| Attachment 2: 202003311508.png

|

|

| Attachment 3: 202003311509.png

|

|

| Attachment 4: 202003311510.png

|

|

| Attachment 5: 202003311511.png

|

|

| Attachment 6: 202003311512.png

|

|

|

172

|

Fri Apr 17 18:27:34 2020 |

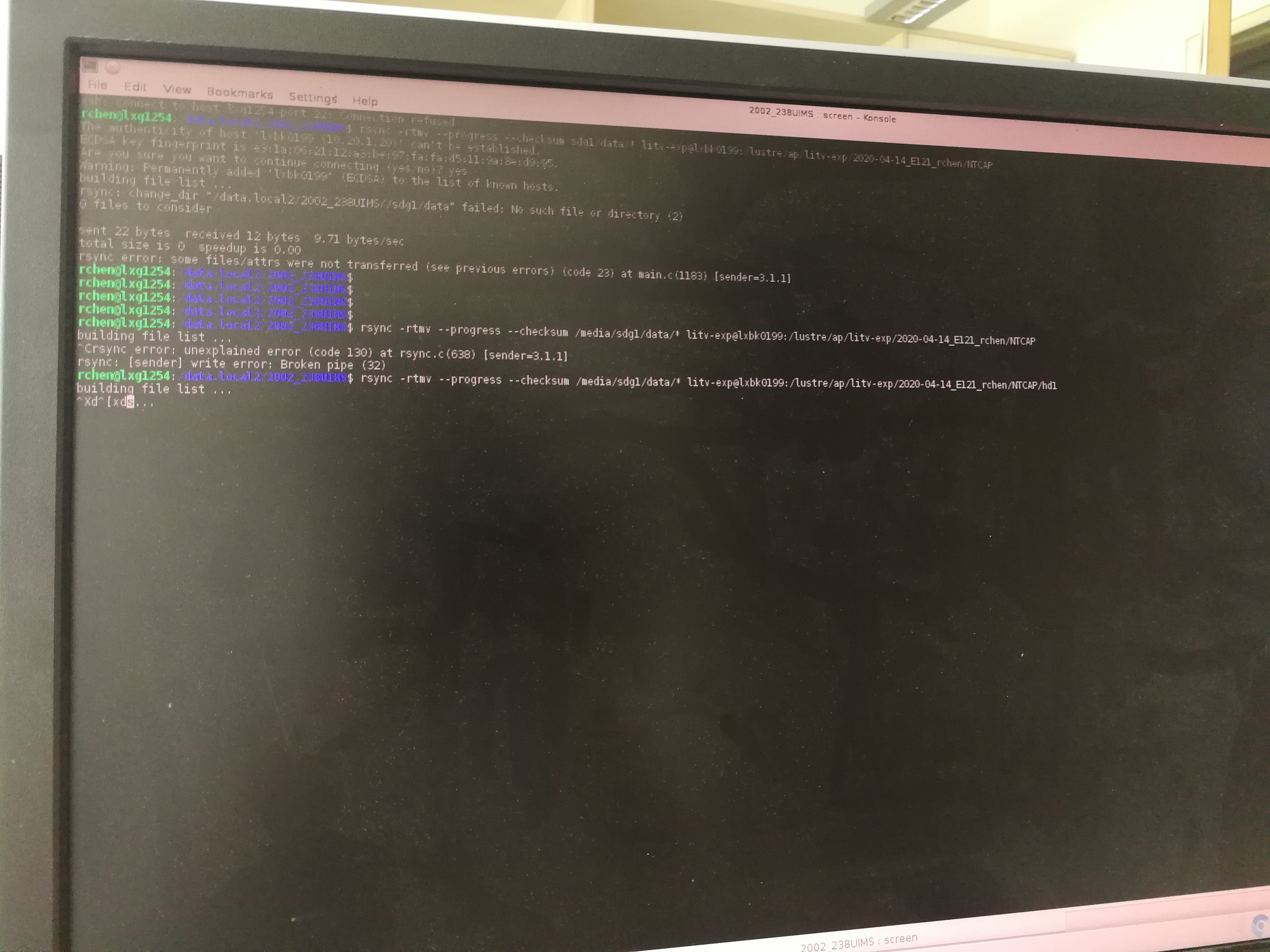

ruijiu | Analysis | backup data | 1.connect USB harddisk to computer lxg1254 and copy data to sever.

sync -rtmv --progress --checkSUD /media/sdgl/data/ litv-exp@sbk0l9:/lustre/ap/litv-exp/2020-

04-14 e121_rchen/NTCAP/hd1

2020.05.02 08:06 copied 11.88 TB to server. 1.8TB rest on hard disk. |

| Attachment 1: IMG_20200417_162202.jpg

|

|

|

174

|

Wed Aug 5 17:19:16 2020 |

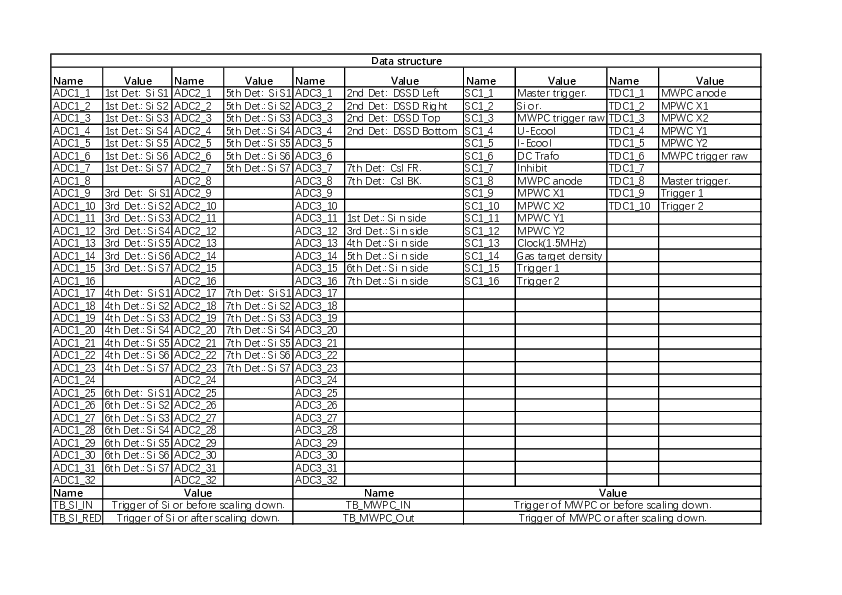

Rui-Jiu Chen | Analysis | Data structure | |

| Attachment 1: DataStructure.pdf

|

|

|

177

|

Thu Nov 5 15:13:43 2020 |

Jan | Analysis | root script example | Attached is an example root script/macro that shows how to use scripts for analysis.

Usage:

1. change INPUT and OUTPUT preprocessor variables in e121_analysis.c pointing to your desired input and output root-files.

2. open root and type: root [1] .L e121_analysis.C++

root [2] run() 3. check plots popping up and output files

Hints:

in e121_analysis.C use #include "e121_raw.h" for the original channel names/mapping (e.g. ADC1_1,...)

and use#include "e121_mapped.h" for named channels (e.g. e_csi[0] or e_dssd_top) |

| Attachment 1: e121_analysis.C

|

#define e121_analysis_cxx

// INPUT FILES

#define INPUT1 "/data.local1/E121/root-files/part1/e121_run_0253.root"

//#define INPUT2 ""

//#define INPUT3 ""

//#define INPUT4 ""

//#define INPUT5 ""

//#define INPUT6 ""

//#define INPUT7 ""

//#define INPUT8 ""

//#define INPUT9 ""

//#define INPUT10 ""

//OUTPUT FILE

#define OUTPUT "run253.ana.root"

#include <TH2.h>

#include <TStyle.h>

#include <TCanvas.h>

#include <cmath>

#include <string>

#include <cstdlib>

#include <cstdio>

#include <ctime>

#include <fstream>

#include <iostream>

#include <stdint.h>

#include "TROOT.h"

#include "TAttText.h"

#include "TAxis.h"

#include "TCanvas.h"

#include "TChain.h"

#include "TCut.h"

#include "TF1.h"

#include "TFile.h"

#include "TGraph.h"

#include "TGraphAsymmErrors.h"

#include "TGraphErrors.h"

#include "TH1.h"

#include "THistPainter.h"

#include "TKey.h"

#include "TLatex.h"

#include "TLegend.h"

#include "TMath.h"

#include "TMatrixD.h"

#include "TMinuit.h"

#include "TMultiGraph.h"

#include "TNtuple.h"

#include "TPave.h"

#include "TPaveText.h"

#include "TPoint.h"

#include "TRandom.h"

#include "TRint.h"

#include "TString.h"

#include "TTree.h"

#include "TH1F.h"

#include "TH2F.h"

#include "TSystem.h"

#include "TProfile.h"

#include "TVirtualFitter.h"

#include "TLegend.h"

#include "TColor.h"

#include "TBranch.h"

#include "TList.h"

using namespace std;

void loop(TChain *fChain)

{

if (fChain == 0) return;

//#include "e121_raw.h" // use this for raw mapping of channels

#include "e121_mapped.h" // use this for mapped channel names

///////////////////////////

// histogram definitions //

///////////////////////////

// energy

TList *e_histo= new TList();

TH1D *h_e_pad_1[7];

TH1D *h_e_pad_2[7];

TH1D *h_e_pad_3[7];

TH1D *h_e_pad_4[7];

TH1D *h_e_pad_5[7];

TH1D *h_e_pad_6[7];

TH1D *h_e_pad_n[7];

TH1D *h_e_pad_n_lo[7];

TH1D *h_e_pad_n_hi[7];

char chnumber[300];

for (int i=0;i<7;i++)

{

sprintf(chnumber,"e_pad_1_strip_%d",i);

h_e_pad_1[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_1[i]);

sprintf(chnumber,"e_pad_2_strip_%d",i);

h_e_pad_2[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_2[i]);

sprintf(chnumber,"e_pad_3_strip_%d",i);

h_e_pad_3[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_3[i]);

sprintf(chnumber,"e_pad_4_strip_%d",i);

h_e_pad_4[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_4[i]);

sprintf(chnumber,"e_pad_5_strip_%d",i);

h_e_pad_5[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_5[i]);

sprintf(chnumber,"e_pad_6_strip_%d",i);

h_e_pad_6[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_6[i]);

sprintf(chnumber,"e_pad_%d_n-side",i);

h_e_pad_n[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n[i]);

sprintf(chnumber,"e_pad_%d_n-side_lo",i);

h_e_pad_n_lo[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n_lo[i]);

sprintf(chnumber,"e_pad_%d_n-side_hi",i);

h_e_pad_n_hi[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n_hi[i]);

}

TH1D *h_e_dssd_left=new TH1D("e_dssd_left","e_dssd_left",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_left);

TH1D *h_e_dssd_right=new TH1D("e_dssd_right","e_dssd_right",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_right);

TH1D *h_e_dssd_top=new TH1D("e_dssd_top","e_dssd_top",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_top);

TH1D *h_e_dssd_bottom=new TH1D("e_dssd_bottom","e_dssd_bottom",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_bottom);

TH1D *h_e_csi[2];

h_e_csi[0]=new TH1D("e_csi_0","e_csi_0",4096,0.5,4096.5);

e_histo->Add(h_e_csi[0]);

h_e_csi[1]=new TH1D("e_csi_1","e_csi_1",4096,0.5,4096.5);

e_histo->Add(h_e_csi[1]);

// position

// time

// scaler

TList *sc_histo= new TList();

Int_t sc_bins = 500;

TGraph *g_sc_si=new TGraph();

g_sc_si->SetNameTitle("g_sc_si", "rate Si OR");

sc_histo->Add(g_sc_si);

TGraph *g_sc_mwpc=new TGraph();

g_sc_mwpc->SetNameTitle("g_sc_mwpc", "rate MWPC anode");

sc_histo->Add(g_sc_mwpc);

TGraph *g_sc_target=new TGraph();

g_sc_target->SetNameTitle("g_sc_target", "target density");

sc_histo->Add(g_sc_target);

TGraph *g_sc_trafo=new TGraph();

g_sc_trafo->SetNameTitle("g_sc_trafo", "ESR ion current");

sc_histo->Add(g_sc_trafo);

TGraph *g_sc_inhibit=new TGraph();

g_sc_inhibit->SetNameTitle("g_sc_inhibit", "target inhibit");

sc_histo->Add(g_sc_inhibit);

TGraph *g_sc_clock=new TGraph();

g_sc_clock->SetNameTitle("g_sc_clock", "1.5 MHz clock");

sc_histo->Add(g_sc_clock);

ULong64_t sc_si_sum = 0;

ULong64_t sc_mwpc_sum = 0;

ULong64_t sc_clock_sum = 0;

ULong64_t sc_target_sum = 0;

ULong64_t sc_trafo_sum = 0;

ULong64_t sc_inhibit_sum = 0;

Int_t sc_interval = 1; //interval time [sec] for scaler plotting

Double_t clock_ref = 1.5e6; // clock reference rate = 1.5 MHz

Double_t t_diff = 0;

Double_t t_elapsed = 0;

// get number of events to process

Long64_t nentries = fChain->GetEntries();

Long64_t nbytes = 0, nb = 0;

//////////////////////

// EVENT LOOP START //

//////////////////////

for (Long64_t i=0; i<nentries;i++)

// for (Long64_t i=0; i<10000;i++)

{

nb = fChain->GetEntry(i); nbytes += nb;

// event countdown

if ((float(i)/100000.)==int(i/100000)){cout << "event: " << i << " \tof " << nentries << endl;}

//////////////////////

//scaler processing //

//////////////////////

sc_si_sum += sc_silicon_or;

sc_mwpc_sum += sc_mwpc_anode;

sc_clock_sum += sc_clock;

sc_target_sum += sc_target;

sc_trafo_sum += sc_trafo;

sc_inhibit_sum += sc_inhibit;

t_elapsed += (double)(sc_clock/clock_ref);

t_diff = (double)(sc_clock_sum/clock_ref);

// fill the scaler sums to histo for very interval

if( !((int)t_diff % sc_interval) && (int)t_diff > 0 )

//if( true )

{

if ( (int)t_diff <= 2*sc_interval ) //exclude large time intervals >> crap data

{

// cout << "time: " << t_elapsed << " trafo:" << sc_trafo_sum;

// cout << " diff: " << t_diff << " modulo: " << ((int)t_diff % sc_interval) << endl;

g_sc_si->SetPoint(g_sc_si->GetN() ,t_elapsed, sc_si_sum);

g_sc_mwpc->SetPoint(g_sc_mwpc->GetN() ,t_elapsed, sc_mwpc_sum);

g_sc_target->SetPoint(g_sc_target->GetN() ,t_elapsed, sc_target_sum);

g_sc_trafo->SetPoint(g_sc_trafo->GetN() ,t_elapsed, sc_trafo_sum);

g_sc_inhibit->SetPoint(g_sc_inhibit->GetN(),t_elapsed, sc_inhibit_sum);

g_sc_clock->SetPoint(g_sc_clock->GetN() ,t_elapsed, sc_clock_sum);

}

sc_si_sum = 0;

sc_mwpc_sum = 0;

sc_clock_sum = 0;

sc_target_sum = 0;

sc_trafo_sum = 0;

sc_inhibit_sum = 0;

}

////////////////////

// energy spectra //

////////////////////

if(TRIGGER==1)

{

for (int i=0;i<7;i++)

{

h_e_pad_1[i]->Fill(e_pad_1[i]);

h_e_pad_2[i]->Fill(e_pad_2[i]);

h_e_pad_3[i]->Fill(e_pad_3[i]);

h_e_pad_4[i]->Fill(e_pad_4[i]);

h_e_pad_5[i]->Fill(e_pad_5[i]);

h_e_pad_6[i]->Fill(e_pad_6[i]);

if ( i > 0 )

{

h_e_pad_n[i]->Fill(e_pad_n[i]);

if ( t_elapsed >= 30 && t_elapsed <= 100 ) h_e_pad_n_hi[i]->Fill(e_pad_n[i]);

if ( t_elapsed >= 250 && t_elapsed <= 350 ) h_e_pad_n_lo[i]->Fill(e_pad_n[i]);

}

}

}

}

////////////////////

// EVENT LOOP END //

////////////////////

// write output file

TFile *outfile = TFile::Open(OUTPUT, "RECREATE");

e_histo->Write("energy", TObject::kSingleKey);

sc_histo->Write("scaler", TObject::kSingleKey);

outfile->Close();

cout << "\033[0;32m" << OUTPUT << " is created!\033[0m" << endl;

// direct plotting (optional)

TCanvas *c_test = new TCanvas("test","test", 1000, 1200);

c_test->Divide(1,5);

c_test->cd(1);

g_sc_si->SetFillColor(15);

g_sc_si->Draw("AB");

c_test->cd(2);

g_sc_mwpc->SetFillColor(15);

g_sc_mwpc->Draw("AB");

c_test->cd(3);

g_sc_target->SetFillColor(15);

g_sc_target->Draw("AB");

c_test->cd(4);

g_sc_trafo->SetFillColor(15);

g_sc_trafo->Draw("AB");

c_test->cd(5);

... 108 more lines ...

|

| Attachment 2: e121_mapped.h

|

//////////////////////////////////////////////////////////

// This class has been automatically generated on

// Wed Nov 4 09:54:00 2020 by ROOT version 6.18/04

// from TTree h101/CWNtuple

// found on file: /data.local1/E121/root-files/part1/e121_run_0252.root

//////////////////////////////////////////////////////////

// Declaration of leaf types

// DAQ

UInt_t TRIGGER; //

UInt_t EVENTNO; //

UInt_t TB_SI_IN;

UInt_t TB_SI_RED;

UInt_t TB_MWPC_IN;

UInt_t TB_MWPC_RED;

// ADCs

UInt_t e_pad_1[7];

UInt_t e_pad_2[7];

UInt_t e_pad_3[7];

UInt_t e_pad_4[7];

UInt_t e_pad_5[7];

UInt_t e_pad_6[7];

UInt_t e_pad_n[7];

UInt_t e_dssd_top, e_dssd_bottom, e_dssd_left, e_dssd_right;

UInt_t e_csi[2];

//TDCs

UInt_t t_mwpc_x1, t_mwpc_x2, t_mwpc_y1, t_mwpc_y2, t_mwpc_anode, t_mwpc_raw;

UInt_t t_master_trig, t_trig_1, t_trig_2;

//Scalers

UInt_t sc_master_trig;

UInt_t sc_silicon_or;

UInt_t sc_mwpc_raw;

UInt_t sc_u_cool;

UInt_t sc_i_cool;

UInt_t sc_trafo;

UInt_t sc_inhibit;

UInt_t sc_mwpc_anode;

UInt_t sc_mwpc_x1;

UInt_t sc_mwpc_x2;

UInt_t sc_mwpc_y1;

UInt_t sc_mwpc_y2;

UInt_t sc_clock;

UInt_t sc_target;

UInt_t sc_trig_1;

UInt_t sc_trig_2;

// Set branch addresses

fChain->SetBranchAddress("TRIGGER", &TRIGGER);

fChain->SetBranchAddress("EVENTNO", &EVENTNO);

fChain->SetBranchAddress("ADC1_1", &e_pad_1[0]);

fChain->SetBranchAddress("ADC1_2", &e_pad_1[1]);

fChain->SetBranchAddress("ADC1_3", &e_pad_1[2]);

fChain->SetBranchAddress("ADC1_4", &e_pad_1[3]);

fChain->SetBranchAddress("ADC1_5", &e_pad_1[4]);

fChain->SetBranchAddress("ADC1_6", &e_pad_1[5]);

fChain->SetBranchAddress("ADC1_7", &e_pad_1[6]);

//fChain->SetBranchAddress("ADC1_8", &);

fChain->SetBranchAddress("ADC1_9", &e_pad_2[0]);

fChain->SetBranchAddress("ADC1_10", &e_pad_2[1]);

fChain->SetBranchAddress("ADC1_11", &e_pad_2[2]);

fChain->SetBranchAddress("ADC1_12", &e_pad_2[3]);

fChain->SetBranchAddress("ADC1_13", &e_pad_2[4]);

fChain->SetBranchAddress("ADC1_14", &e_pad_2[5]);

fChain->SetBranchAddress("ADC1_15", &e_pad_2[6]);

// fChain->SetBranchAddress("ADC1_16", &);

fChain->SetBranchAddress("ADC1_17", &e_pad_3[0]);

fChain->SetBranchAddress("ADC1_18", &e_pad_3[1]);

fChain->SetBranchAddress("ADC1_19", &e_pad_3[2]);

fChain->SetBranchAddress("ADC1_20", &e_pad_3[3]);

fChain->SetBranchAddress("ADC1_21", &e_pad_3[4]);

fChain->SetBranchAddress("ADC1_22", &e_pad_3[5]);

fChain->SetBranchAddress("ADC1_23", &e_pad_3[6]);

// fChain->SetBranchAddress("ADC1_24", &);

fChain->SetBranchAddress("ADC1_25", &e_pad_4[0]);

fChain->SetBranchAddress("ADC1_26", &e_pad_4[1]);

fChain->SetBranchAddress("ADC1_27", &e_pad_4[2]);

fChain->SetBranchAddress("ADC1_28", &e_pad_4[3]);

fChain->SetBranchAddress("ADC1_29", &e_pad_4[4]);

fChain->SetBranchAddress("ADC1_30", &e_pad_4[5]);

fChain->SetBranchAddress("ADC1_31", &e_pad_4[6]);

// fChain->SetBranchAddress("ADC1_32", &);

fChain->SetBranchAddress("ADC2_1", &e_pad_5[0]);

fChain->SetBranchAddress("ADC2_2", &e_pad_5[1]);

fChain->SetBranchAddress("ADC2_3", &e_pad_5[2]);

fChain->SetBranchAddress("ADC2_4", &e_pad_5[3]);

fChain->SetBranchAddress("ADC2_5", &e_pad_5[4]);

fChain->SetBranchAddress("ADC2_6", &e_pad_5[5]);

fChain->SetBranchAddress("ADC2_7", &e_pad_5[6]);

// fChain->SetBranchAddress("ADC2_8", &);

// fChain->SetBranchAddress("ADC2_9", &);

// fChain->SetBranchAddress("ADC2_10", &);

// fChain->SetBranchAddress("ADC2_11", &);

// fChain->SetBranchAddress("ADC2_12", &);

// fChain->SetBranchAddress("ADC2_13", &);

// fChain->SetBranchAddress("ADC2_14", &);

// fChain->SetBranchAddress("ADC2_15", &);

// fChain->SetBranchAddress("ADC2_16", &);

fChain->SetBranchAddress("ADC2_17", &e_pad_6[0]);

fChain->SetBranchAddress("ADC2_18", &e_pad_6[1]);

fChain->SetBranchAddress("ADC2_19", &e_pad_6[2]);

fChain->SetBranchAddress("ADC2_20", &e_pad_6[3]);

fChain->SetBranchAddress("ADC2_21", &e_pad_6[4]);

fChain->SetBranchAddress("ADC2_22", &e_pad_6[5]);

fChain->SetBranchAddress("ADC2_23", &e_pad_6[6]);

// fChain->SetBranchAddress("ADC2_24", &);

// fChain->SetBranchAddress("ADC2_25", &);

// fChain->SetBranchAddress("ADC2_26", &);

// fChain->SetBranchAddress("ADC2_27", &);

// fChain->SetBranchAddress("ADC2_28", &);

// fChain->SetBranchAddress("ADC2_29", &);

// fChain->SetBranchAddress("ADC2_30", &);

// fChain->SetBranchAddress("ADC2_31", &);

// fChain->SetBranchAddress("ADC2_32", &);

fChain->SetBranchAddress("ADC3_1", &e_dssd_left);

fChain->SetBranchAddress("ADC3_2", &e_dssd_right);

fChain->SetBranchAddress("ADC3_3", &e_dssd_top);

fChain->SetBranchAddress("ADC3_4", &e_dssd_bottom);

// fChain->SetBranchAddress("ADC3_5", &);

// fChain->SetBranchAddress("ADC3_6", &);

fChain->SetBranchAddress("ADC3_7", &e_csi[0]);

fChain->SetBranchAddress("ADC3_8", &e_csi[1]);

// fChain->SetBranchAddress("ADC3_9", &);

// fChain->SetBranchAddress("ADC3_10", &);

fChain->SetBranchAddress("ADC3_11", &e_pad_n[1]);

fChain->SetBranchAddress("ADC3_12", &e_pad_n[2]);

fChain->SetBranchAddress("ADC3_13", &e_pad_n[3]);

fChain->SetBranchAddress("ADC3_14", &e_pad_n[4]);

fChain->SetBranchAddress("ADC3_15", &e_pad_n[5]);

fChain->SetBranchAddress("ADC3_16", &e_pad_n[6]);

// fChain->SetBranchAddress("ADC3_17", &);

// fChain->SetBranchAddress("ADC3_18", &);

// fChain->SetBranchAddress("ADC3_19", &);

// fChain->SetBranchAddress("ADC3_20", &);

// fChain->SetBranchAddress("ADC3_21", &);

// fChain->SetBranchAddress("ADC3_22", &);

// fChain->SetBranchAddress("ADC3_23", &);

// fChain->SetBranchAddress("ADC3_24", &);

// fChain->SetBranchAddress("ADC3_25", &);

// fChain->SetBranchAddress("ADC3_26", &);

// fChain->SetBranchAddress("ADC3_27", &);

// fChain->SetBranchAddress("ADC3_28", &);

// fChain->SetBranchAddress("ADC3_29", &);

// fChain->SetBranchAddress("ADC3_30", &);

// fChain->SetBranchAddress("ADC3_31", &);

// fChain->SetBranchAddress("ADC3_32", &);

fChain->SetBranchAddress("SC1", &sc_master_trig);

fChain->SetBranchAddress("SC2", &sc_silicon_or);

fChain->SetBranchAddress("SC3", &sc_mwpc_raw);

fChain->SetBranchAddress("SC4", &sc_u_cool);

fChain->SetBranchAddress("SC5", &sc_i_cool);

fChain->SetBranchAddress("SC6", &sc_trafo);

fChain->SetBranchAddress("SC7", &sc_inhibit);

fChain->SetBranchAddress("SC8", &sc_mwpc_anode);

fChain->SetBranchAddress("SC9", &sc_mwpc_x1);

fChain->SetBranchAddress("SC10", &sc_mwpc_x2);

fChain->SetBranchAddress("SC11", &sc_mwpc_y1);

fChain->SetBranchAddress("SC12", &sc_mwpc_y2);

fChain->SetBranchAddress("SC13", &sc_clock);

fChain->SetBranchAddress("SC14", &sc_target);

fChain->SetBranchAddress("SC15", &sc_trig_1);

fChain->SetBranchAddress("SC16", &sc_trig_2);

// fChain->SetBranchAddress("SC17", &);

// fChain->SetBranchAddress("SC18", &);

// fChain->SetBranchAddress("SC19", &);

// fChain->SetBranchAddress("SC20", &);

// fChain->SetBranchAddress("SC21", &);

// fChain->SetBranchAddress("SC22", &);

// fChain->SetBranchAddress("SC23", &);

// fChain->SetBranchAddress("SC24", &);

// fChain->SetBranchAddress("SC25", &);

// fChain->SetBranchAddress("SC26", &);

// fChain->SetBranchAddress("SC27", &);

// fChain->SetBranchAddress("SC28", &);

// fChain->SetBranchAddress("SC29", &);

// fChain->SetBranchAddress("SC30", &);

// fChain->SetBranchAddress("SC31", &);

// fChain->SetBranchAddress("SC32", &);

fChain->SetBranchAddress("TDC1", &t_mwpc_anode);

fChain->SetBranchAddress("TDC2", &t_mwpc_x1);

fChain->SetBranchAddress("TDC3", &t_mwpc_x2);

fChain->SetBranchAddress("TDC4", &t_mwpc_y1);

fChain->SetBranchAddress("TDC5", &t_mwpc_y2);

fChain->SetBranchAddress("TDC6", &t_mwpc_raw);

// fChain->SetBranchAddress("TDC7", &t_);

fChain->SetBranchAddress("TDC8", &t_master_trig);

fChain->SetBranchAddress("TDC9", &t_trig_1);

fChain->SetBranchAddress("TDC10", &t_trig_2);

fChain->SetBranchAddress("TB_SI_IN", &TB_SI_IN);

fChain->SetBranchAddress("TB_SI_RED", &TB_SI_RED);

fChain->SetBranchAddress("TB_MWPC_IN", &TB_MWPC_IN);

fChain->SetBranchAddress("TB_MWPC_RED", &TB_MWPC_RED);

|

| Attachment 3: e121_raw.h

|

//////////////////////////////////////////////////////////

// This class has been automatically generated on

// Wed Nov 4 09:54:00 2020 by ROOT version 6.18/04

// from TTree h101/CWNtuple

// found on file: /data.local1/E121/root-files/part1/e121_run_0252.root

//////////////////////////////////////////////////////////

// Declaration of leaf types

UInt_t TRIGGER; //

UInt_t EVENTNO; //

UInt_t ADC1_1;

UInt_t ADC1_2;

UInt_t ADC1_3;

UInt_t ADC1_4;

UInt_t ADC1_5;

UInt_t ADC1_6;

UInt_t ADC1_7;

UInt_t ADC1_8;

UInt_t ADC1_9;

UInt_t ADC1_10;

UInt_t ADC1_11;

UInt_t ADC1_12;

UInt_t ADC1_13;

UInt_t ADC1_14;

UInt_t ADC1_15;

UInt_t ADC1_16;

UInt_t ADC1_17;

UInt_t ADC1_18;

UInt_t ADC1_19;

UInt_t ADC1_20;

UInt_t ADC1_21;

UInt_t ADC1_22;

UInt_t ADC1_23;

UInt_t ADC1_24;

UInt_t ADC1_25;

UInt_t ADC1_26;

UInt_t ADC1_27;

UInt_t ADC1_28;

UInt_t ADC1_29;

UInt_t ADC1_30;

UInt_t ADC1_31;

UInt_t ADC1_32;

UInt_t ADC2_1;

UInt_t ADC2_2;

UInt_t ADC2_3;

UInt_t ADC2_4;

UInt_t ADC2_5;

UInt_t ADC2_6;

UInt_t ADC2_7;

UInt_t ADC2_8;

UInt_t ADC2_9;

UInt_t ADC2_10;

UInt_t ADC2_11;

UInt_t ADC2_12;

UInt_t ADC2_13;

UInt_t ADC2_14;

UInt_t ADC2_15;

UInt_t ADC2_16;

UInt_t ADC2_17;

UInt_t ADC2_18;

UInt_t ADC2_19;

UInt_t ADC2_20;

UInt_t ADC2_21;

UInt_t ADC2_22;

UInt_t ADC2_23;

UInt_t ADC2_24;

UInt_t ADC2_25;

UInt_t ADC2_26;

UInt_t ADC2_27;

UInt_t ADC2_28;

UInt_t ADC2_29;

UInt_t ADC2_30;

UInt_t ADC2_31;

UInt_t ADC2_32;

UInt_t ADC3_1;

UInt_t ADC3_2;

UInt_t ADC3_3;

UInt_t ADC3_4;

UInt_t ADC3_5;

UInt_t ADC3_6;

UInt_t ADC3_7;

UInt_t ADC3_8;

UInt_t ADC3_9;

UInt_t ADC3_10;

UInt_t ADC3_11;

UInt_t ADC3_12;

UInt_t ADC3_13;

UInt_t ADC3_14;

UInt_t ADC3_15;

UInt_t ADC3_16;

UInt_t ADC3_17;

UInt_t ADC3_18;

UInt_t ADC3_19;

UInt_t ADC3_20;

UInt_t ADC3_21;

UInt_t ADC3_22;

UInt_t ADC3_23;

UInt_t ADC3_24;

UInt_t ADC3_25;

UInt_t ADC3_26;

UInt_t ADC3_27;

UInt_t ADC3_28;

UInt_t ADC3_29;

UInt_t ADC3_30;

UInt_t ADC3_31;

UInt_t ADC3_32;

UInt_t SC1;

UInt_t SC2;

UInt_t SC3;

UInt_t SC4;

UInt_t SC5;

UInt_t SC6;

UInt_t SC7;

UInt_t SC8;

UInt_t SC9;

UInt_t SC10;

UInt_t SC11;

UInt_t SC12;

UInt_t SC13;

UInt_t SC14;

UInt_t SC15;

UInt_t SC16;

UInt_t SC17;

UInt_t SC18;

UInt_t SC19;

UInt_t SC20;

UInt_t SC21;

UInt_t SC22;

UInt_t SC23;

UInt_t SC24;

UInt_t SC25;

UInt_t SC26;

UInt_t SC27;

UInt_t SC28;

UInt_t SC29;

UInt_t SC30;

UInt_t SC31;

UInt_t SC32;

UInt_t TDC1;

UInt_t TDC2;

UInt_t TDC3;

UInt_t TDC4;

UInt_t TDC5;

UInt_t TDC6;

UInt_t TDC7;

UInt_t TDC8;

UInt_t TDC9;

UInt_t TDC10;

UInt_t TB_SI_IN;

UInt_t TB_SI_RED;

UInt_t TB_MWPC_IN;

UInt_t TB_MWPC_RED;

// Set branch addresses

fChain->SetBranchAddress("TRIGGER", &TRIGGER );

fChain->SetBranchAddress("EVENTNO", &EVENTNO );

fChain->SetBranchAddress("ADC1_1", &ADC1_1 );

fChain->SetBranchAddress("ADC1_2", &ADC1_2 );

fChain->SetBranchAddress("ADC1_3", &ADC1_3 );

fChain->SetBranchAddress("ADC1_4", &ADC1_4 );

fChain->SetBranchAddress("ADC1_5", &ADC1_5 );

fChain->SetBranchAddress("ADC1_6", &ADC1_6 );

fChain->SetBranchAddress("ADC1_7", &ADC1_7 );

fChain->SetBranchAddress("ADC1_8", &ADC1_8 );

fChain->SetBranchAddress("ADC1_9", &ADC1_9 );

fChain->SetBranchAddress("ADC1_10", &ADC1_10 );

fChain->SetBranchAddress("ADC1_11", &ADC1_11 );

fChain->SetBranchAddress("ADC1_12", &ADC1_12 );

fChain->SetBranchAddress("ADC1_13", &ADC1_13 );

fChain->SetBranchAddress("ADC1_14", &ADC1_14 );

fChain->SetBranchAddress("ADC1_15", &ADC1_15 );

fChain->SetBranchAddress("ADC1_16", &ADC1_16 );

fChain->SetBranchAddress("ADC1_17", &ADC1_17 );

fChain->SetBranchAddress("ADC1_18", &ADC1_18 );

fChain->SetBranchAddress("ADC1_19", &ADC1_19 );

fChain->SetBranchAddress("ADC1_20", &ADC1_20 );

fChain->SetBranchAddress("ADC1_21", &ADC1_21 );

fChain->SetBranchAddress("ADC1_22", &ADC1_22 );

fChain->SetBranchAddress("ADC1_23", &ADC1_23 );

fChain->SetBranchAddress("ADC1_24", &ADC1_24 );

fChain->SetBranchAddress("ADC1_25", &ADC1_25 );

fChain->SetBranchAddress("ADC1_26", &ADC1_26 );

fChain->SetBranchAddress("ADC1_27", &ADC1_27 );

fChain->SetBranchAddress("ADC1_28", &ADC1_28 );

fChain->SetBranchAddress("ADC1_29", &ADC1_29 );

fChain->SetBranchAddress("ADC1_30", &ADC1_30 );

fChain->SetBranchAddress("ADC1_31", &ADC1_31 );

fChain->SetBranchAddress("ADC1_32", &ADC1_32 );

fChain->SetBranchAddress("ADC2_1", &ADC2_1 );

fChain->SetBranchAddress("ADC2_2", &ADC2_2 );

fChain->SetBranchAddress("ADC2_3", &ADC2_3 );

fChain->SetBranchAddress("ADC2_4", &ADC2_4 );

fChain->SetBranchAddress("ADC2_5", &ADC2_5 );

fChain->SetBranchAddress("ADC2_6", &ADC2_6 );

fChain->SetBranchAddress("ADC2_7", &ADC2_7 );

fChain->SetBranchAddress("ADC2_8", &ADC2_8 );

fChain->SetBranchAddress("ADC2_9", &ADC2_9 );

fChain->SetBranchAddress("ADC2_10", &ADC2_10 );

fChain->SetBranchAddress("ADC2_11", &ADC2_11 );

fChain->SetBranchAddress("ADC2_12", &ADC2_12 );

fChain->SetBranchAddress("ADC2_13", &ADC2_13 );

fChain->SetBranchAddress("ADC2_14", &ADC2_14 );

fChain->SetBranchAddress("ADC2_15", &ADC2_15 );

fChain->SetBranchAddress("ADC2_16", &ADC2_16 );

fChain->SetBranchAddress("ADC2_17", &ADC2_17 );

fChain->SetBranchAddress("ADC2_18", &ADC2_18 );

fChain->SetBranchAddress("ADC2_19", &ADC2_19 );

fChain->SetBranchAddress("ADC2_20", &ADC2_20 );

fChain->SetBranchAddress("ADC2_21", &ADC2_21 );

fChain->SetBranchAddress("ADC2_22", &ADC2_22 );

fChain->SetBranchAddress("ADC2_23", &ADC2_23 );

fChain->SetBranchAddress("ADC2_24", &ADC2_24 );

fChain->SetBranchAddress("ADC2_25", &ADC2_25 );

fChain->SetBranchAddress("ADC2_26", &ADC2_26 );

fChain->SetBranchAddress("ADC2_27", &ADC2_27 );

fChain->SetBranchAddress("ADC2_28", &ADC2_28 );

fChain->SetBranchAddress("ADC2_29", &ADC2_29 );

fChain->SetBranchAddress("ADC2_30", &ADC2_30 );

fChain->SetBranchAddress("ADC2_31", &ADC2_31 );

fChain->SetBranchAddress("ADC2_32", &ADC2_32 );

fChain->SetBranchAddress("ADC3_1", &ADC3_1 );

fChain->SetBranchAddress("ADC3_2", &ADC3_2 );

fChain->SetBranchAddress("ADC3_3", &ADC3_3 );

fChain->SetBranchAddress("ADC3_4", &ADC3_4 );

fChain->SetBranchAddress("ADC3_5", &ADC3_5 );

fChain->SetBranchAddress("ADC3_6", &ADC3_6 );

fChain->SetBranchAddress("ADC3_7", &ADC3_7 );

fChain->SetBranchAddress("ADC3_8", &ADC3_8 );

fChain->SetBranchAddress("ADC3_9", &ADC3_9 );

fChain->SetBranchAddress("ADC3_10", &ADC3_10 );

fChain->SetBranchAddress("ADC3_11", &ADC3_11 );

fChain->SetBranchAddress("ADC3_12", &ADC3_12 );

fChain->SetBranchAddress("ADC3_13", &ADC3_13 );

fChain->SetBranchAddress("ADC3_14", &ADC3_14 );

fChain->SetBranchAddress("ADC3_15", &ADC3_15 );

fChain->SetBranchAddress("ADC3_16", &ADC3_16 );

fChain->SetBranchAddress("ADC3_17", &ADC3_17 );

fChain->SetBranchAddress("ADC3_18", &ADC3_18 );

fChain->SetBranchAddress("ADC3_19", &ADC3_19 );

fChain->SetBranchAddress("ADC3_20", &ADC3_20 );

fChain->SetBranchAddress("ADC3_21", &ADC3_21 );

fChain->SetBranchAddress("ADC3_22", &ADC3_22 );

fChain->SetBranchAddress("ADC3_23", &ADC3_23 );

fChain->SetBranchAddress("ADC3_24", &ADC3_24 );

fChain->SetBranchAddress("ADC3_25", &ADC3_25 );

fChain->SetBranchAddress("ADC3_26", &ADC3_26 );

fChain->SetBranchAddress("ADC3_27", &ADC3_27 );

fChain->SetBranchAddress("ADC3_28", &ADC3_28 );

fChain->SetBranchAddress("ADC3_29", &ADC3_29 );

fChain->SetBranchAddress("ADC3_30", &ADC3_30 );

fChain->SetBranchAddress("ADC3_31", &ADC3_31 );

fChain->SetBranchAddress("ADC3_32", &ADC3_32 );

fChain->SetBranchAddress("SC1", &SC1 );

fChain->SetBranchAddress("SC2", &SC2 );

fChain->SetBranchAddress("SC3", &SC3 );

fChain->SetBranchAddress("SC4", &SC4 );

fChain->SetBranchAddress("SC5", &SC5 );

fChain->SetBranchAddress("SC6", &SC6 );

fChain->SetBranchAddress("SC7", &SC7 );

fChain->SetBranchAddress("SC8", &SC8 );

fChain->SetBranchAddress("SC9", &SC9 );

fChain->SetBranchAddress("SC10", &SC10 );

fChain->SetBranchAddress("SC11", &SC11 );

fChain->SetBranchAddress("SC12", &SC12 );

fChain->SetBranchAddress("SC13", &SC13 );

fChain->SetBranchAddress("SC14", &SC14 );

fChain->SetBranchAddress("SC15", &SC15 );

fChain->SetBranchAddress("SC16", &SC16 );

fChain->SetBranchAddress("SC17", &SC17 );

fChain->SetBranchAddress("SC18", &SC18 );

fChain->SetBranchAddress("SC19", &SC19 );

fChain->SetBranchAddress("SC20", &SC20 );

fChain->SetBranchAddress("SC21", &SC21 );

fChain->SetBranchAddress("SC22", &SC22 );

fChain->SetBranchAddress("SC23", &SC23 );

fChain->SetBranchAddress("SC24", &SC24 );

fChain->SetBranchAddress("SC25", &SC25 );

fChain->SetBranchAddress("SC26", &SC26 );

fChain->SetBranchAddress("SC27", &SC27 );

fChain->SetBranchAddress("SC28", &SC28 );

fChain->SetBranchAddress("SC29", &SC29 );

fChain->SetBranchAddress("SC30", &SC30 );

fChain->SetBranchAddress("SC31", &SC31 );

fChain->SetBranchAddress("SC32", &SC32 );

fChain->SetBranchAddress("TDC1", &TDC1 );

fChain->SetBranchAddress("TDC2", &TDC2 );

fChain->SetBranchAddress("TDC3", &TDC3 );

fChain->SetBranchAddress("TDC4", &TDC4 );

fChain->SetBranchAddress("TDC5", &TDC5 );

fChain->SetBranchAddress("TDC6", &TDC6 );

fChain->SetBranchAddress("TDC7", &TDC7 );

fChain->SetBranchAddress("TDC8", &TDC8 );

fChain->SetBranchAddress("TDC9", &TDC9 );

fChain->SetBranchAddress("TDC10", &TDC10 );

fChain->SetBranchAddress("TB_SI_IN", &TB_SI_IN);

fChain->SetBranchAddress("TB_SI_RED", &TB_SI_RED);

fChain->SetBranchAddress("TB_MWPC_IN", &TB_MWPC_IN);

fChain->SetBranchAddress("TB_MWPC_RED", &TB_MWPC_RED);

|

|

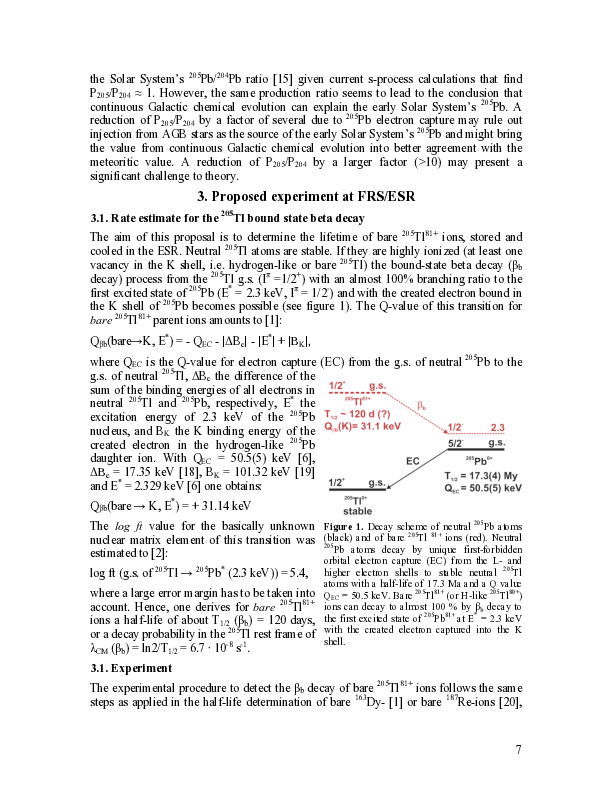

1

|

Thu Sep 13 11:32:17 2018 |

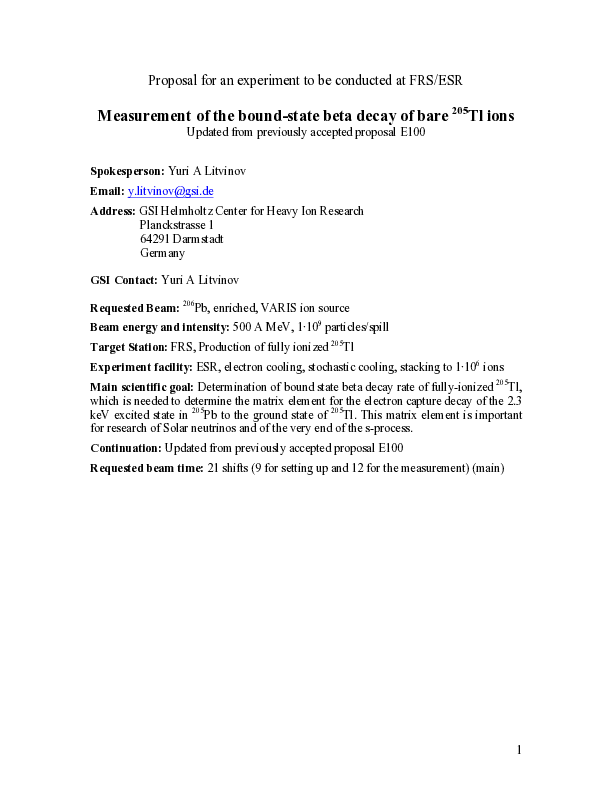

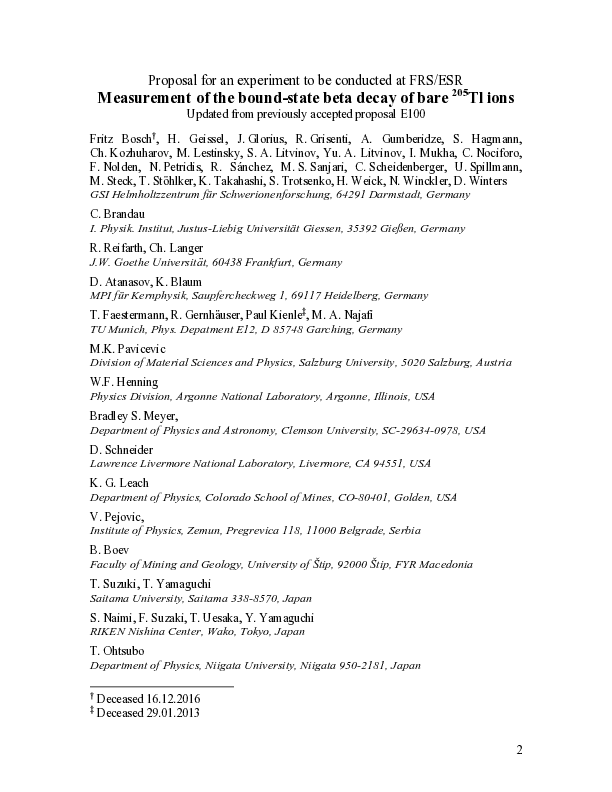

Jan Glorius | Collaboration | Proposal | | Attached is the beam time proposal submitted and accepted by the G-PAC in 2017. |

| Attachment 1: E121_Litvinov.pdf

|

|

| Attachment 2: E121_Approval.pdf

|

|

|

2

|

Mon Dec 3 15:06:04 2018 |

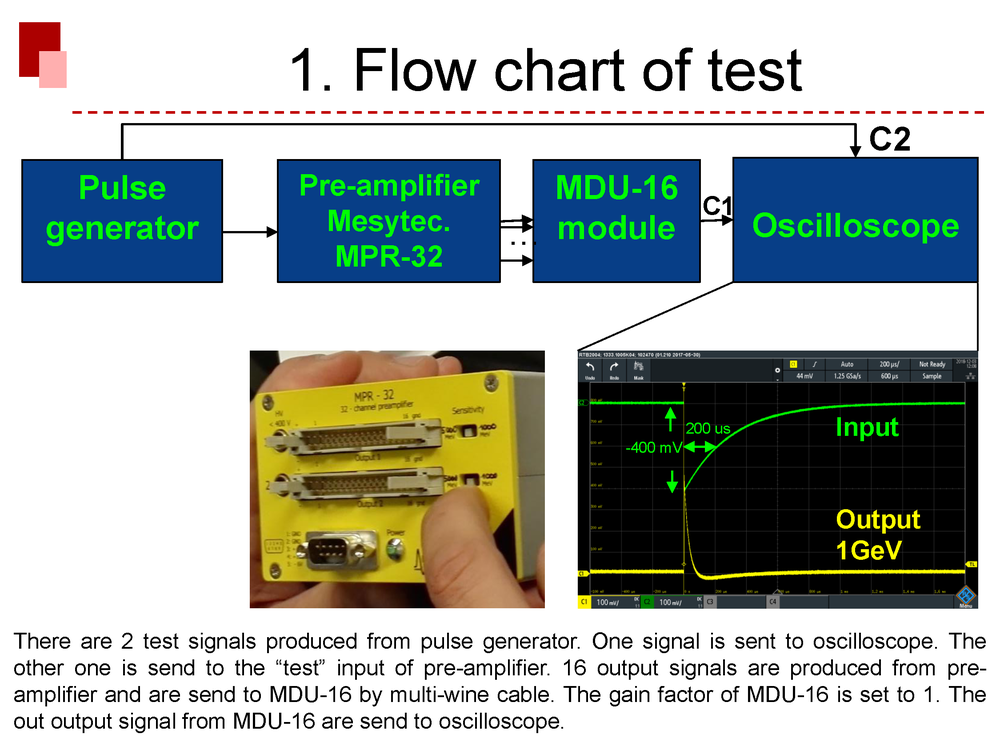

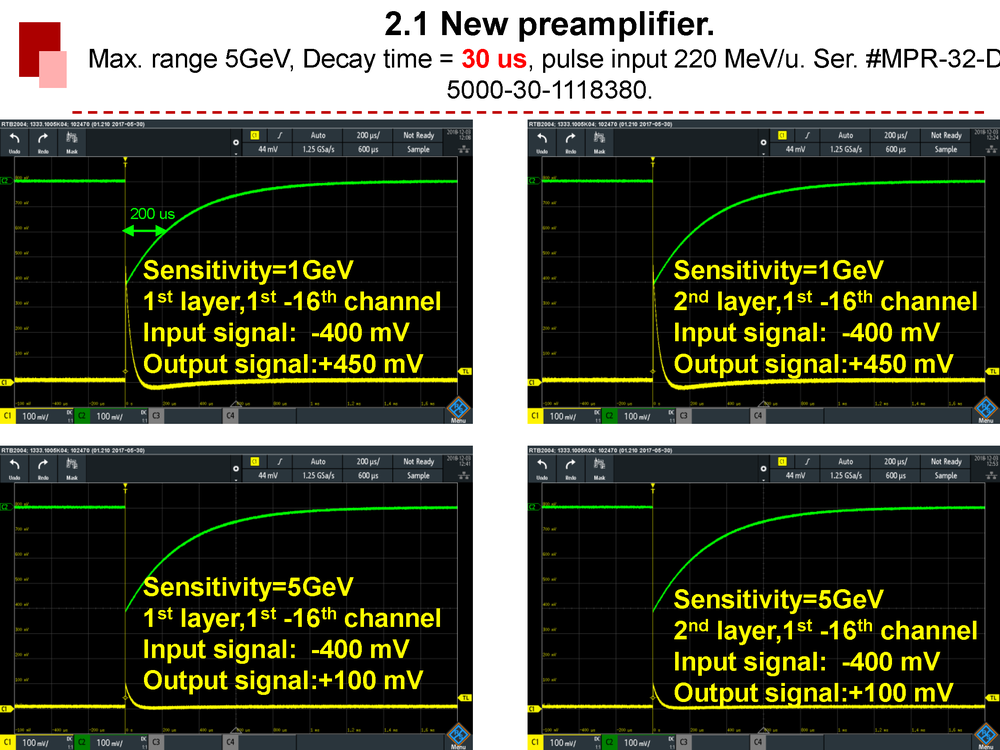

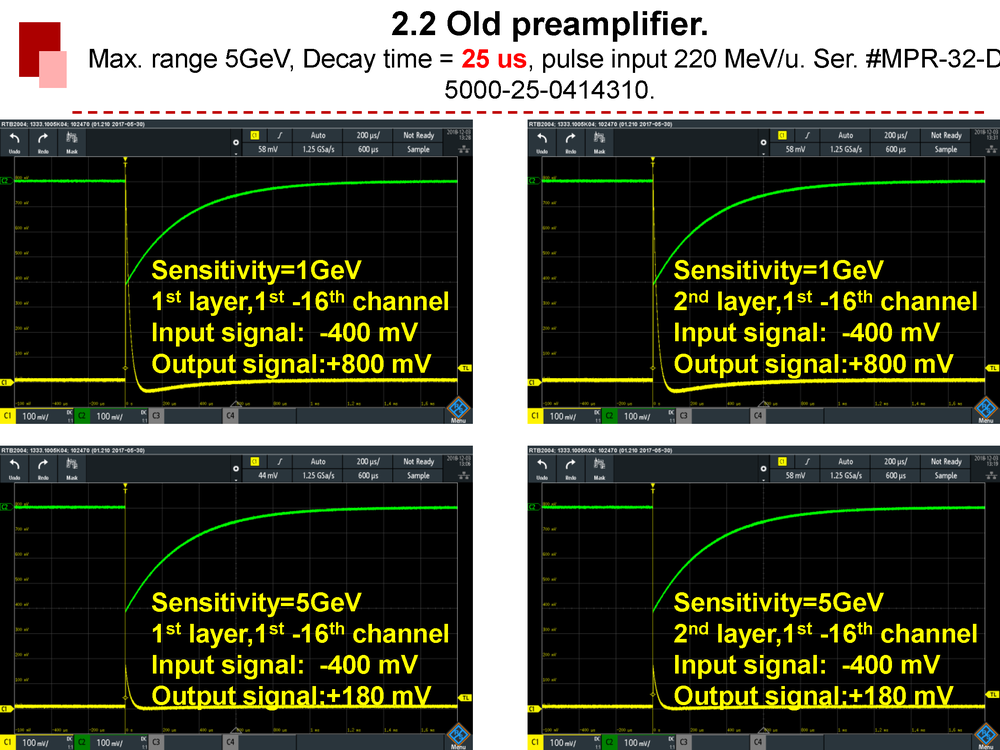

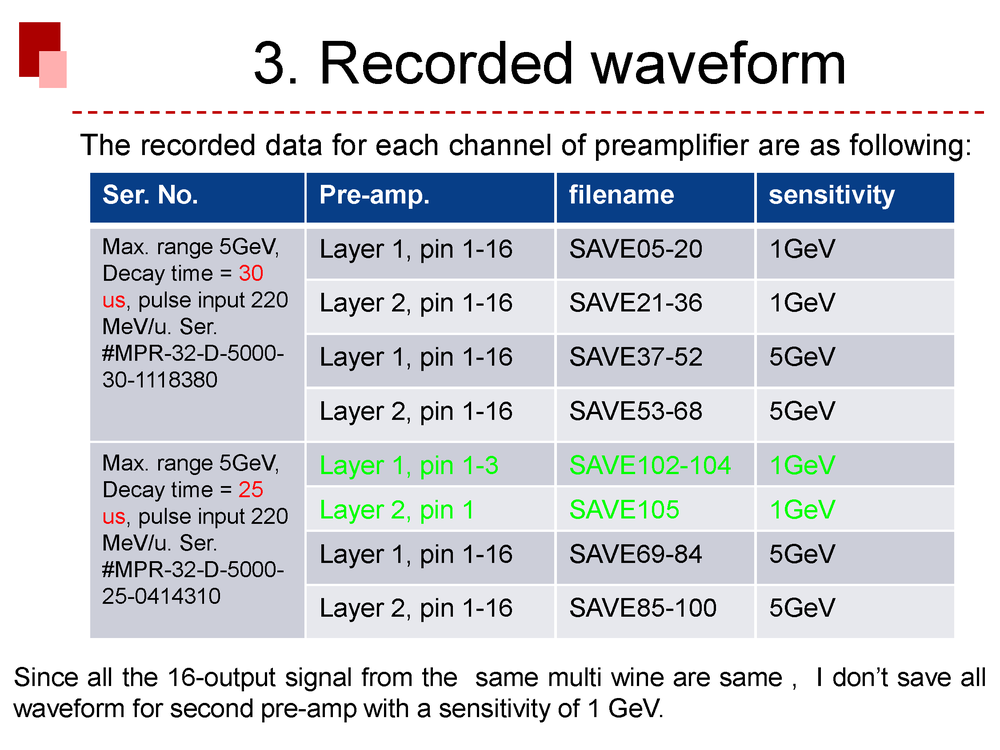

Chen, Sidhu | DAQ | Test of two preamplifier. | Description:

We have two pre-amplifiers:

New: Max. range 5GeV, Two sensitivity options: 1 GeV and 5 GeV, Decay time = 30 us, pulse input 220 MeV/u, Ser. #MPR-32-D-5000-30-1118380.

Old: Max. range 5GeV, Two sensitivity options: 1 GeV and 5 GeV, Decay time = 25 us, pulse input 220 MeV/u. Ser. #MPR-32-D-5000-25-0414310.

Conclusion:

Both pre-amplifiers work well.

The summary is attached in the followings:

|

|

7

|

Tue Mar 12 12:54:58 2019 |

Chen, Sidhu | DAQ | how to start DAQ and plot histogram. | 1. login litv-exp account

rchen@lxg1254:/data.local2/2002_238UIMS$ ssh -X litv-exp@lxg0155.gsi.de

(don't login on lx-pool.)

litv-exp@lx-pool.gsi.de's password: ViValasVegas@****

2.login r4l-47 account

litv-exp@lxi087:~$ ssh r4l-47

litv-exp@r4l-47's password:ViValasVegas@****

3.start mbs

R4L-47 litv-exp > mbs

mbs>

mbs> -R4L-47 :msg_log :Message logger running

3.1 Initilizing, show, start and stop the acq

mbs> @startup

-R4L-47  ispatch :Task "m_util" not started! ispatch :Task "m_util" not started!

mbs> @startup

-R4L-47 :util :task m_util started

-R4L-47 :util :setup file setup.usf successfully loaded

-R4L-47 :util :trigger module set up as MASTER, crate nr: 0

-R4L-47 :util :enabled interrupt

-R4L-47 :collector  ipe type 2 or 4: virtual mapping ipe type 2 or 4: virtual mapping

-R4L-47 :transport :task m_transport started

-R4L-47 :read_meb  ipe type 2 or 4: virtual mapping ipe type 2 or 4: virtual mapping

-R4L-47 :transport :starting server in inclusive mode

-R4L-47 :transport :waiting for client (port 6000)

mbs> -R4L-47 :read_meb :task m_read_meb started

-R4L-47 :stream_serv:task m_stream_serv started

-R4L-47 :collector :task m_collector started

mbs> show acq

-R4L-47  ispatch :Task "m_util" not started! ispatch :Task "m_util" not started!

mbs> show acq

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :ACQUISITION INITIALIZED 12-Mar-19 13:44:09: active tasks:

-R4L-47 :util :m_util m_transport m_daq_rate m_collector m_stream_serv

-R4L-47 :util :m_read_meb

-R4L-47 :util :SB setup LOADED from setup.usf.

-R4L-47 :util :Readout table NOT LOADED, acquisition STOPPED.

-R4L-47 :util :There are 32 streams with 32 buffers a 32768 each.

-R4L-47 :util :Current crate is 0, event builder is RIO4.

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Crate 0: ID= 20, LOCAL SYNC SYNC , subevent slots=200000.

-R4L-47 :util : trig 1: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 2: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 3: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 4: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 5: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 6: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 7: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 8: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 9: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 10: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 11: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 12: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 13: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 14: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 15: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Name of output device =

-R4L-47 :util :Tape label = , Dismounted, file CLOSED

-R4L-47 :util : 0.000 [MB] written to tape, 0.000 to file

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Collected: 0.0000 MB, 0 Buffers, 0 Events.

-R4L-47 :util :Rate : 0 KB/s, 0 Buffers/s, 0 Events/s

-R4L-47 :util :--------------------------------------------------------------

mbs> start acq

mbs> stop acq

-R4L-47 :util :stop acquisition

mbs> -R4L-47 :collector :acquisition NOT running

-R4L-47 :read_meb :found trig type 15 == stop acquisition

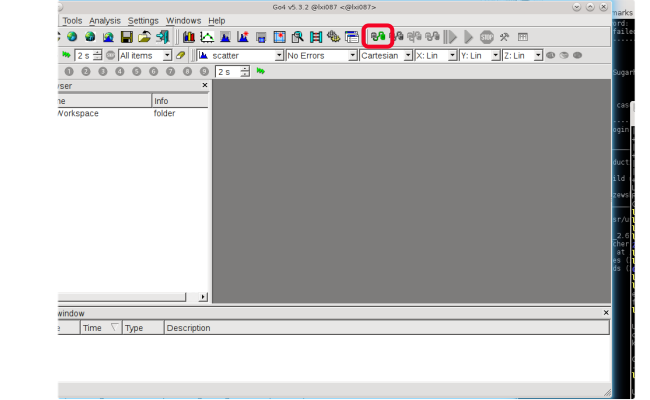

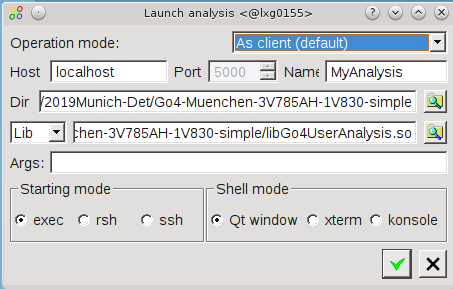

4. plot the histogram

litv-exp@lxi087:~/2019Munich-Det/Go4-Muenchen-3V785AH-1V830-simple$ go4

Go4 v5.3.2, build with ROOT 6.12/06 and Qt 4.8.6

Using Qt settings at /u/litv-exp/.config/GSI/go4.conf (default)

|

|

9

|

Tue May 28 08:36:14 2019 |

Jan | DAQ | MBS start & RFIO server | You need a DAQ-PC and the RIO crate computer.

All of the DAQ proceedures laid out here are operated from inside the DAQ screen session.

Right now for e121 the following DAQ-setup is used: (might change in the future)

DAQ-PC: lxg0155

screen session: e121_daq @ lxg0155

RIO: r4l-47

DAQ dir: /esr/usr/litv-exp/2019Munich-Det

The most important commands:

on DAQ-PC

mbs - start mbs DAQ

rawDispRFIO64 - start RFIO server

in MBS shell

@startup - initialize MBS (only inside DAQ dir)

@connect - connect RFIO server (only if server running)

@runstart - open file for data writing

@runstop - close file

start acq - start DAQ

show acq - status of DAQ

show file - status of current file/RFIO server

The full proceedure for the DAQ:

- on DAQ-PC enter screen session:

litv-exp@lxg____:~$ screen -x e121_daq or create new screen session if non is exisiting:litv-exp@lxg____:~$ screen -S e121_daq - inside screen: go to 1st tab (MBS) and login to RIO if not yet done:

<Ctrl-a 0>

litv-exp@lxg____:~$ ssh r4l-47

- on RIO reset and start MBS

R4L-47 litv-exp > cd 2019Munich-Det

R4L-47 litv-exp > resl

R4L-47 litv-exp > mbs

mbs > @startup

- inside screen go to 2nd tab (RFIO)

<Ctrl-a 1> or create 2nd tab if not exisiting<Ctrl-a c> - start RFIO server on DAQ-PC

litv-exp@lxg____:~$ cd /u/litv-exp/rfio

litv-exp@lxg____:~$ ./rawDispRFIO64-wheezy

-I- 64 bit RFIO test server (lxg0155) listening on port 1974

forks './rawServRFIO64-wheezy' for each client request - inside screen go to 1st tab and connect MBS to RFIO server

<Ctrl-a 0>

mbs > @connect

mbs> show file

mbs> -R4L-47 :transport :Name of output device = RFIO

-R4L-47 :transport :current tape label = lxg0155 , opened

-R4L-47 :transport :current file name = , closed

-R4L-47 :transport : 0.000 MBytes written to tape

-R4L-47 :transport : 0.000 MBytes written to current file - start acquisition

mbs > start acq

mbs > show acq

...

-R4L-47 :util :Name of output device = RFIO

-R4L-47 :util :RFIO server lxg0155, file CLOSED

-R4L-47 :util : 0.000 [MB] written to tape, 0.000 to file

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Collected: 61.1451 MB, 1866 Buffers, 131990 Events.

-R4L-47 :util :Rate : 33 KB/s, 1 Buffers/s, 71 Events/s

-R4L-47 :util :-------------------------------------------------------------- - open file / start a run

mbs > @runstart

-R4L-47 :transport :open file at server lxg0155::

-R4L-47 :transport :/data.local1/E121/predata/e121_run_1239.lmd - close file / stop a run

mbs > @runstop

-R4L-47 :transport :Rfio server lxg0155: closed file after 0.262 MB written:

-R4L-47 :transport :-I- remote output file /data.local1/E121/predata/e121_run_1239.lmd closed

mbs> -R4L-47 :transport :/data.local1/E121/predata/e121_run_1239.lmd

|

|