| ID |

Date |

Author |

Category |

Subject |

|

10

|

Wed Jun 26 16:20:31 2019 |

Jan | DAQ | unpacker: lmd > root | I have written an unpacker for the lmd data taken with the current daq-system for E121.

The crate configuration is as follows:

ADC1 channels 1-32 (Caen 785)

ADC2 channels 1-32 (Caen 785)

ADC3 channels 1-32 (Caen 785)

SCALER channels 1-32 (Caen 830)

The unpacker binary can be found here

/u/litv-exp/unpacker/unpackexps/E121/E121

The current spec file is attached.

To convert lmd-files to root-files, please use it as follows:litv-exp@lxg___: E121_unpacker /path/to/file.lmd --ntuple=RAW,/path/to/new_file.root |

| Attachment 1: E121.spec

|

// -*- C++ -*-

ADC(start)

{

MEMBER(DATA12 data[32]);

list(0 <= ch < 32)

{

UINT32 item NOENCODE

{

0_15: channel;

16_27: value;

28_31: 0;

ENCODE(data[channel - start], (value=value));

}

}

}

SCALER(start)

{

MEMBER(DATA32 data[32]);

list(0 <= ch < 32)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel / 2) - start], (value=(high.value << 16) | low.value));

}

}

SUBEVENT(ESR)

{

adc[0] = ADC(start = 0);

adc[1] = ADC(start = 32);

adc[2] = ADC(start = 64);

select optional {

scaler[0] = SCALER(start = 0x100);

}

}

EVENT

{

esr = ESR(type = 10, subtype = 1);

}

#include "det_mapping.hh"

|

| Attachment 2: det_mapping.hh

|

SIGNAL( ADC1_1, esr.adc[0].data[0],

ADC1_32, esr.adc[0].data[31], DATA12);

SIGNAL( ADC2_1, esr.adc[1].data[0],

ADC2_32, esr.adc[1].data[31], DATA12);

SIGNAL( ADC3_1, esr.adc[2].data[0],

ADC3_32, esr.adc[2].data[31], DATA12);

//SIGNAL( SC_1, esr.scaler[0].data[0],

// SC_32, esr.scaler[0].data[31],DATA32);

|

|

15

|

Tue Feb 25 15:48:31 2020 |

ruijiu chen | DAQ | Important folders of e121 eperiments: | 1. slow control:

1.1. program file:

litv-exp@ringpi:~/epics/mrcc_ioc/db $

1.2 user interface:

litv-exp@lxg1298:~/E121/scripts/GUIe121_new

2. mbs:

2.1 user interface

litv-exp@lxg1298:~/E121/scripts$ ./e121_gui.py

2.2 source

R4L-47 litv-exp > pwd

/esr/usr/litv-exp/2020_e121/

3. go4:

litv-exp@lxg1298:~/2019Munich-Det/Go4-Muenchen-3V785AH-1V830-simple$ go4

4. experimenal data:

litv-exp@lxg1298:/data.local1/E121 |

|

16

|

Tue Feb 25 15:49:58 2020 |

ruijiu chen | DAQ | changing scaling factor. | How to change scaling factor?

The parameters is in f_user.c file:

1. open the f_user.C with emacs :

R4L-47 litv-exp > emacs -nw f_user.c

2. change the parameters "MWPC_downscale".

#define MWPC_downscale 0 // reduction = 2**MWPC_downscale

3.compile the program.

4. restart mbs. |

|

33

|

Sat Mar 28 12:19:21 2020 |

Ragan, RuiJiu | DAQ | Change of the polarity of Amplifiers | Since last night, the signals from the p-side of all the Si pads were seen as negative on picoscope.

The signals from DSSSD, all n-sides of Si pads and CsI were positive which all are in MSCF-5.

Thus, I and RuiJiu, changed the polarity jumpers of MSCF 1,2,3 and 4(all the four jumpers inside the mentioned MSCF) and now hope to see positive signals from the p-side of all the Si pads. |

| Attachment 1: 7888530B-DE66-4D37-A0A8-933307DD2AB8.MOV

|

|

37

|

Sat Mar 28 15:07:40 2020 |

ruijiu | DAQ | start run | |

|

41

|

Sat Mar 28 16:12:25 2020 |

ruijiu, ragan | DAQ | enter ESR and turn on the HV crate. | |

|

44

|

Sun Mar 29 09:40:35 2020 |

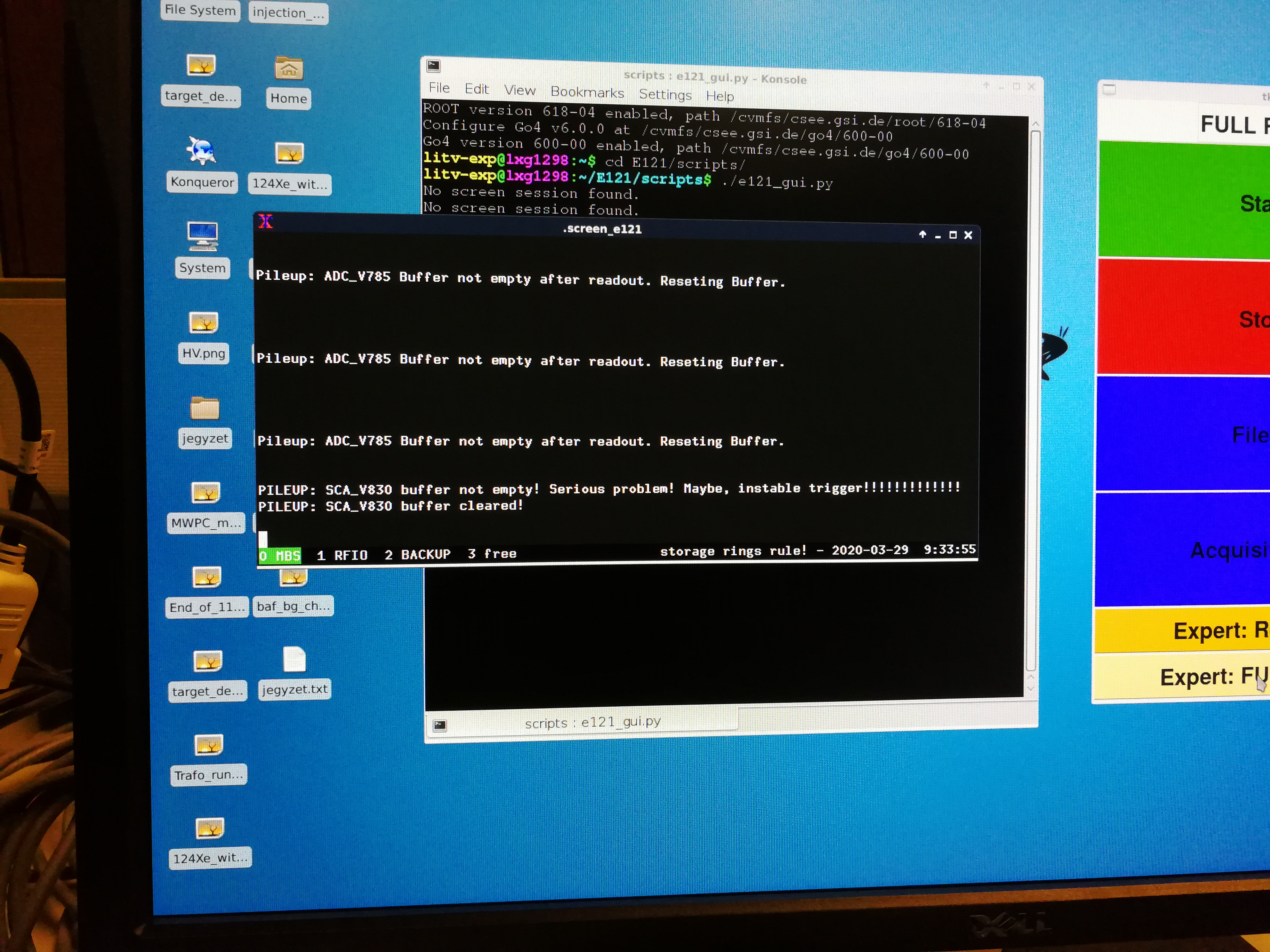

ruijiu | DAQ | restart go4 | go4 crush up.

the problem is

due to mbs.

restart mbs.

see an error.

restart again.

the mbs and go4

are working

working. |

| Attachment 1: IMG_20200329_093354.jpg

|

|

|

51

|

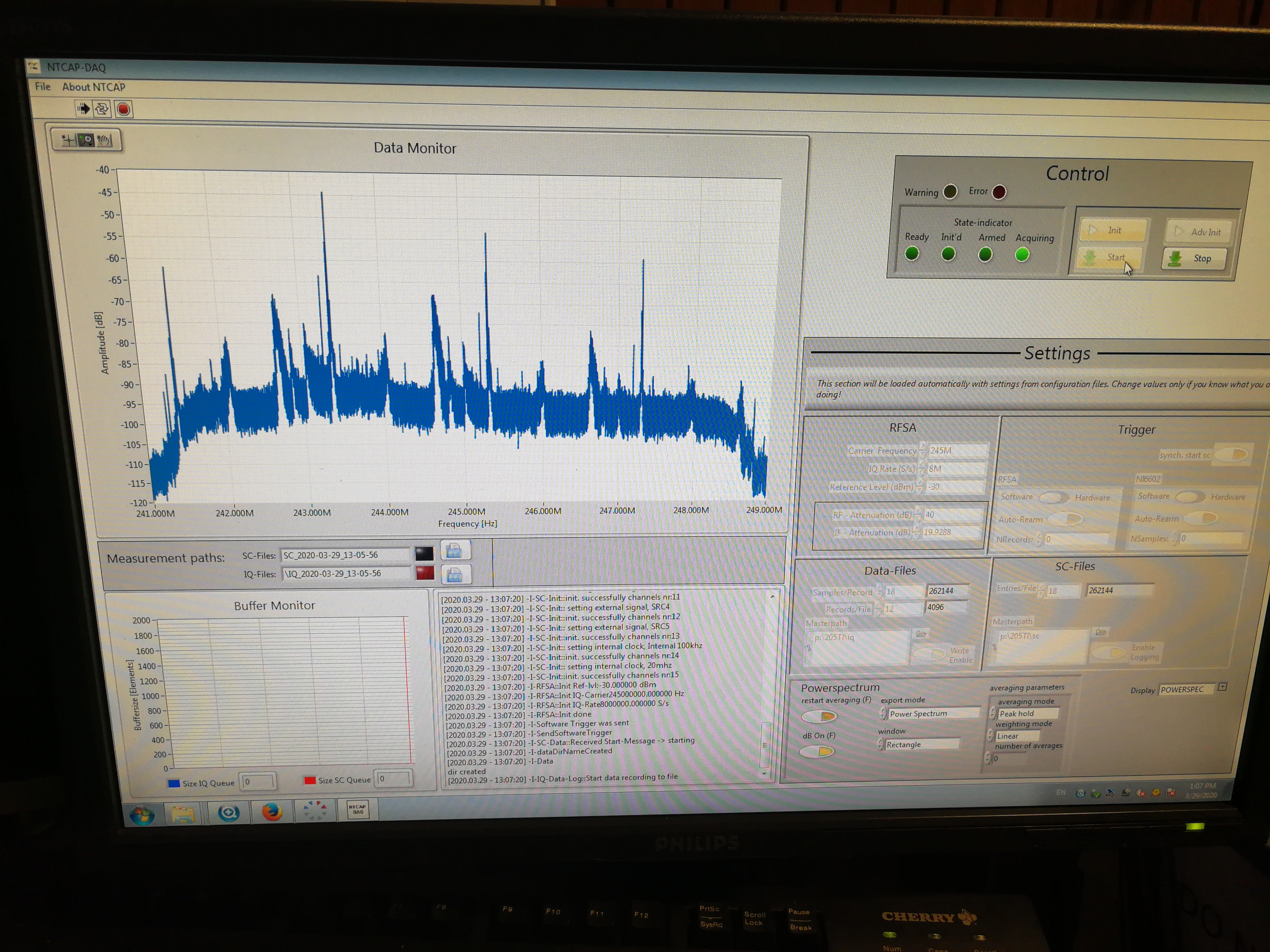

Sun Mar 29 13:05:36 2020 |

ruijiu | DAQ | start ntcap | IQ_2020-03-29_13-05-

56

SC_2020-03-29_13-05-

56 |

| Attachment 1: IMG_20200329_130438.jpg

|

|

|

98

|

Mon Mar 30 14:24:46 2020 |

ruijiu | DAQ | stop taking data. | 1. stop run0272.lmd.

2. stop NTCAP.

NTCAp file:

SC_2020-03-30_09-28-14

IQ_2020-03-30_09-28-14

(saved in drive: p) |

|

175

|

Thu Oct 1 22:20:03 2020 |

Jan | DAQ | final unpacker config | We identified an issue with randomly missing adc channels in all lmd-files before run 0273.

This led to errors in the unpacking process.

This issue is solved with the new config and mapping for the unpacker.

The respective files are attached here.

The unpacker is ready to use in /u/litv-exp/unpacker/unpackexps/E121

The adc issue is also understood. We deactivated the internal adc thresholds during the experiment, because we encountered the very same unpacker errors. This solved the problem for all later runs, but we forgot to think about a solution for the earlier runs.

Mea culpa.

Jan |

| Attachment 1: E121.spec

|

// -*- C++ -*-

ADC_CH(start, id)

{

MEMBER(DATA12 data[96]);

UINT32 item NOENCODE

{

0_15: channel = MATCH(id);

16_27: value;

28_31: unknown;

ENCODE(data[channel - start], (value=value));

}

}

SCALER(start)

{

MEMBER(DATA32 data[32]);

list(0 <= ch < 32)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel - start) / 2], (value=(high.value << 16) | low.value));

}

}

TDC(start)

{

MEMBER(DATA32 data);

UINT32 high NOENCODE

{

0_15: channel = MATCH(start);

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data,(value=(high.value << 16) | low.value));

}

TBOX(start)

{

MEMBER(DATA32 data[16]);

list(0 <= ch < 16)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel - start) / 2], (value=(high.value << 16) | low.value));

}

}

SUBEVENT(ESR)

{

tb_in[0] = TBOX(start = 0x300);

tb_inhibit[0] = TBOX(start = 0x380);

tb_red[0] = TBOX(start = 0x400);

// adc[0] = ADC(start = 0);

// adc[1] = ADC(start = 32);

// adc[2] = ADC(start = 64);

select several {

adc[0] = ADC_CH(start = 0 , id = 0);

adc[0] = ADC_CH(start = 0 , id = 1);

adc[0] = ADC_CH(start = 0 , id = 2);

adc[0] = ADC_CH(start = 0 , id = 3);

adc[0] = ADC_CH(start = 0 , id = 4);

adc[0] = ADC_CH(start = 0 , id = 5);

adc[0] = ADC_CH(start = 0 , id = 6);

adc[0] = ADC_CH(start = 0 , id = 7);

adc[0] = ADC_CH(start = 0 , id = 8);

adc[0] = ADC_CH(start = 0 , id = 9);

adc[0] = ADC_CH(start = 0 , id = 10);

adc[0] = ADC_CH(start = 0 , id = 11);

adc[0] = ADC_CH(start = 0 , id = 12);

adc[0] = ADC_CH(start = 0 , id = 13);

adc[0] = ADC_CH(start = 0 , id = 14);

adc[0] = ADC_CH(start = 0 , id = 15);

adc[0] = ADC_CH(start = 0 , id = 16);

adc[0] = ADC_CH(start = 0 , id = 17);

adc[0] = ADC_CH(start = 0 , id = 18);

adc[0] = ADC_CH(start = 0 , id = 19);

adc[0] = ADC_CH(start = 0 , id = 20);

adc[0] = ADC_CH(start = 0 , id = 21);

adc[0] = ADC_CH(start = 0 , id = 22);

adc[0] = ADC_CH(start = 0 , id = 23);

adc[0] = ADC_CH(start = 0 , id = 24);

adc[0] = ADC_CH(start = 0 , id = 25);

adc[0] = ADC_CH(start = 0 , id = 26);

adc[0] = ADC_CH(start = 0 , id = 27);

adc[0] = ADC_CH(start = 0 , id = 28);

adc[0] = ADC_CH(start = 0 , id = 29);

adc[0] = ADC_CH(start = 0 , id = 30);

adc[0] = ADC_CH(start = 0 , id = 31);

adc[1] = ADC_CH(start = 32, id = 32);

adc[1] = ADC_CH(start = 32, id = 33);

adc[1] = ADC_CH(start = 32, id = 34);

adc[1] = ADC_CH(start = 32, id = 35);

adc[1] = ADC_CH(start = 32, id = 36);

adc[1] = ADC_CH(start = 32, id = 37);

adc[1] = ADC_CH(start = 32, id = 38);

adc[1] = ADC_CH(start = 32, id = 39);

adc[1] = ADC_CH(start = 32, id = 40);

adc[1] = ADC_CH(start = 32, id = 41);

adc[1] = ADC_CH(start = 32, id = 42);

adc[1] = ADC_CH(start = 32, id = 43);

adc[1] = ADC_CH(start = 32, id = 44);

adc[1] = ADC_CH(start = 32, id = 45);

adc[1] = ADC_CH(start = 32, id = 46);

adc[1] = ADC_CH(start = 32, id = 47);

adc[1] = ADC_CH(start = 32, id = 48);

adc[1] = ADC_CH(start = 32, id = 49);

adc[1] = ADC_CH(start = 32, id = 50);

adc[1] = ADC_CH(start = 32, id = 51);

adc[1] = ADC_CH(start = 32, id = 52);

adc[1] = ADC_CH(start = 32, id = 53);

adc[1] = ADC_CH(start = 32, id = 54);

adc[1] = ADC_CH(start = 32, id = 55);

adc[1] = ADC_CH(start = 32, id = 56);

adc[1] = ADC_CH(start = 32, id = 57);

adc[1] = ADC_CH(start = 32, id = 58);

adc[1] = ADC_CH(start = 32, id = 59);

adc[1] = ADC_CH(start = 32, id = 60);

adc[1] = ADC_CH(start = 32, id = 61);

adc[1] = ADC_CH(start = 32, id = 62);

adc[1] = ADC_CH(start = 32, id = 63);

adc[2] = ADC_CH(start = 64, id = 64);

adc[2] = ADC_CH(start = 64, id = 65);

adc[2] = ADC_CH(start = 64, id = 66);

adc[2] = ADC_CH(start = 64, id = 67);

adc[2] = ADC_CH(start = 64, id = 68);

adc[2] = ADC_CH(start = 64, id = 69);

adc[2] = ADC_CH(start = 64, id = 70);

adc[2] = ADC_CH(start = 64, id = 71);

adc[2] = ADC_CH(start = 64, id = 72);

adc[2] = ADC_CH(start = 64, id = 73);

adc[2] = ADC_CH(start = 64, id = 74);

adc[2] = ADC_CH(start = 64, id = 75);

adc[2] = ADC_CH(start = 64, id = 76);

adc[2] = ADC_CH(start = 64, id = 77);

adc[2] = ADC_CH(start = 64, id = 78);

adc[2] = ADC_CH(start = 64, id = 79);

adc[2] = ADC_CH(start = 64, id = 80);

adc[2] = ADC_CH(start = 64, id = 81);

adc[2] = ADC_CH(start = 64, id = 82);

adc[2] = ADC_CH(start = 64, id = 83);

adc[2] = ADC_CH(start = 64, id = 84);

adc[2] = ADC_CH(start = 64, id = 85);

adc[2] = ADC_CH(start = 64, id = 86);

adc[2] = ADC_CH(start = 64, id = 87);

adc[2] = ADC_CH(start = 64, id = 88);

adc[2] = ADC_CH(start = 64, id = 89);

adc[2] = ADC_CH(start = 64, id = 90);

adc[2] = ADC_CH(start = 64, id = 91);

adc[2] = ADC_CH(start = 64, id = 92);

adc[2] = ADC_CH(start = 64, id = 93);

adc[2] = ADC_CH(start = 64, id = 94);

adc[2] = ADC_CH(start = 64, id = 95);

}

select optional {

scaler[0] = SCALER(start = 0x100);

}

select several {

tdc[0] = TDC(start = 0x200);

tdc[1] = TDC(start = 0x202);

tdc[2] = TDC(start = 0x204);

tdc[3] = TDC(start = 0x206);

tdc[4] = TDC(start = 0x208);

tdc[5] = TDC(start = 0x20a);

tdc[6] = TDC(start = 0x20c);

tdc[7] = TDC(start = 0x20e);

tdc[8] = TDC(start = 0x210);

tdc[9] = TDC(start = 0x212);

}

}

EVENT

{

esr = ESR(type = 10, subtype = 1);

}

#include "det_mapping.hh"

|

| Attachment 2: det_mapping.hh

|

SIGNAL( ADC1_1, esr.adc[0].data[0],

ADC1_32, esr.adc[0].data[31], DATA12);

SIGNAL( ADC2_1, esr.adc[1].data[0],

ADC2_32, esr.adc[1].data[31], DATA12);

SIGNAL( ADC3_1, esr.adc[2].data[0],

ADC3_32, esr.adc[2].data[31], DATA12);

SIGNAL( SC_1, esr.scaler[0].data[0],

SC_32, esr.scaler[0].data[31],DATA32);

SIGNAL( TDC_1, esr.tdc[0].data,

TDC_10, esr.tdc[9].data,DATA32);

SIGNAL( TB_SI_IN, esr.tb_in[0].data[0],DATA32);

SIGNAL( TB_SI_RED, esr.tb_red[0].data[0],DATA32);

SIGNAL( TB_MWPC_IN, esr.tb_in[0].data[1],DATA32);

SIGNAL( TB_MWPC_RED, esr.tb_red[0].data[1],DATA32);

|

|

176

|

Mon Nov 2 16:45:55 2020 |

Jan | DAQ | f_user & mbslog | Attached is the f_user.c and the mbslog.l files.

The readout function is for the following setup:

3x ADC CAEN V785

1x SCA CAEN V830

1x TDC CAEN V1190

1x Vulom TRB5 (triggerbox)

1x Vulom4b PEV (priority encoder)

1x TRIVA7

1x RIO4 R4L-47 |

| Attachment 1: f_user.c

|

/* CAEN V785 32 channel ADC*/

#include "stdio.h"

#include "s_veshe.h"

//----------------------------------------------

#define MWPC_downscale 0 // reduction = 2**MWPC_downscale

#define SI_downscale 0

#define VME_BASE 0x00000000

#define TB__OFFSET 0x05000000

#define TB__No_Ch 16

#define TB__No_Ch_enabled 16

#define TB__lmd_offset 0x300

#define ADC_V785__VME_OFFSET 0x00200000

#define ADC_V785__VME_SIZE 0x10000

#define ADC_V785__No_Ch 32

#define ADC_V785__lmd_offset 0x00

#define ADC_V785__No_Mod 3

#define SCA_V830_VME_OFFSET 0x00000000

#define SCA_V830_VME_SIZE 0x10000

#define SCA_V830__No_Ch 32

#define SCA_V830__lmd_offset 0x100

#define TDC_V1190a__OFFSET 0x01200000

#define TDC_V1190a__VME_SIZE 0x10000

#define TDC_V1190a__No_Ch 128

#define TDC_V1190a__No_hit_per_Ch 1 //only single hit allowed

#define TDC_V1190a__lmd_offset 0x200

#define TDC_V1190a__win_width 200

#define TDC_V1190a__win_offset -180

const long TB_Ch_enable_reg_F_0 = 0x00FF ;

//------------//

// scale down: ch00, ch01, ch02

const long TB_scale_down_0_F[TB__No_Ch] ={ SI_downscale,MWPC_downscale,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

const long ADC_threshold_value = 0x0000 ;

/*****************************************************************************/

/*

* all pointer wllhich are used for read/write operations in the functions

* f_user_init and f_user_readout must be defined here as static variables

*/

static long volatile *pl_VME_virtual_mem_base ;

static long volatile *pl_trig_vme_str; // triva status register

static long ll_evt_ctr = 0;

/* TB - Triggerbox on Vulom3 */

static long volatile *pl_TB__base ;

static long volatile *pl_TB__Ch_enable_reg_F_0 ;

static long volatile *pl_TB__scale_down_7_0 ;

static long volatile *pl_TB__scale_down_F_8 ;

static long volatile *pl_TB__latch_reg ;

static long volatile *pl_TB__version ;

static long volatile *pl_TB__scaler_inp [TB__No_Ch];

static long volatile *pl_TB__scaler_inhib [TB__No_Ch] ;

static long volatile *pl_TB__scaler_after_reduction [TB__No_Ch] ;

long TB__scaler_inp_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

long TB__scaler_inhib_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

long TB__scaler_after_reduction_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

/* ADC - Analog to Digital Converter CAEN V785AH */

static long volatile *pl_ADC_V785__base [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__firm_rev [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__geo_adr [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__oui_msb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__oui [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__oui_lsb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__version [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id_msb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id_lsb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__revision [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__serial_msb [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__serial_lsb [ADC_V785__No_Mod];

static long volatile *pl_ADC_V785__outp_buffer [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_set_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_clr_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__stat_reg_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__ctrl_reg_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__stat_reg_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_set_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_clr_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__threshs[ADC_V785__No_Ch] [ADC_V785__No_Mod];

/* SCA - Scaler CAEN V830 */

static long volatile *pl_SCA_V830__base;

static long volatile *pl_SCA_V830__outp_buffer;

static long volatile *pl_SCA_V830__counter[SCA_V830__No_Ch];

static short volatile *ps_SCA_V830__scaler_clr;

static short volatile *ps_SCA_V830__scaler_status_reg;

static short volatile *ps_SCA_V830__fixed_code;

static short volatile *ps_SCA_V830__manuf_mod_type;

static short volatile *ps_SCA_V830__version_series;

static short volatile *ps_SCA_V830__firm_rev;

static short volatile *ps_SCA_V830__geo_adr;

static short volatile *ps_SCA_V830__oui_msb ;

static short volatile *ps_SCA_V830__oui ;

static short volatile *ps_SCA_V830__oui_lsb ;

static short volatile *ps_SCA_V830__version ;

static short volatile *ps_SCA_V830__board_id_msb ;

static short volatile *ps_SCA_V830__board_id ;

static short volatile *ps_SCA_V830__board_id_lsb ;

static short volatile *ps_SCA_V830__revision ;

static short volatile *ps_SCA_V830__serial_msb;

static short volatile *ps_SCA_V830__serial_lsb;

static short volatile *ps_SCA_V830__bit_set_1 ;

static short volatile *ps_SCA_V830__bit_clr_1 ;

static short volatile *ps_SCA_V830__stat_reg_1;

static short volatile *ps_SCA_V830__ctrl_reg_1;

static short volatile *ps_SCA_V830__sw_clr_reg ;

long SCA_V830__data_old [SCA_V830__No_Ch] ;

/* TDC - Time to Digital Converter CAEN V1190a */

static long volatile *pl_TDC_V1190a__base ;

static long volatile *pl_TDC_V1190a__outp_buffer ;

static short volatile *ps_TDC_V1190a__ctrl_reg_1 ;

static short volatile *ps_TDC_V1190a__stat_reg_1 ;

static short volatile *ps_TDC_V1190a__geo_adr ;

static short volatile *ps_TDC_V1190a__module_reset ;

static short volatile *ps_TDC_V1190a__sw_clr ;

static short volatile *ps_TDC_V1190a__sw_evt_reset ;

static short volatile *ps_TDC_V1190a__sw_trig ;

static short volatile *pl_TDC_V1190a__evt_cnt ;

static short volatile *ps_TDC_V1190a__firmware_rev ;

static short volatile *ps_TDC_V1190a__micro_reg ;

static short volatile *ps_TDC_V1190a__micro_hdshk_reg ;

static short volatile *ps_TDC_V1190a__oui_2 ;

static short volatile *ps_TDC_V1190a__oui_1 ;

static short volatile *ps_TDC_V1190a__oui_0 ;

static short volatile *ps_TDC_V1190a__board_ver ;

static short volatile *ps_TDC_V1190a__board_id_2 ;

static short volatile *ps_TDC_V1190a__board_id_1 ;

static short volatile *ps_TDC_V1190a__board_id_0 ;

static short volatile *ps_TDC_V1190a__revision_3 ;

static short volatile *ps_TDC_V1190a__revision_2 ;

static short volatile *ps_TDC_V1190a__revision_1 ;

static short volatile *ps_TDC_V1190a__revision_0 ;

static short volatile *ps_TDC_V1190a__serial_1 ;

static short volatile *ps_TDC_V1190a__serial_0 ;

int l_mod;

int l_ch;

long l_event_counter;

/*****************************************************************************/

/*****************************************************************************/

int f_user_get_virt_ptr (long *pl_loc_hwacc, long pl_rem_cam[])

{

int i;

long l_i, l_j;

/*

* create virtual pointer to be used in f_user_init and f_user_readout

*/

l_event_counter = 0;

//***************

// CAEN mapping

//***************

{ //#ifdef CAEN

pl_VME_virtual_mem_base = (long*) ((long)pl_loc_hwacc) ;

} //#endif // CAEN

// *****************************************************************************/

{

// * create virtual pointer to be used in f_user_init and f_user_readout

/*------------------------------------------------------------------------------*/

/* TB on VULOM3 */

/*------------------------------------------------------------------------------*/

{

pl_TB__base = (long*) ((long) pl_VME_virtual_mem_base + TB__OFFSET ) ;

pl_TB__Ch_enable_reg_F_0 = (long*) ( (long) pl_TB__base + 0x0000 );

pl_TB__scale_down_7_0 = (long*) ( (long) pl_TB__base + 0x0004 );

pl_TB__scale_down_F_8 = (long*) ( (long) pl_TB__base + 0x0008 ) ;

pl_TB__latch_reg = (long*) ( (long) pl_TB__base + 0x000c );

pl_TB__version = (long*) ( (long) pl_TB__base + 0x003c );

long l_ch ;

for (l_ch=0; l_ch<TB__No_Ch; l_ch++)

{ pl_TB__scaler_inp[l_ch] =

(long*) ( (long) pl_TB__base + 0x0040 +(l_ch*4));

pl_TB__scaler_inhib[l_ch] =

(long*) ( (long) pl_TB__base + 0x0080 +(l_ch*4));

pl_TB__scaler_after_reduction[l_ch] =

(long*) ( (long) pl_TB__base + 0x00c0 +(l_ch*4));

}

}

/*------------------------------------------------------------------------------*/

/* ADC CAEN 785AH */

/*------------------------------------------------------------------------------*/

for (l_mod = 0 ; l_mod < ADC_V785__No_Mod; l_mod++)

{

pl_ADC_V785__base[l_mod] = (long*) ( (long) pl_VME_virtual_mem_base + ADC_V785__VME_OFFSET + l_mod * ADC_V785__VME_SIZE) ;

ps_ADC_V785__firm_rev[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1000 );

ps_ADC_V785__geo_adr[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1002 );

ps_ADC_V785__oui_msb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8026 );

ps_ADC_V785__oui[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802a );

ps_ADC_V785__oui_lsb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802e );

ps_ADC_V785__version[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8032 );

ps_ADC_V785__board_id_msb[l_mod]= (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8036 );

ps_ADC_V785__board_id[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802a );

ps_ADC_V785__board_id_lsb[l_mod]= (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802e );

ps_ADC_V785__revision[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x804e );

ps_ADC_V785__serial_msb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8f02 );

ps_ADC_V785__serial_lsb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8f06 );

pl_ADC_V785__outp_buffer[l_mod]= (long*) ( (long) pl_ADC_V785__base[l_mod] + 0x0000 );

ps_ADC_V785__bit_set_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1006 );

ps_ADC_V785__bit_clr_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1008 );

ps_ADC_V785__stat_reg_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x100e );

ps_ADC_V785__ctrl_reg_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1010 );

ps_ADC_V785__stat_reg_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1022 );

ps_ADC_V785__bit_set_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1032 );

ps_ADC_V785__bit_clr_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1034 );

for (l_ch=0; l_ch<ADC_V785__No_Ch; l_ch++)

{

ps_ADC_V785__threshs[l_ch][l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1080 + l_ch * 0x0002 );

}

}

/*------------------------------------------------------------------------------*/

/* Scaler CAEN V830 */

... 832 more lines ...

|

| Attachment 2: mbslog.l

|

22-Oct-18 16:39:14#R4-54 :msg_log :Message logger running

22-Oct-18 16:39:21+R4-54 :dispatch :>>> Start procedure "startup.scom" break mode 1

22-Oct-18 16:39:21#R4-54 :dispatch :start task m_util

22-Oct-18 16:39:22#R4-54 :util :task m_util started

22-Oct-18 16:39:22#R4-54 :util :load setup setup.usf

22-Oct-18 16:39:22#R4-54 :util :setup file setup.usf successfully loaded

22-Oct-18 16:39:22+R4-54 :util :load setup finished (x0)

22-Oct-18 16:39:22#R4-54 :util :set trig_mod

22-Oct-18 16:39:22#R4-54 :util :trigger module set up as MASTER, crate nr: 0

22-Oct-18 16:39:22+R4-54 :util :set trig_mod finished (x0)

22-Oct-18 16:39:22#R4-54 :util :enable irq

22-Oct-18 16:39:23+R4-54 :util :enable irq finished (x0)

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_read_meb "./m_read_meb"

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_collector

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_transport

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_stream_serv

22-Oct-18 16:39:24#R4-54 :dispatch :start task m_daq_rate

22-Oct-18 16:39:26!R4-54 :read_meb :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:39:27!R4-54 :collector :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:39:27#R4-54 :read_meb :task m_read_meb started

22-Oct-18 16:39:27#R4-54 :stream_serv:task m_stream_serv started

22-Oct-18 16:39:27#R4-54 :collector :task m_collector started

22-Oct-18 16:39:27#R4-54 :transport :task m_transport started

22-Oct-18 16:39:27#R4-54 :transport :enable tcp

22-Oct-18 16:39:27#R4-54 :transport :starting server in inclusive mode

22-Oct-18 16:39:27+R4-54 :transport :enable tcp finished (x0)

22-Oct-18 16:39:27+R4-54 :dispatch :>>> End procedure "startup.scom"

22-Oct-18 16:39:27#R4-54 :transport :waiting for client (port 6000)

22-Oct-18 16:39:30#R4-54 :util :start acquisition

22-Oct-18 16:39:30+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:39:31#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:39:31#R4-54 :collector :acquisition running

22-Oct-18 16:42:19#R4-54 :util :stop acquisition

22-Oct-18 16:42:21+R4-54 :util :stop acquisition finished (x0)

22-Oct-18 16:42:21#R4-54 :collector :acquisition NOT running

22-Oct-18 16:42:21#R4-54 :read_meb :found trig type 15 == stop acquisition

22-Oct-18 16:45:08#R4-54 :util :start acquisition

22-Oct-18 16:45:08+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:45:09#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:45:10#R4-54 :collector :acquisition running

22-Oct-18 16:45:19!R4-54 :dispatch :Key "events" > invalid value "v"!

22-Oct-18 16:45:19!R4-54 :dispatch :Command not executed

22-Oct-18 16:45:19!R4-54 :dispatch :Command "type event v 10" finished with argument error (20)

22-Oct-18 16:45:34#R4-54 :transport :type event -v 10

22-Oct-18 16:45:34+R4-54 :transport :type event finished (x0)

22-Oct-18 16:45:41#R4-54 :util :stop acquisition

22-Oct-18 16:45:43+R4-54 :util :stop acquisition finished (x0)

22-Oct-18 16:45:43#R4-54 :collector :acquisition NOT running

22-Oct-18 16:45:43#R4-54 :read_meb :found trig type 15 == stop acquisition

22-Oct-18 16:45:52#R4-54 :util :start acquisition

22-Oct-18 16:45:52+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:45:52#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:45:53#R4-54 :collector :acquisition running

22-Oct-18 16:46:36#R4-54 :transport :type event -v 10

22-Oct-18 16:46:36+R4-54 :transport :type event finished (x0)

22-Oct-18 16:52:38#R4-54 :stream_serv:140.181.81.77 connected

22-Oct-18 16:55:03!R4-54 :stream_serv:received CLOSE, client disconnected!

22-Oct-18 16:55:25#R4-54 :msg_log :Message logger running

22-Oct-18 16:58:29+R4-54 :dispatch :>>> Start procedure "startup.scom" break mode 1

22-Oct-18 16:58:29#R4-54 :dispatch :start task m_util

22-Oct-18 16:58:30#R4-54 :util :task m_util started

22-Oct-18 16:58:30#R4-54 :util :load setup setup.usf

22-Oct-18 16:58:30#R4-54 :util :setup file setup.usf successfully loaded

22-Oct-18 16:58:30+R4-54 :util :load setup finished (x0)

22-Oct-18 16:58:30#R4-54 :util :set trig_mod

22-Oct-18 16:58:30#R4-54 :util :trigger module set up as MASTER, crate nr: 0

22-Oct-18 16:58:30+R4-54 :util :set trig_mod finished (x0)

22-Oct-18 16:58:30#R4-54 :util :enable irq

22-Oct-18 16:58:30+R4-54 :util :enable irq finished (x0)

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_read_meb "./m_read_meb"

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_collector

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_transport

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_stream_serv

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_daq_rate

22-Oct-18 16:58:34!R4-54 :read_meb :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:58:35!R4-54 :collector :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:58:37#R4-54 :read_meb :task m_read_meb started

22-Oct-18 16:58:37#R4-54 :collector :task m_collector started

22-Oct-18 16:58:37#R4-54 :stream_serv:task m_stream_serv started

22-Oct-18 16:58:37#R4-54 :transport :task m_transport started

22-Oct-18 16:58:37#R4-54 :transport :enable tcp

22-Oct-18 16:58:37#R4-54 :transport :starting server in inclusive mode

22-Oct-18 16:58:37+R4-54 :transport :enable tcp finished (x0)

22-Oct-18 16:58:37+R4-54 :dispatch :>>> End procedure "startup.scom"

22-Oct-18 16:58:37#R4-54 :transport :waiting for client (port 6000)

22-Oct-18 16:59:50#R4-54 :stream_serv:140.181.81.77 connected

22-Oct-18 17:00:03#R4-54 :util :start acquisition

22-Oct-18 17:00:03+R4-54 :util :start acquisition finished (x0)

22-Oct-18 17:00:03#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 17:00:03#R4-54 :collector :acquisition running

22-Oct-18 17:01:26!R4-54 :dispatch :Key "events" > invalid value "v"!

22-Oct-18 17:01:26!R4-54 :dispatch :Command not executed

22-Oct-18 17:01:26!R4-54 :dispatch :Command "type event v" finished with argument error (20)

22-Oct-18 17:01:29#R4-54 :transport :type event -v

22-Oct-18 17:01:29+R4-54 :transport :type event finished (x0)

22-Oct-18 17:02:29#R4-54 :transport :type event -v

22-Oct-18 17:02:29+R4-54 :transport :type event finished (x0)

23-Oct-18 10:47:03#R4-54 :transport :type event -v 5

23-Oct-18 10:47:03+R4-54 :transport :type event finished (x0)

23-Oct-18 14:07:59!R4-54 :stream_serv:NODATA, client disconnected!

23-Oct-18 14:37:32#R4-54 :msg_log :Message logger running

23-Oct-18 14:38:37!R4-54 :dispatch :>>> Procedure "startup.scom" not found!

23-Oct-18 14:38:43#R4-54 :util :data acquisition was already started ���

23-Oct-18 14:39:03#R4-54 :util :show acquisition

23-Oct-18 14:39:04+R4-54 :util :show acquisition finished (x0)

23-Oct-18 14:41:16!R4-54 :dispatch :Command not found: "-R4-54"!

23-Oct-18 14:41:23!R4-54 :dispatch :Command key missing: type

23-Oct-18 14:41:55#R4-54 :transport :type event -v

23-Oct-18 14:42:11#R4-54 :transport :type event -v 3

23-Oct-18 14:59:29#R4-54 :util :start acquisition

23-Oct-18 14:59:29+R4-54 :util :start acquisition finished (x0)

23-Oct-18 14:59:45#R4-54 :transport :type event -v

23-Oct-18 15:00:39#R4-54 :util :show acquisition

23-Oct-18 15:00:40+R4-54 :util :show acquisition finished (x0)

23-Oct-18 15:49:53#R4-54 :util :show acquisition

23-Oct-18 15:49:54+R4-54 :util :show acquisition finished (x0)

23-Oct-18 15:50:15+R4-54 :transport :type event finished (x0)

23-Oct-18 15:55:44!R4-54 :stream_serv:received CLOSE, client disconnected!

23-Oct-18 16:11:45!R4-54 :stream_serv:received CLOSE, client disconnected!

23-Oct-18 16:17:30#R4-54 :stream_serv:show stream_serv

23-Oct-18 16:17:30#R4-54 :stream_serv:Streams: total 7622, sent 3811 (50.0%), free 8.

23-Oct-18 16:17:58#R4-54 :stream_serv:set stream_serv 1

23-Oct-18 16:17:58+R4-54 :stream_serv:set stream_serv finished (x0)

23-Oct-18 16:18:04#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:18:04+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:18:15#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:18:15+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:10#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:10+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:14#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:14+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:22#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:22+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:25#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:25+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:34!R4-54 :dispatch :value 0

23-Oct-18 16:19:34!R4-54 :dispatch :Command not executed

23-Oct-18 16:19:41#R4-54 :stream_serv:set stream_serv 1

23-Oct-18 16:19:41+R4-54 :stream_serv:set stream_serv finished (x0)

23-Oct-18 16:20:03#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:03+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:20:08#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:08+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:20:11#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:11+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:24:14#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:24:14+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:26:57#R4-54 :stream_serv:140.181.81.77 connected

24-Oct-18 15:05:22#R4-54 :util :stop acquisition

24-Oct-18 15:05:24#R4-54 :collector :acquisition NOT running

26-Oct-18 14:38:49#R4-55 :msg_log :Message logger running

26-Oct-18 14:38:59+R4-55 :dispatch :>>> Start procedure "startup.scom" break mode 1

26-Oct-18 14:38:59#R4-55 :dispatch :start task m_util

26-Oct-18 14:39:02#R4-55 :util :task m_util started

26-Oct-18 14:39:02#R4-55 :util :load setup setup.usf

26-Oct-18 14:39:02#R4-55 :util :setup file setup.usf successfully loaded

26-Oct-18 14:39:02+R4-55 :util :load setup finished (x0)

26-Oct-18 14:39:02#R4-55 :util :set trig_mod

26-Oct-18 14:39:02#R4-55 :util :trigger module set up as MASTER, crate nr: 0

26-Oct-18 14:39:02+R4-55 :util :set trig_mod finished (x0)

26-Oct-18 14:39:02#R4-55 :util :enable irq

26-Oct-18 14:39:02+R4-55 :util :enable irq finished (x0)

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_read_meb "./m_read_meb"

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_collector

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_transport

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_stream_serv

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_daq_rate

26-Oct-18 14:39:07!R4-55 :read_meb :Pipe type 0: smem_create for base 0x8000000

26-Oct-18 14:39:07!R4-55 :collector :Pipe type 0: smem_create for base 0x8000000

26-Oct-18 14:39:08#R4-55 :read_meb :task m_read_meb started

26-Oct-18 14:39:09#R4-55 :stream_serv:task m_stream_serv started

26-Oct-18 14:39:09#R4-55 :collector :task m_collector started

26-Oct-18 14:39:09#R4-55 :transport :task m_transport started

26-Oct-18 14:39:09#R4-55 :transport :enable tcp

26-Oct-18 14:39:09#R4-55 :transport :starting server in inclusive mode

26-Oct-18 14:39:09+R4-55 :transport :enable tcp finished (x0)

26-Oct-18 14:39:09+R4-55 :dispatch :>>> End procedure "startup.scom"

26-Oct-18 14:39:09#R4-55 :transport :waiting for client (port 6000)

26-Oct-18 14:39:23#R4-55 :util :start acquisition

26-Oct-18 14:39:23+R4-55 :util :start acquisition finished (x0)

26-Oct-18 14:39:23#R4-55 :read_meb :found trig type 14 == start acquisition

26-Oct-18 14:39:24#R4-55 :collector :acquisition running

26-Oct-18 14:39:30#R4-55 :transport :type event -v 4

26-Oct-18 14:39:30+R4-55 :transport :type event finished (x0)

26-Oct-18 14:39:33#R4-55 :transport :type event -v 4

26-Oct-18 14:39:33+R4-55 :transport :type event finished (x0)

26-Oct-18 14:49:28#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 14:56:07!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 14:58:24#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 15:11:09!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 15:11:54#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 15:13:41!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 15:46:38#R4-55 :util :stop acquisition

26-Oct-18 15:46:40+R4-55 :util :stop acquisition finished (x0)

26-Oct-18 15:46:40#R4-55 :collector :acquisition NOT running

26-Oct-18 15:46:40#R4-55 :read_meb :found trig type 15 == stop acquisition

28-Nov-18 10:43:17#R4L-60 :msg_log :Message logger running

28-Nov-18 10:43:22+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_util

28-Nov-18 10:43:22#R4L-60 :util :task m_util started

28-Nov-18 10:43:22#R4L-60 :util :load setup setup.usf

28-Nov-18 10:43:22#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 10:43:22+R4L-60 :util :load setup finished (x0)

28-Nov-18 10:43:22#R4L-60 :util :set trig_mod

28-Nov-18 10:43:22#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 10:43:22+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 10:43:22#R4L-60 :util :enable irq

28-Nov-18 10:43:22+R4L-60 :util :enable irq finished (x0)

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_collector

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_transport

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 10:43:22!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:43:22#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:43:23!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:43:23#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:43:23#R4L-60 :transport :task m_transport started

28-Nov-18 10:43:23#R4L-60 :transport :enable tcp

28-Nov-18 10:43:23#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 10:43:23+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 10:43:23+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 10:43:23#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 10:43:23#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 10:48:22#R4L-60 :msg_log :Message logger running

28-Nov-18 10:48:25+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_util

28-Nov-18 10:48:25#R4L-60 :util :task m_util started

28-Nov-18 10:48:25#R4L-60 :util :load setup setup.usf

28-Nov-18 10:48:25#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 10:48:25+R4L-60 :util :load setup finished (x0)

28-Nov-18 10:48:25#R4L-60 :util :set trig_mod

28-Nov-18 10:48:25#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 10:48:25+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 10:48:25#R4L-60 :util :enable irq

28-Nov-18 10:48:25+R4L-60 :util :enable irq finished (x0)

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_collector

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_transport

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 10:48:25!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:48:25#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:48:25!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:48:25#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:48:25#R4L-60 :transport :task m_transport started

28-Nov-18 10:48:25#R4L-60 :transport :enable tcp

28-Nov-18 10:48:25#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 10:48:25+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 10:48:25+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 10:48:25#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 10:48:25#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 10:48:41#R4L-60 :msg_log :exiting.. SIGTERM (kill) signal ���

28-Nov-18 11:01:34#R4L-60 :msg_log :Message logger running

28-Nov-18 11:01:37+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_util

28-Nov-18 11:01:37#R4L-60 :util :task m_util started

28-Nov-18 11:01:37#R4L-60 :util :load setup setup.usf

28-Nov-18 11:01:37#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 11:01:37+R4L-60 :util :load setup finished (x0)

28-Nov-18 11:01:37#R4L-60 :util :set trig_mod

28-Nov-18 11:01:37#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 11:01:37+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 11:01:37#R4L-60 :util :enable irq

28-Nov-18 11:01:37+R4L-60 :util :enable irq finished (x0)

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_collector

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_transport

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 11:01:38!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 11:01:38#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 11:01:38!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 11:01:38#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 11:01:38#R4L-60 :transport :task m_transport started

28-Nov-18 11:01:38#R4L-60 :transport :enable tcp

28-Nov-18 11:01:38#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 11:01:38+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 11:01:38+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 11:01:38#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 11:01:38#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 11:01:55!R4L-60 :dispatch :Command not found: "ls"!

28-Nov-18 11:01:57!R4L-60 :dispatch :Command not found: "cd .."!

28-Nov-18 11:44:45#R4L-60 :msg_log :Message logger running

28-Nov-18 11:44:51+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_util

28-Nov-18 11:44:51#R4L-60 :util :task m_util started

28-Nov-18 11:44:51#R4L-60 :util :load setup setup.usf

28-Nov-18 11:44:51#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 11:44:51+R4L-60 :util :load setup finished (x0)

28-Nov-18 11:44:51#R4L-60 :util :set trig_mod

28-Nov-18 11:44:51#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 11:44:51+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 11:44:51#R4L-60 :util :enable irq

28-Nov-18 11:44:51+R4L-60 :util :enable irq finished (x0)

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_collector

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_transport

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_daq_rate

... 21082 more lines ...

|

|

181

|

Tue Dec 15 09:25:41 2020 |

Jan | DAQ | SiCsIPhos signal/amplitude reconstruction | |

| Attachment 1: amps.pdf

|

|

|

182

|

Mon Mar 29 16:31:09 2021 |

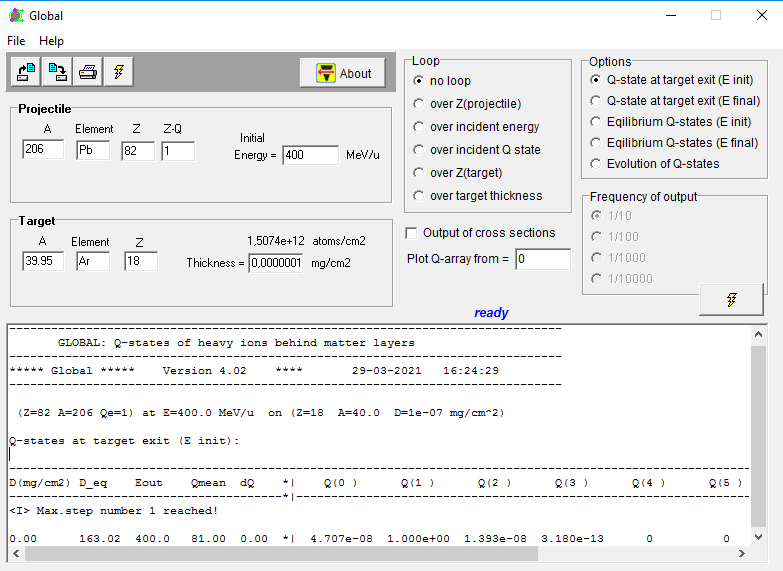

Pierre-Michel | DAQ | cross section | (1.393*^-8 + 3.18*^-13 + 4.707*^-8)/4.707*^-8 = 1.29595 |

| Attachment 1: Pb81onAr.png

|

|

|

184

|

Wed Aug 25 15:13:41 2021 |

Jan | DAQ | SC13 clock frequency | The frequency of the clock used as reference in scaler channel 13 has been measured precisely.

In contrast to what was expected (1.5MHz precisely), it is:

f_ref = 1.5625(5) MHz |

|

3

|

Wed Dec 5 17:29:24 2018 |

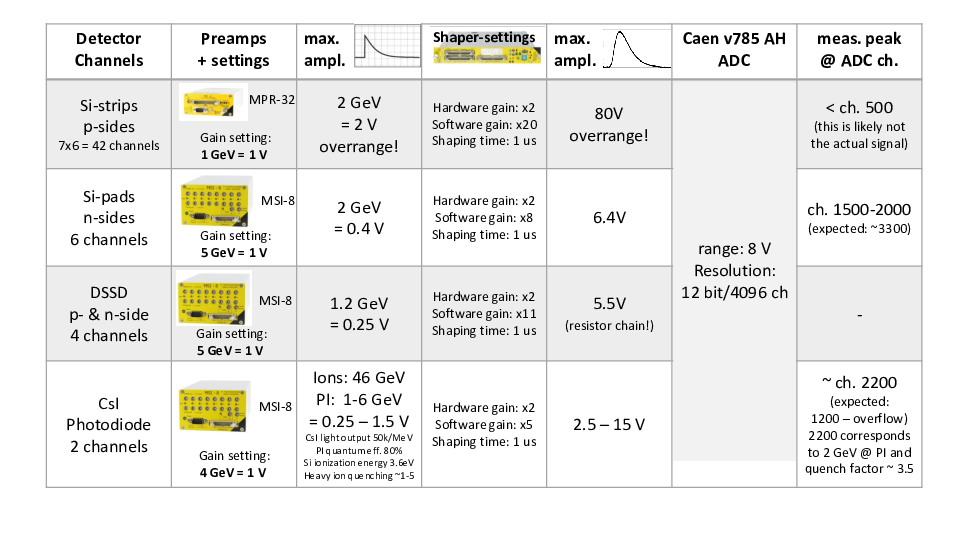

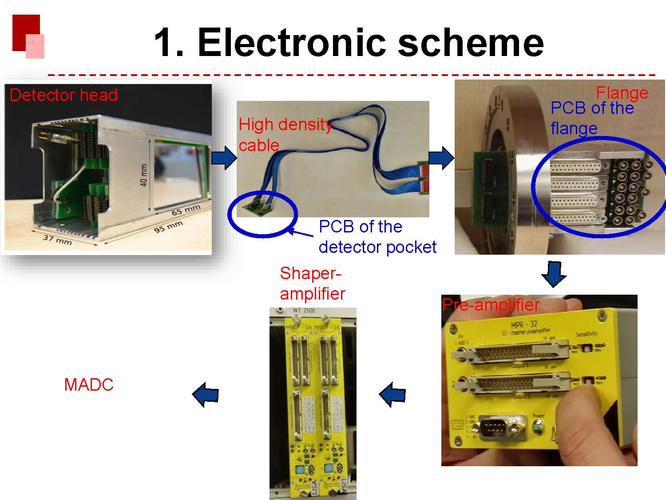

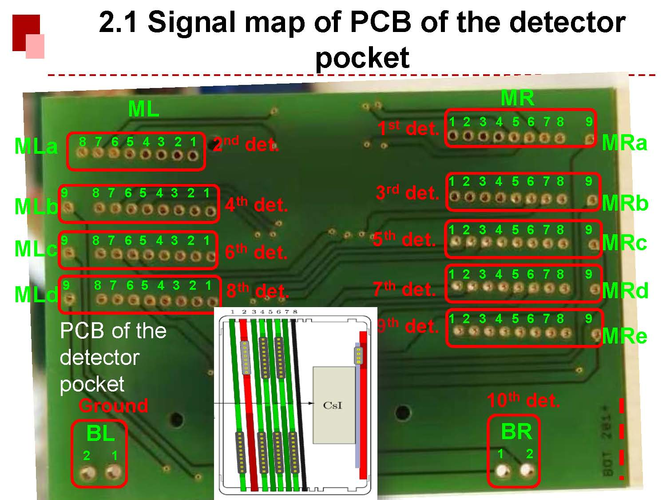

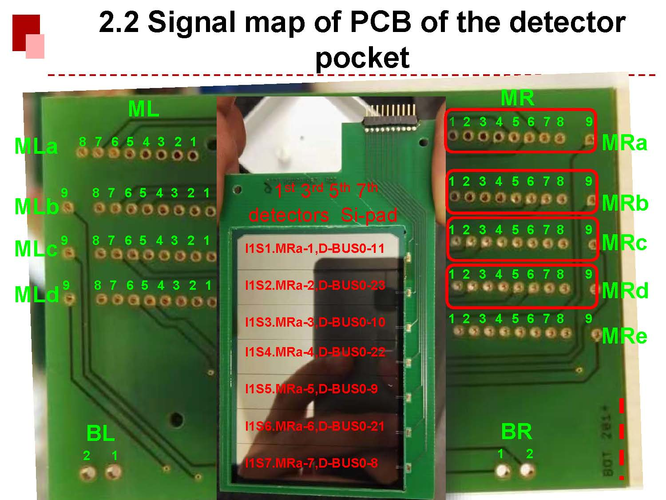

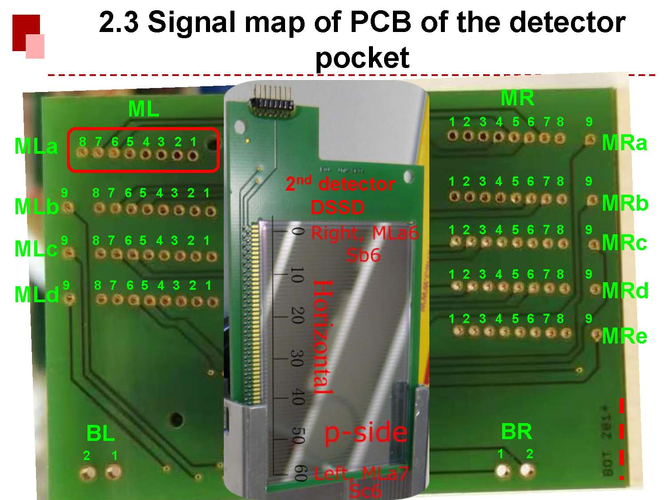

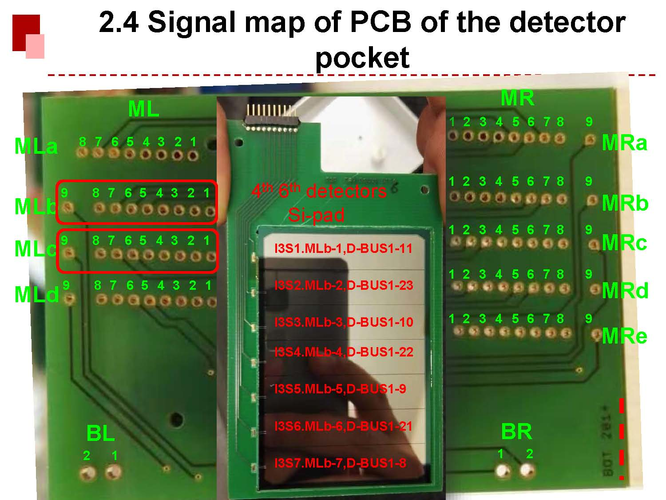

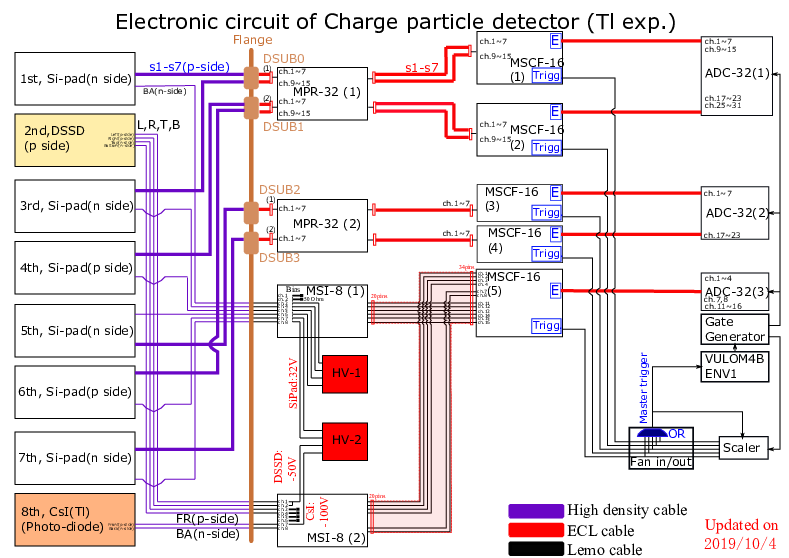

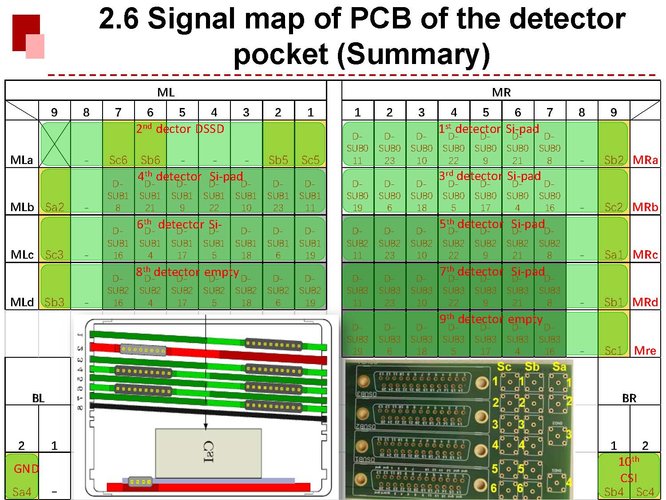

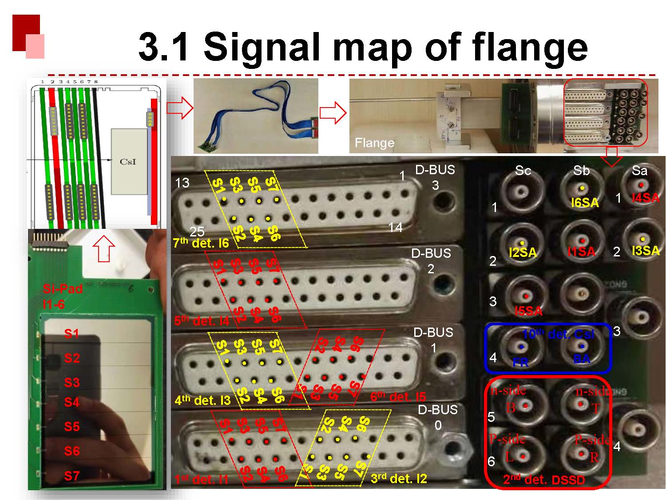

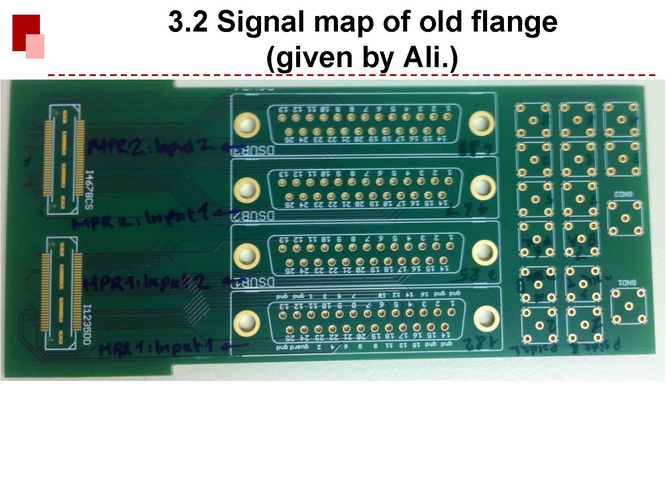

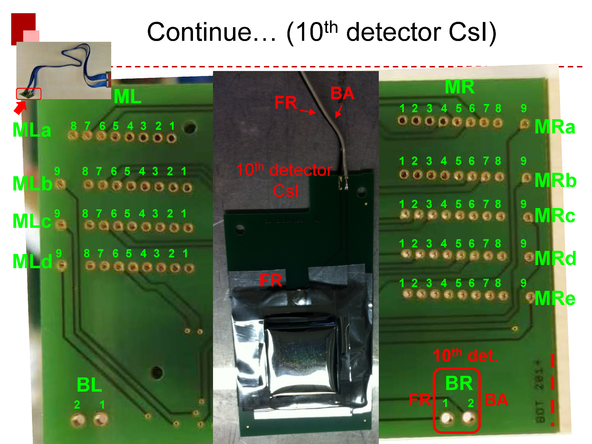

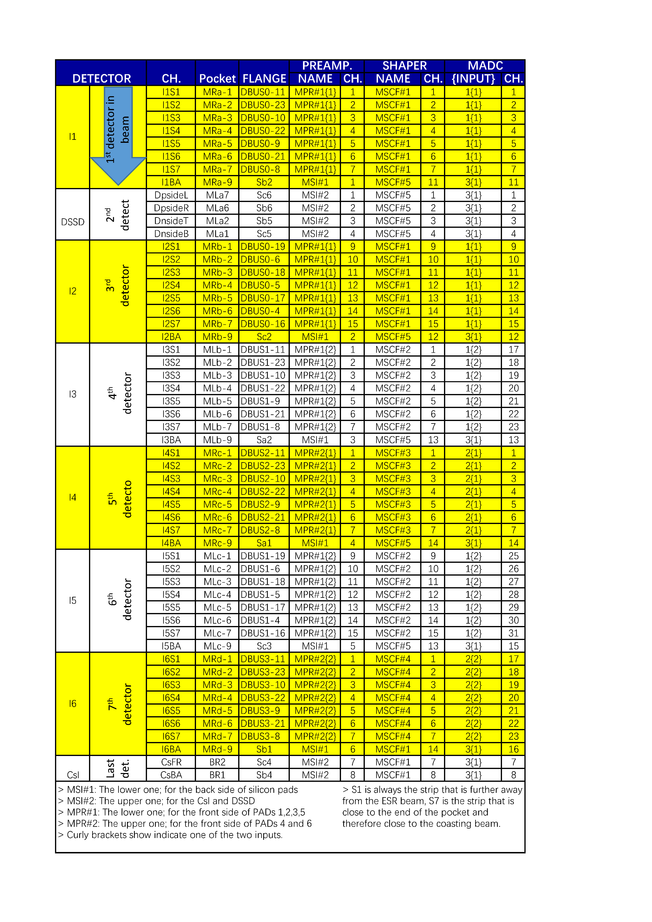

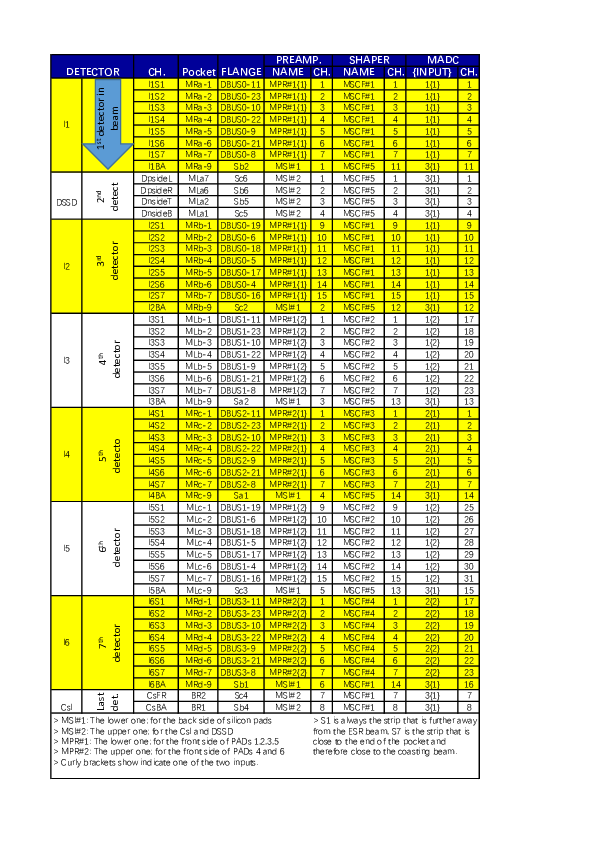

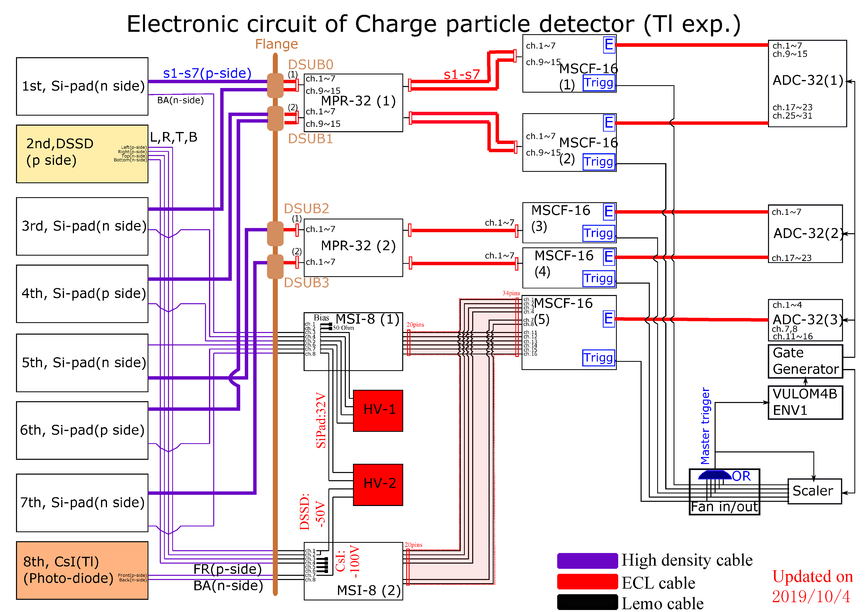

Chen, Sidhu | Detectors | signal map | Description:

Here is a summary of signal map. The charged particle detector includes 6 layers of Si-Pad, 1 DSSD and 1 CsI.

All these detectors are installed inside the detector pocket. All signals are connected to one PCB which is attached on the pocket, then are connected

to the PCB of the flange by high density cable. This document descripts the signal map on the PCB of the detector

pocket and flange.

The signal maps of the PCB of the detector pocket are shown as follow:

|

|

6

|

Mon Dec 10 11:59:15 2018 |

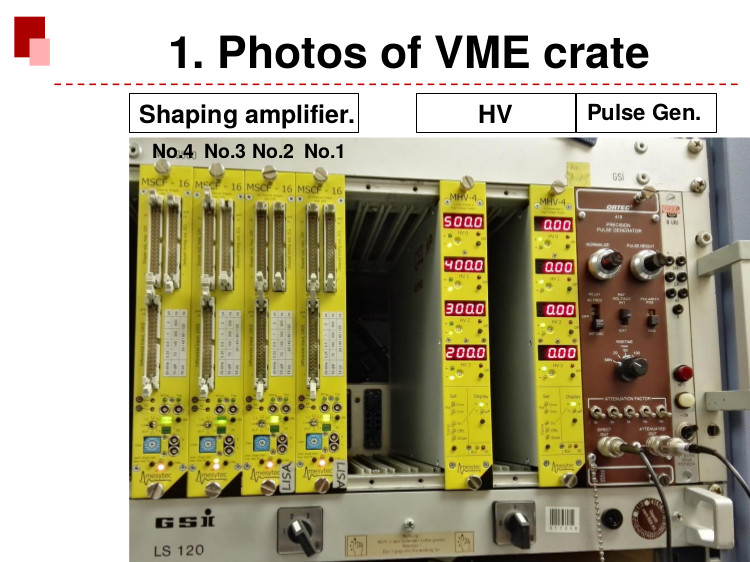

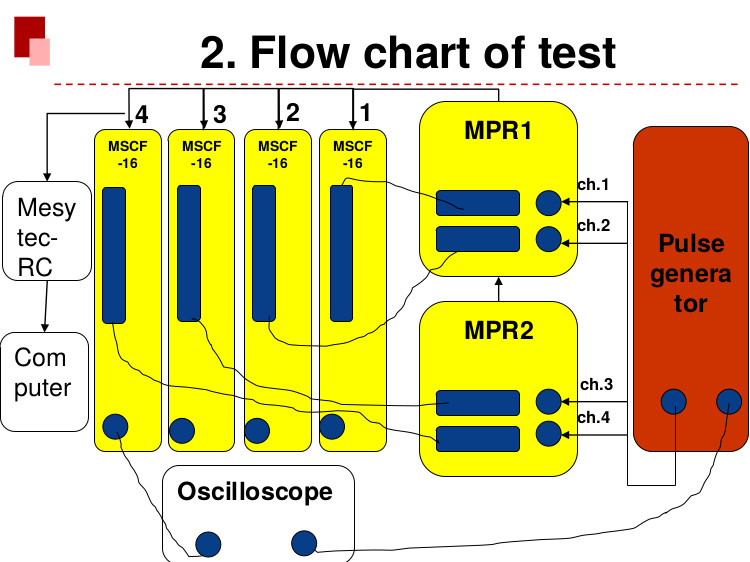

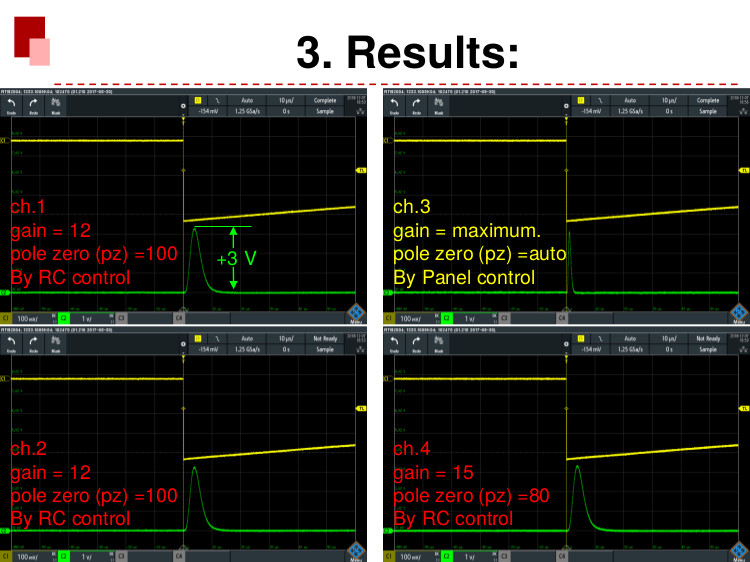

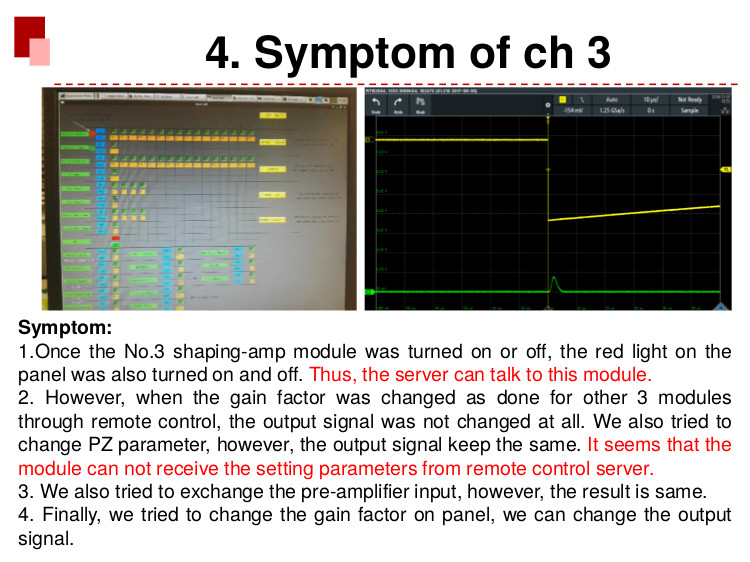

Chen, Sidhu | Detectors | Test of shaping amplifier. |

|

|

11

|

Tue Aug 27 14:53:47 2019 |

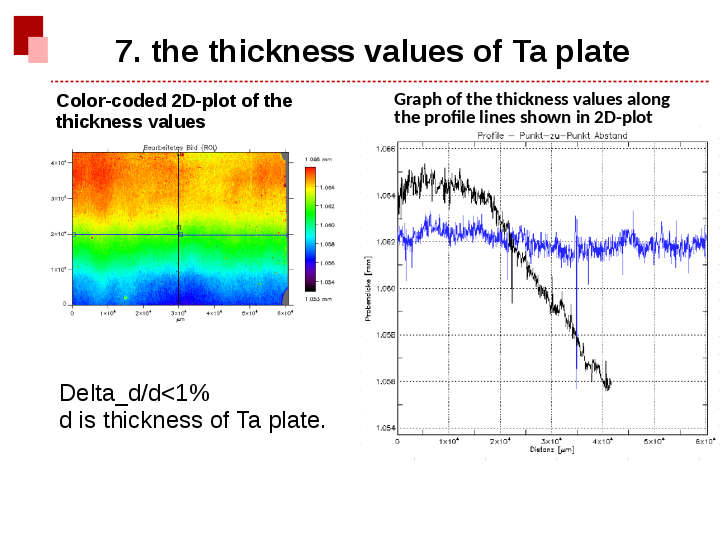

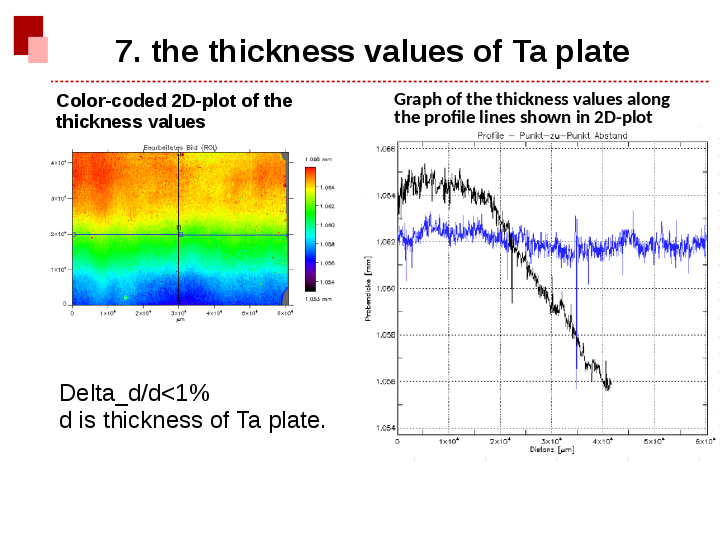

Chen, Sidhu | Detectors | The thickness uncertainty of Ta is less than 1%. | The thickness of Ta plate have been measured by target group. The result is show as following.

According to this measurement, the thickness uncertainty is less than 1%.

This thickness uncertainty is good enough for Tl experiment.

|

| Attachment 1: 20180711ChargeParticleDetectorV8.png

|

|

| Attachment 3: 2019_08-Ta-Blech.xlsx

|

|

12

|

Thu Oct 24 15:36:13 2019 |

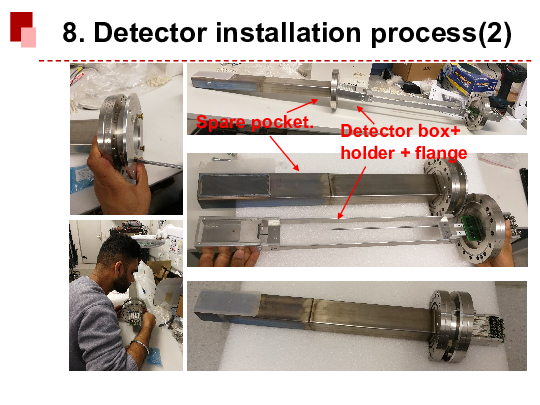

Chen, Sidhu | Detectors | Detector installation process |

|

| Attachment 4: Detector_installation_process.pdf

|

|

|

17

|

Thu Feb 27 14:04:12 2020 |

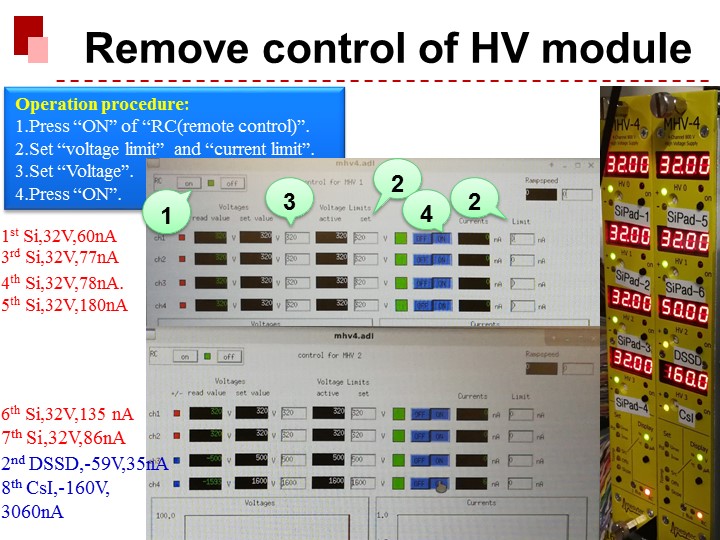

Ruijiu Chen | Detectors | Remote control of HV module | Be careful. The voltage value on user interface is 10 times of real value. e.g. if the real value is 32V, the voltage value on UI has to be 320V.

|

|

27

|

Sat Mar 28 04:32:15 2020 |

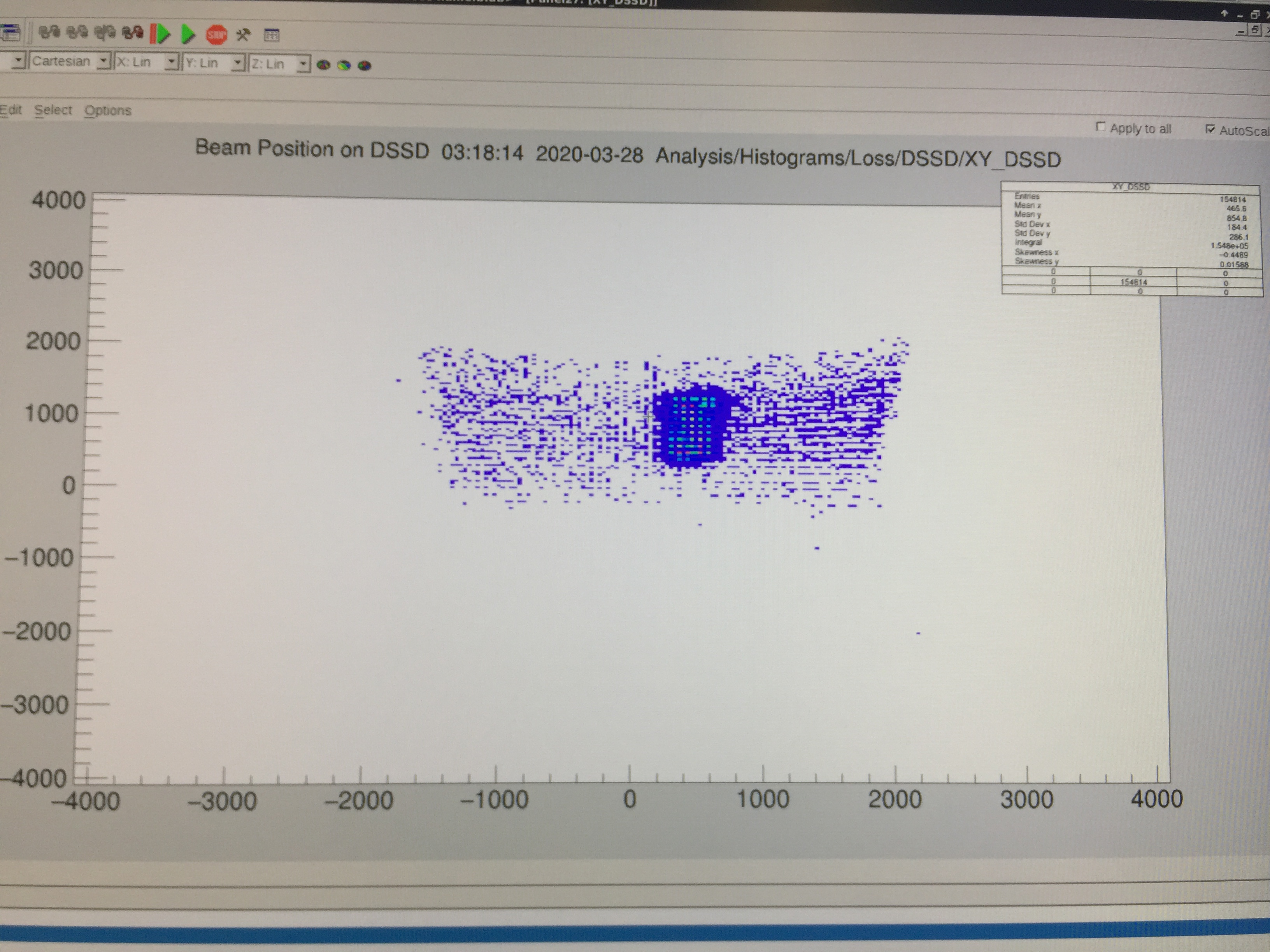

Ragan | Detectors | Ionisation events on DSSSD | XY co-relation of DSSSD showing 206Pb82+ beam hitting the CsISiPHOS detector present in the inner pocket of ESR after the first dipole after the gas jet. 206Pb82+ is

produced by ionisation of

206Pb81+ due to interaction of beam with the gas jet. |

| Attachment 1: 9800D808-D570-466D-8411-512D069F9233.jpeg

|

|

|