| ID |

Date |

Author |

Category |

Subject |

|

164

|

Mon Apr 6 05:43:50 2020 |

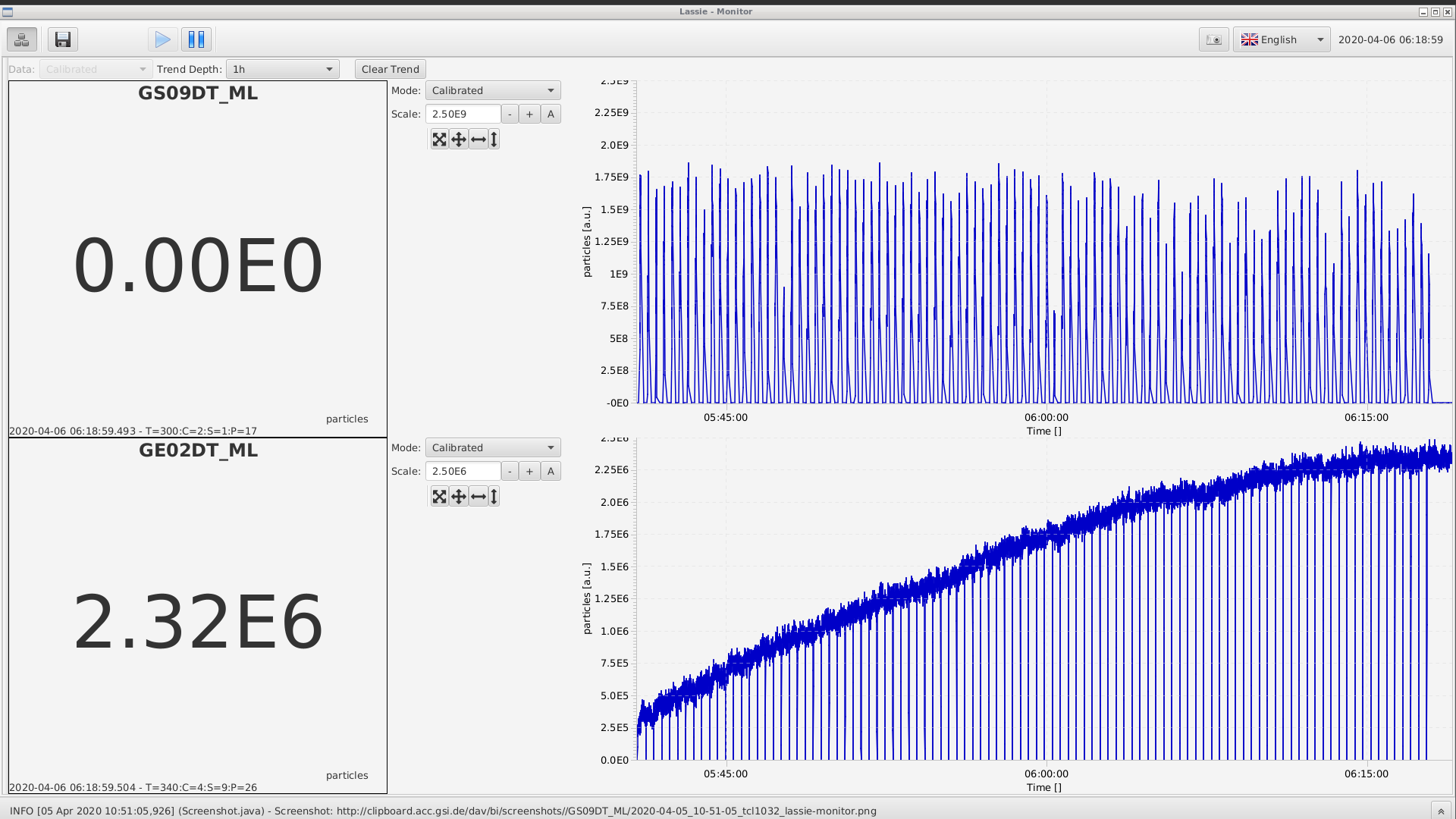

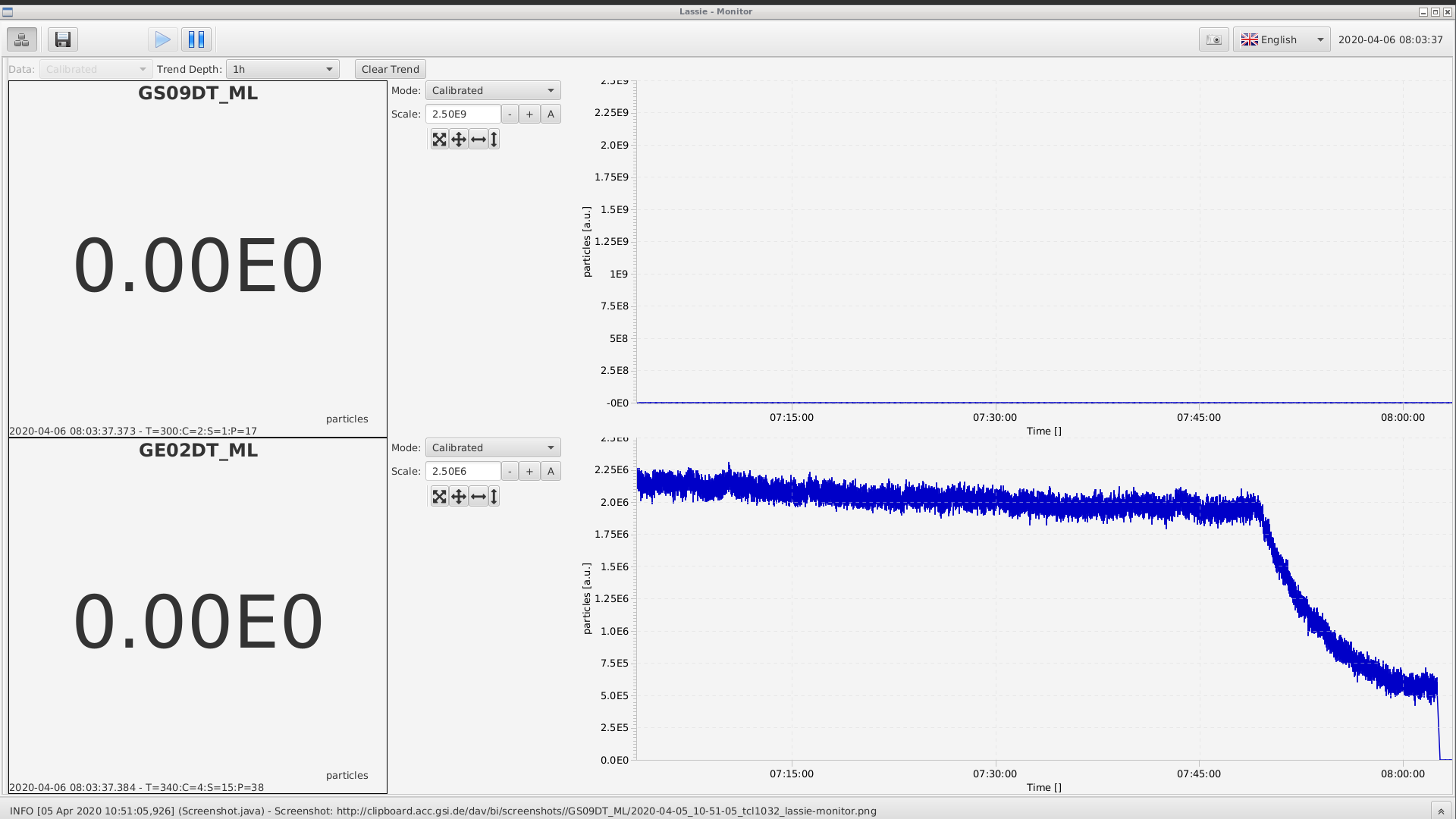

Ragan, Laszlo, Nikos | Runs | One and a half hour measurement (S2: 0/35 mm and S6: -20/7 mm) | beam: 205Tl81+ (no scraping , Al ~1g/cm2)

energy: 400 MeV/u

storage time: 1.5 hr

S2: 0/35 mm

s6: -20/7

purpose: data with TARGET ON

Detector position (CsISiPHOS): out of the ring

Detector position (MWPC): -60 mm

run start at 20:21, run0540.lmd

file running: 0558.lmd

_______________________________________________________________________________

time when accumulation starts: 05:41

time when storage starts: 06:19

time when storage ends: 07:49

I_cooler during storage time: -1 mA (20 mA)

I_cooler = 179 mA

I_SIS: 1.75e9

ESR particles after stacking: 2.3e6 (offset 5e5)

Number of stackings: 100

Target ON density: 4.36e12

Target on time for measurement: 10 mins (by event mode)

time spend at manipulation 13 : 3 mins

(i.e. time for which electron cooler is on after gas jet)

NTCAp file:

SC_2020-04-06_00-59-46

\IQ_2020-04-06_00-59-38

IQ rate: 8 MS/s

(saved in drive : O)

copy and repeat the above (below the line) for every storage time measurement/ |

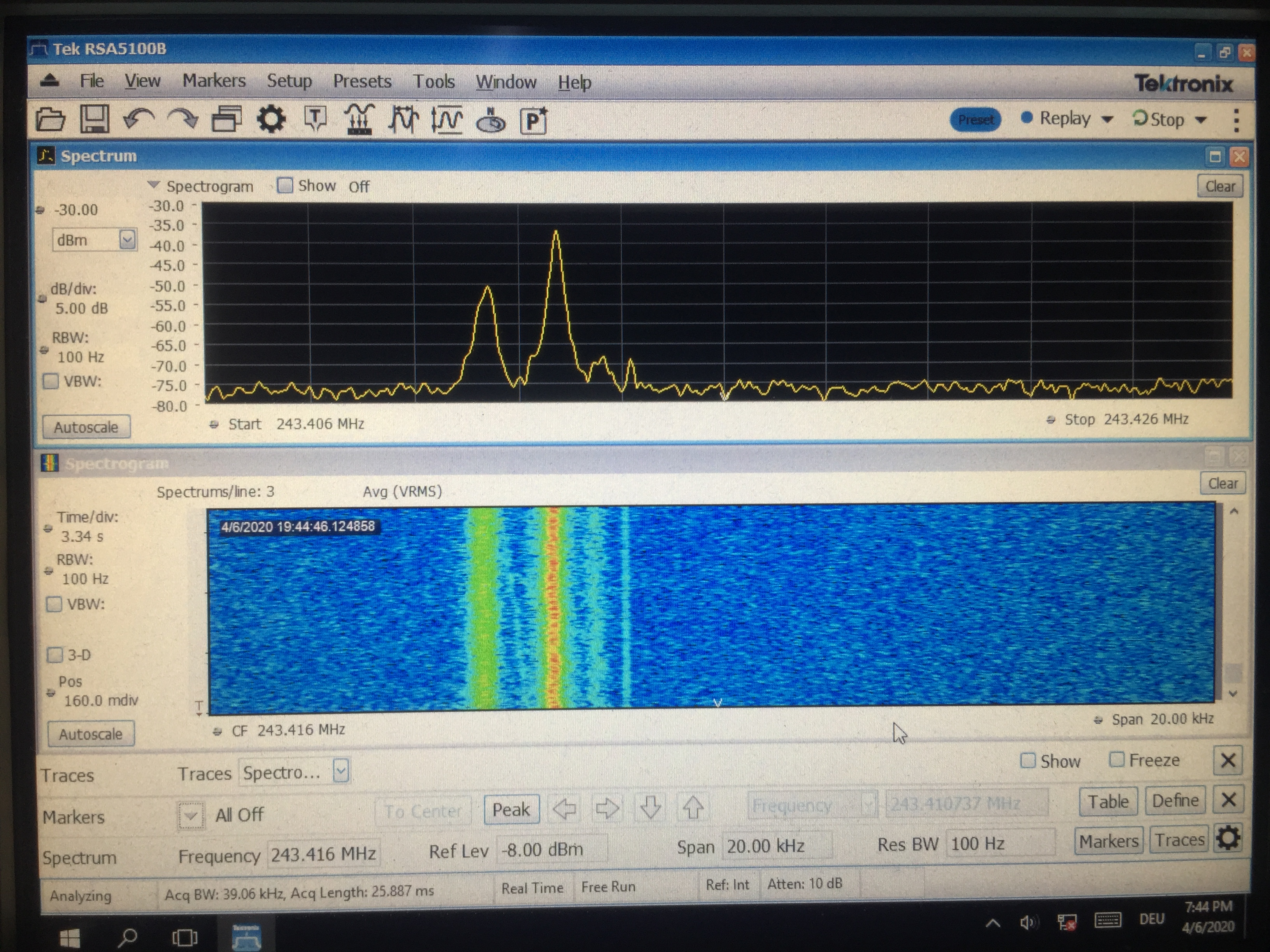

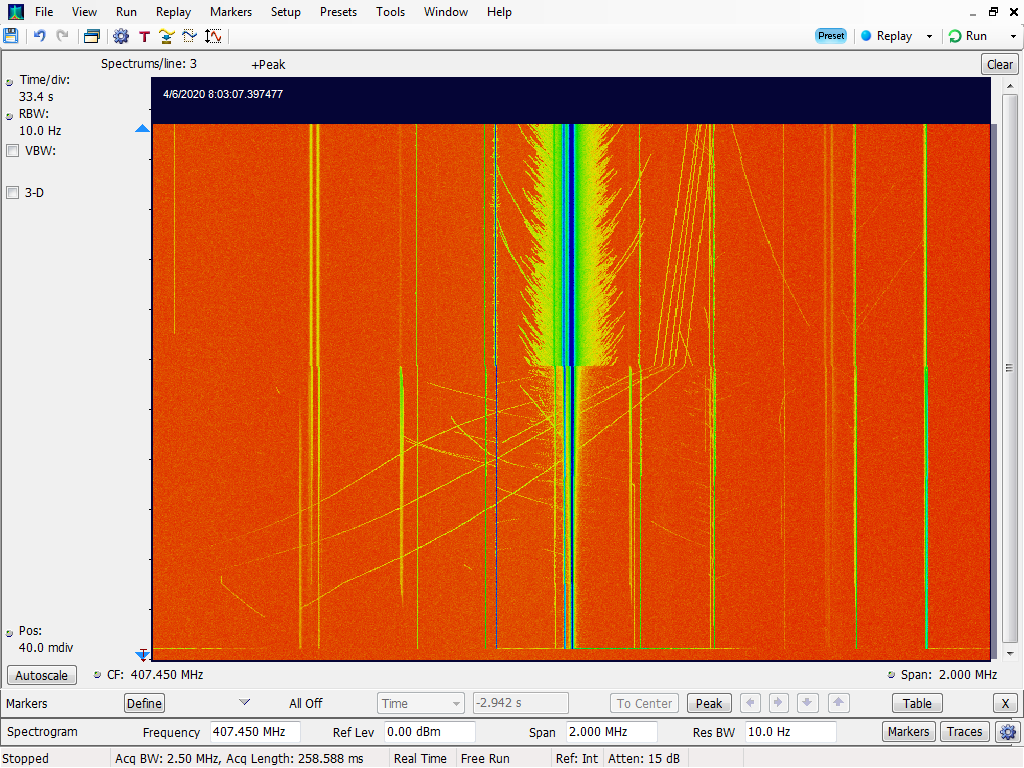

| Attachment 1: 2020-04-06_06-18-59-809.png

|

|

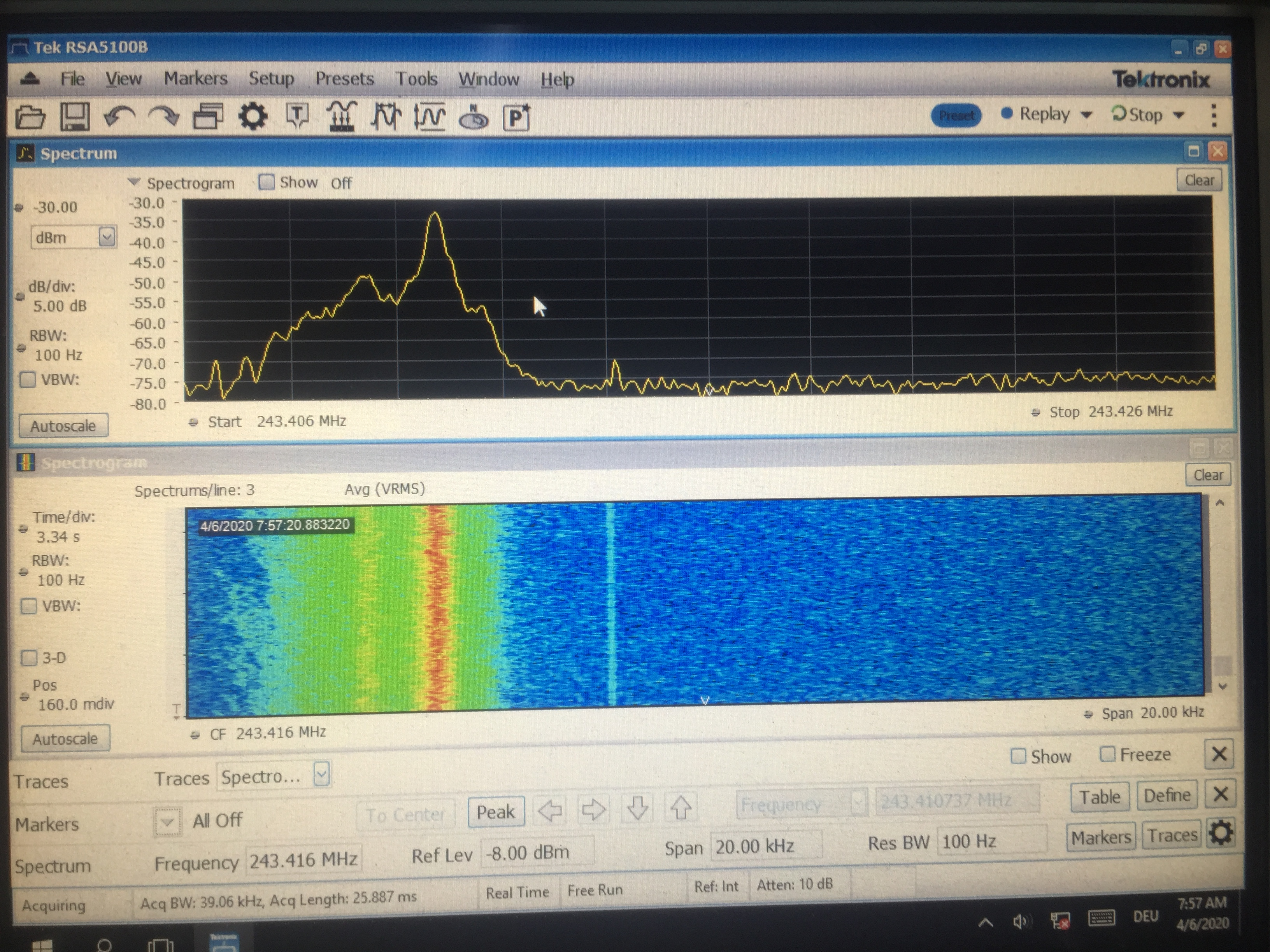

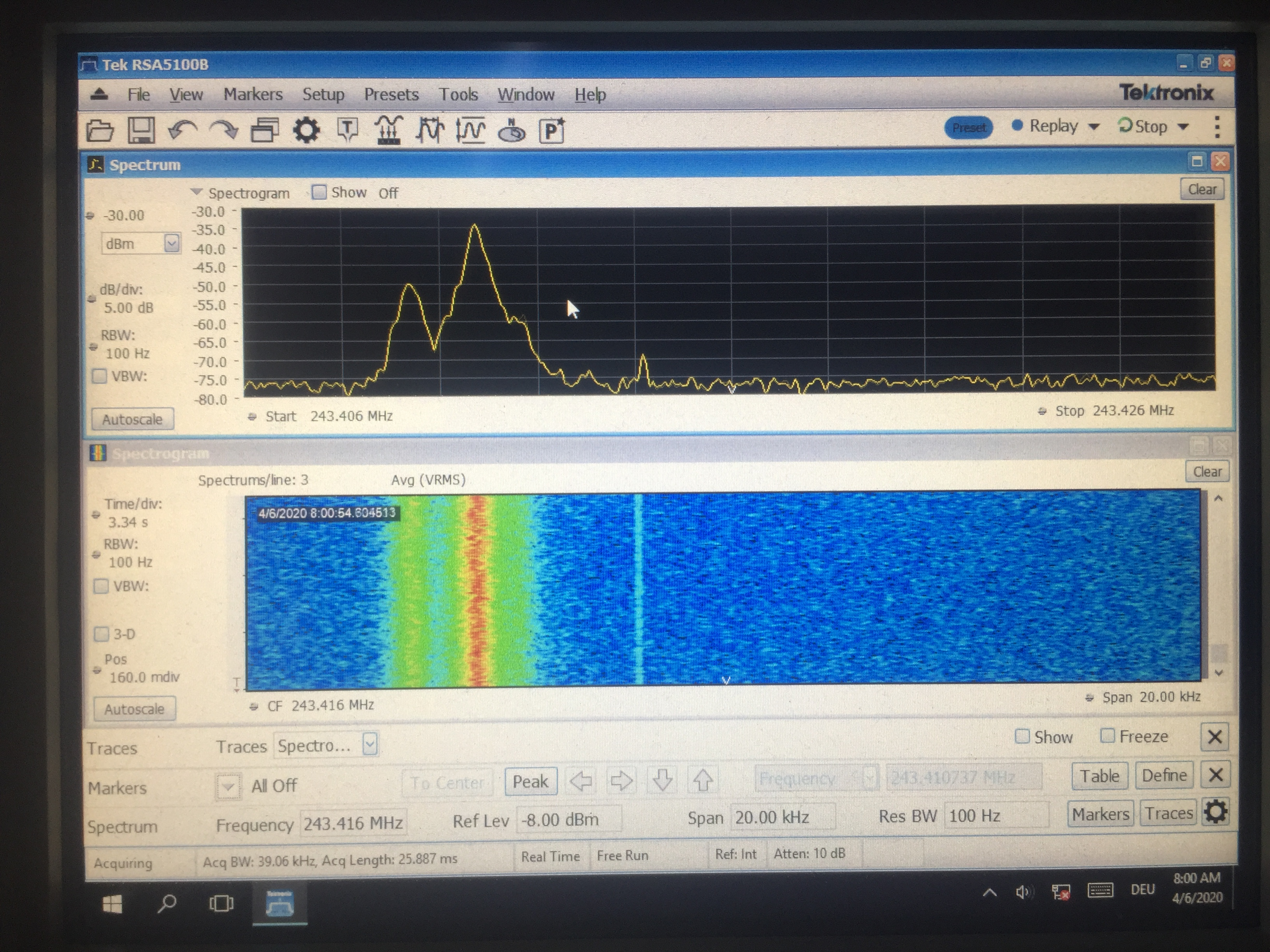

| Attachment 2: 946073FA-3077-4CBF-900B-565BD19CF040.jpeg

|

|

| Attachment 3: 10FEB6AE-653B-4803-9927-EEB5BF33D3ED.jpeg

|

|

| Attachment 4: 2020-04-06_08-03-40-493.png

|

|

|

165

|

Mon Apr 6 08:37:02 2020 |

Ragan, Shahab, Pierre-Michel | Runs | 10 hour measurement (S2: 0/35 mm and S6: -20/7 mm) | beam: 205Tl81+ (no scraping , Al ~1g/cm2)

energy: 400 MeV/u

storage time: 10 hr

S2: 0/35 mm

s6: -20/7

purpose: data with TARGET ON

Detector position (CsISiPHOS): out of the ring

Detector position (MWPC): -60 mm

run start at 20:21, run0540.lmd

file running: 0558.lmd

_______________________________________________________________________________

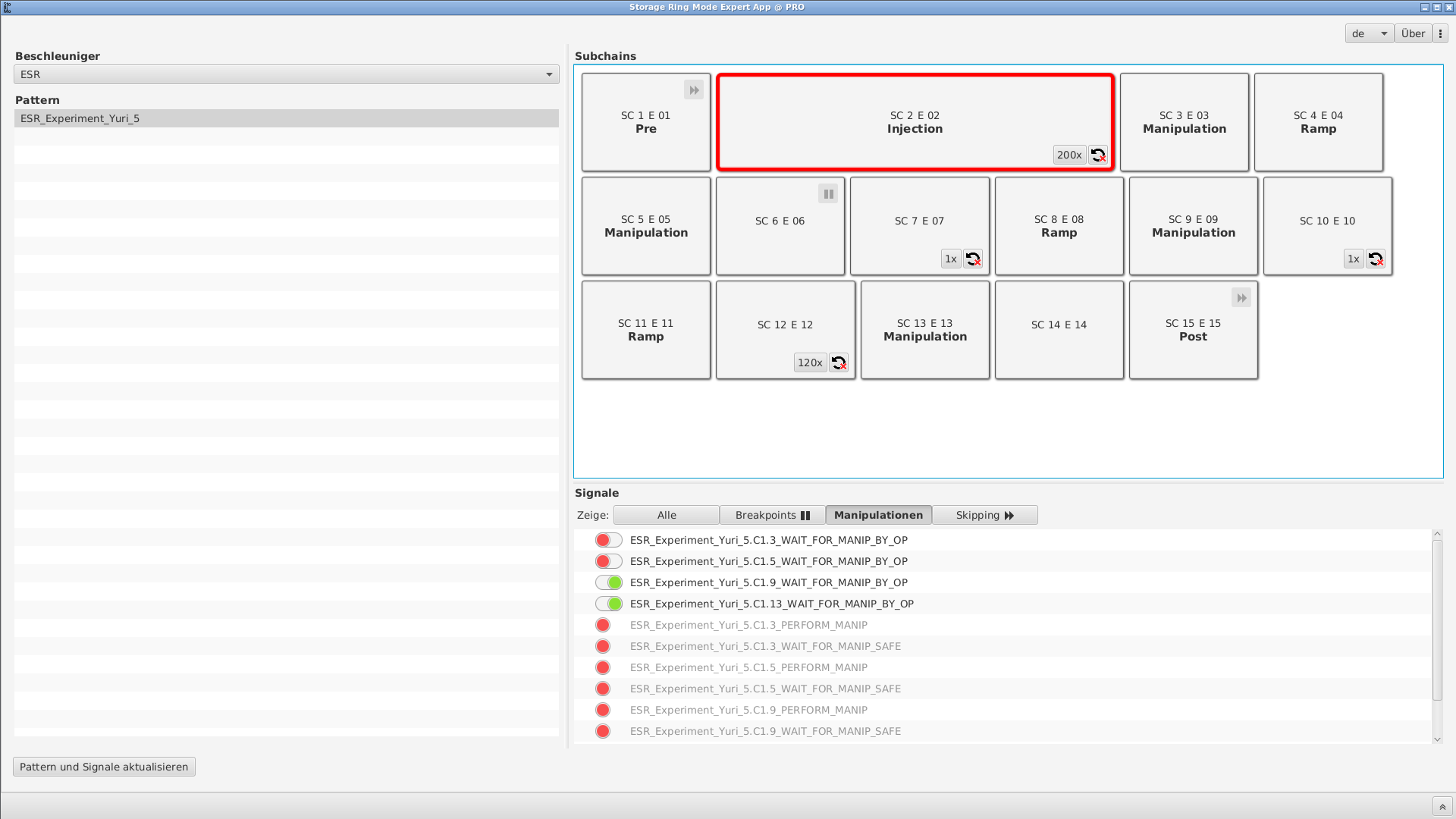

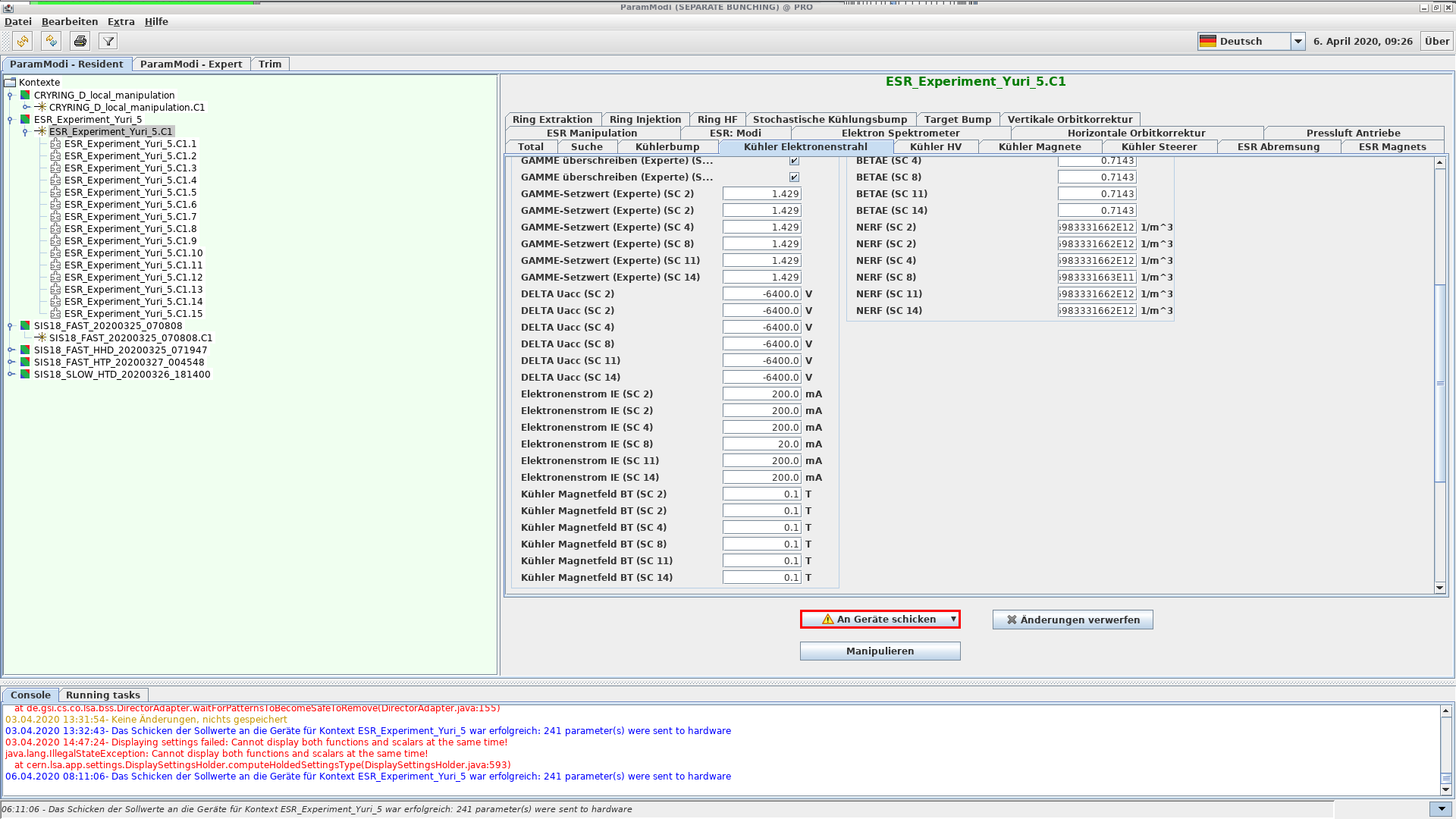

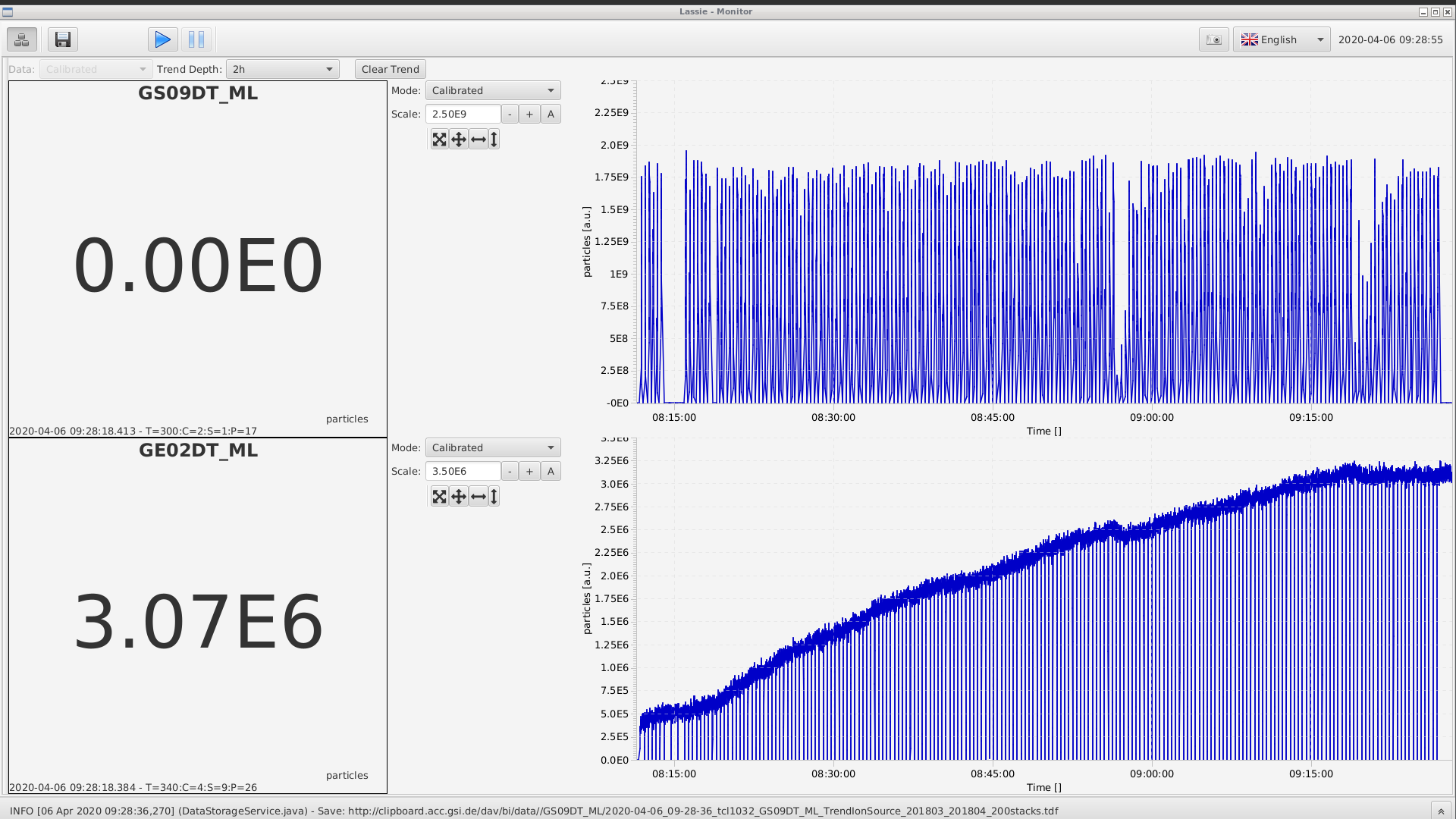

time when accumulation starts: 08:21

time when storage starts: 09:27

time when storage ends: 19:27

I_cooler during storage time: -1 mA (20 mA)

I_cooler = 180 mA

I_SIS: 1.8e9

ESR particles after stacking: 3.1e6 (offset 4e5)

Number of stackings: 200

Target ON density: 4.15e12

Target on time for measurement: 10 mins (by event mode)

time spend at manipulation 13 : 10 mins

(i.e. time for which electron cooler is on after gas jet)

I_ESR (10:34): 2.78e6

I_ESR (11:07): 2.53e6

I_ESR (12:07): 2.2e6

I_ESR (13:43): 1.7e6

I_ESR (14:00): 1.6E6

I_ESR (14:43): 1.5e6

I_ESR (15:24): 1.43e6

I_ESR (16:19): 1.3e6

I_ESR (17:03): I.IIIeVI

I_ESR (18:20): 1.15e6 (frozen screen)

I_ESR (18:50): 9.5e5

I_ESR (19:27): 8.5e5

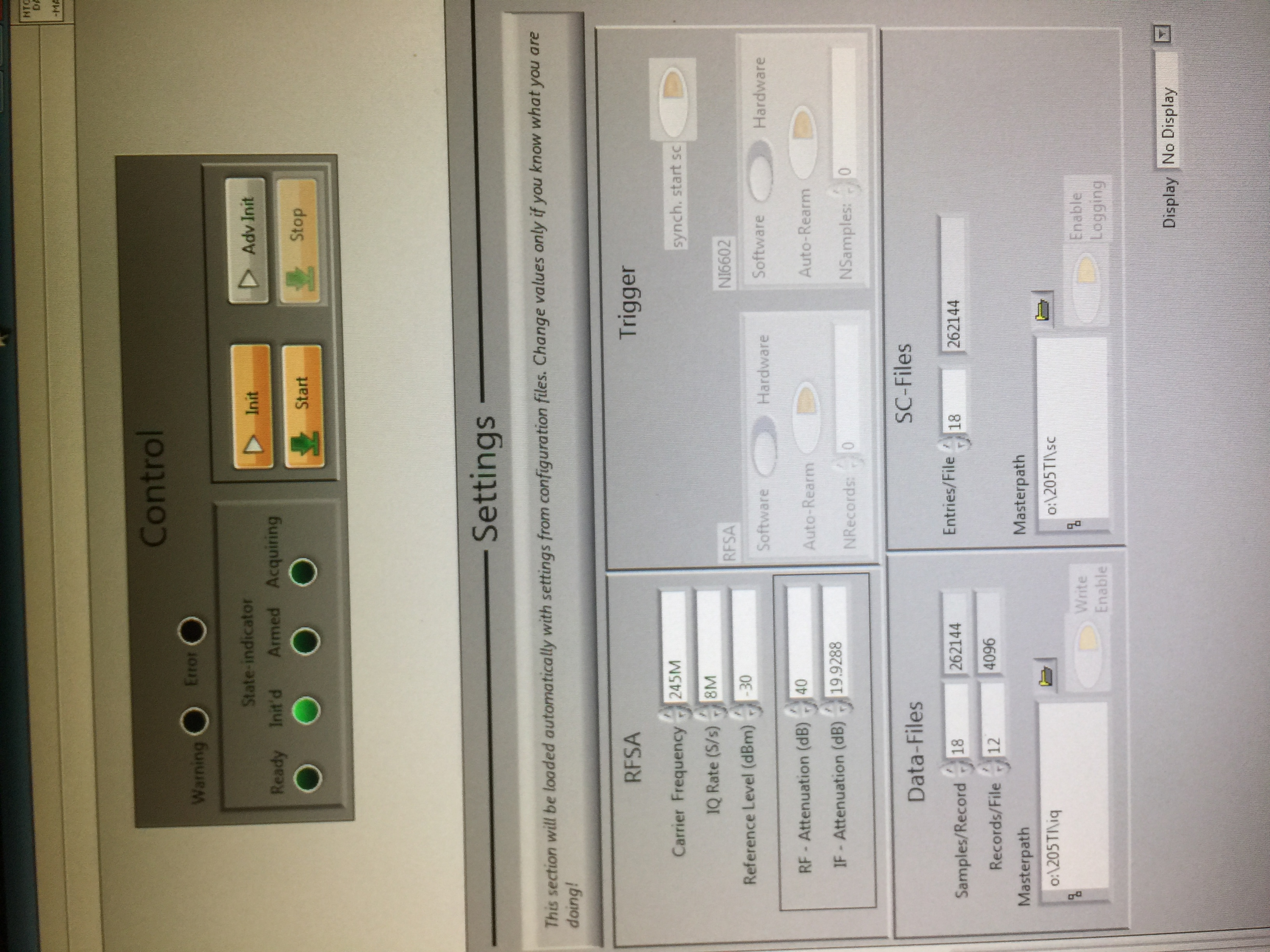

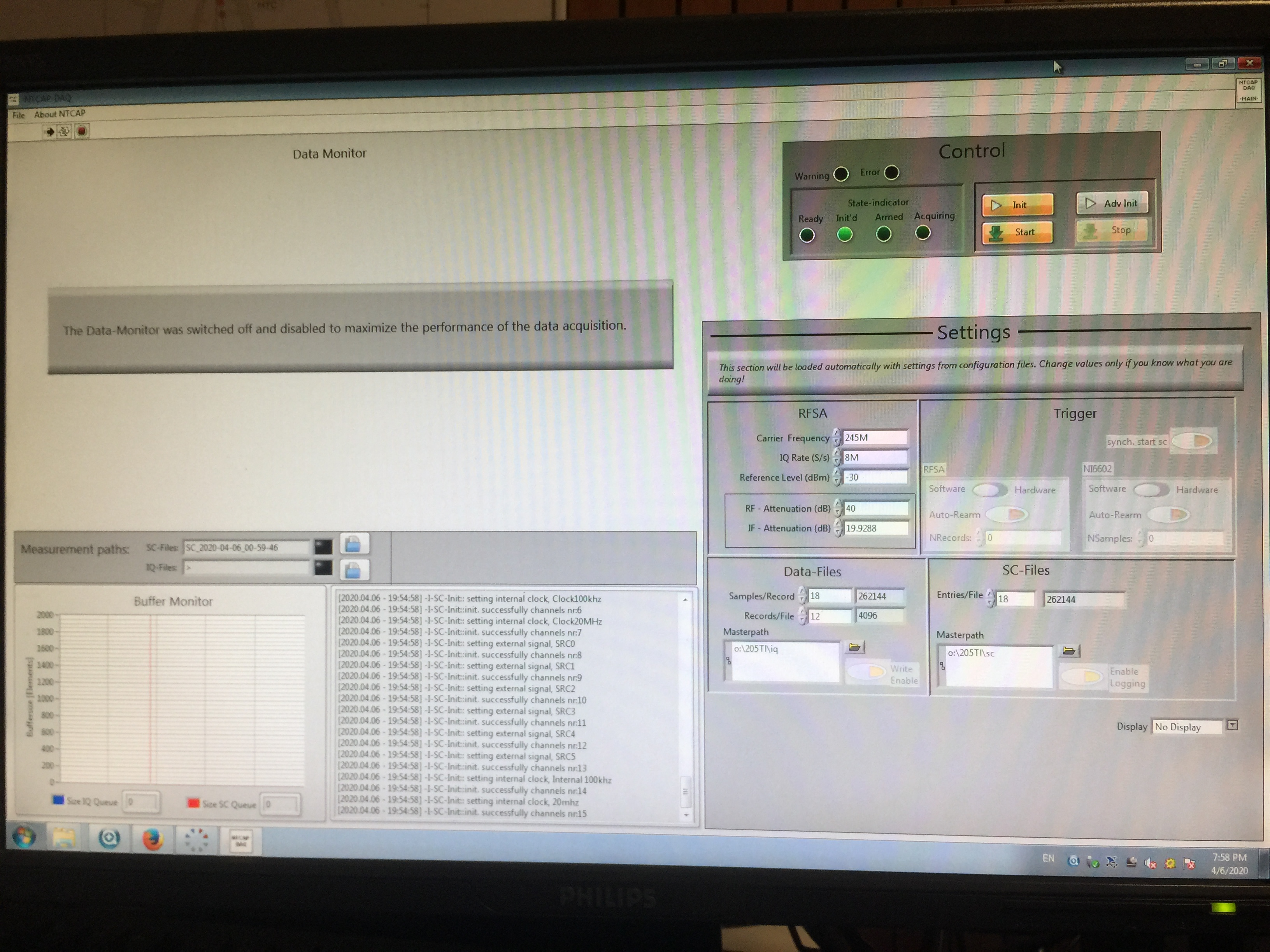

NTCAp file:

SC_2020-04-06_00-59-46

\IQ_2020-04-06_00-59-38

IQ rate: 8 MS/s

(saved in drive : O)

copy and repeat the above (below the line) for every storage time measurement/ |

| Attachment 1: 2020-04-06_09-26-46-084.png

|

|

| Attachment 2: 2020-04-06_09-27-05-494.png

|

|

| Attachment 3: 2020-04-06_09-28-55-435.png

|

|

| Attachment 4: 966F359F-1BC2-4923-8A7A-4067312EC945.jpeg

|

|

| Attachment 5: 3A858F59-3AC9-41B2-8804-0672BFF50554.jpeg

|

|

| Attachment 6: 1CE8A342-C798-4B86-B175-228F841C1650.jpeg

|

|

| Attachment 7: ECAA6801-6590-4155-88FB-90EAE304358D.jpeg

|

|

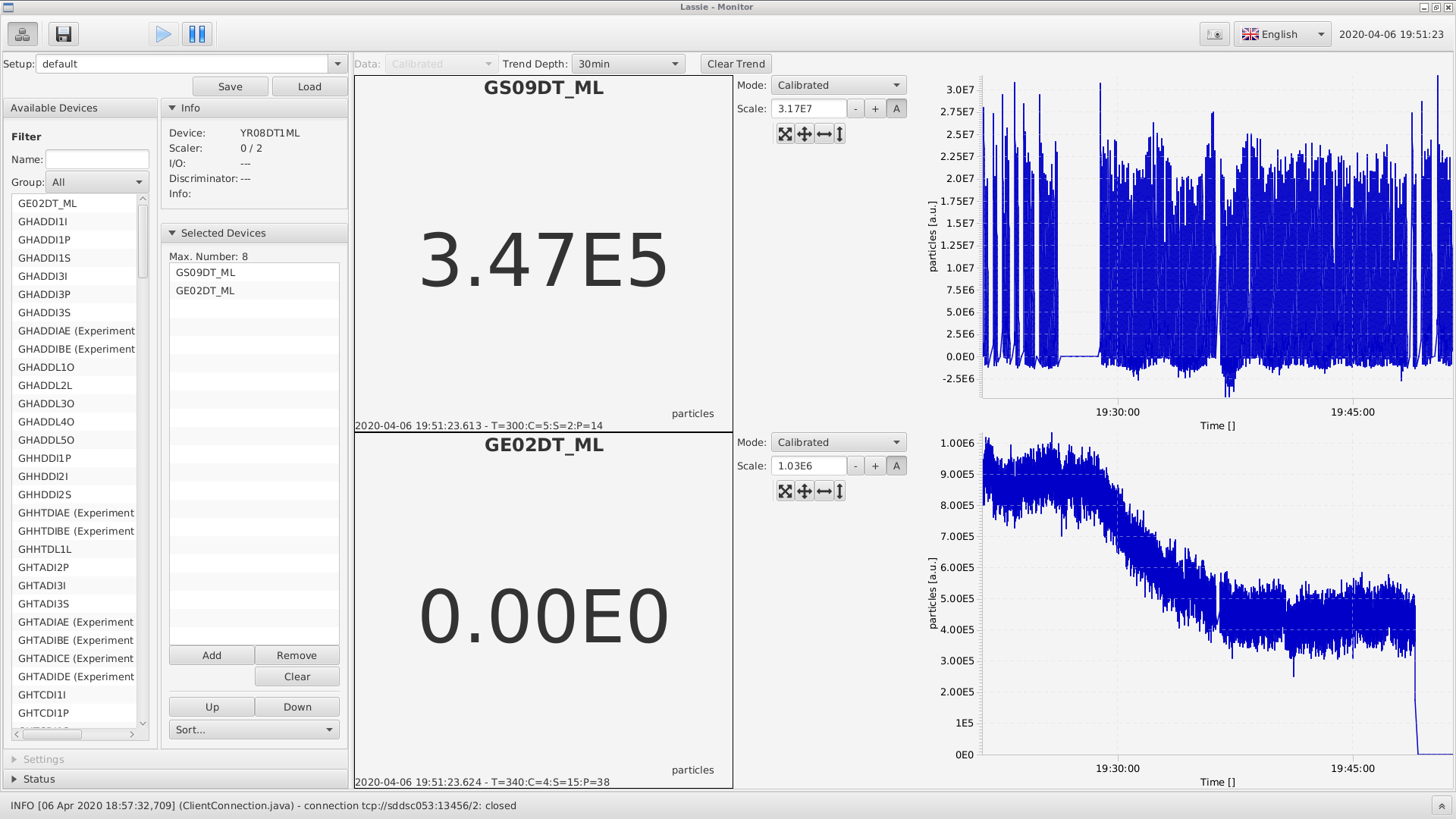

| Attachment 8: 2020-04-06_19-51-23-878.png

|

|

|

166

|

Mon Apr 6 09:34:58 2020 |

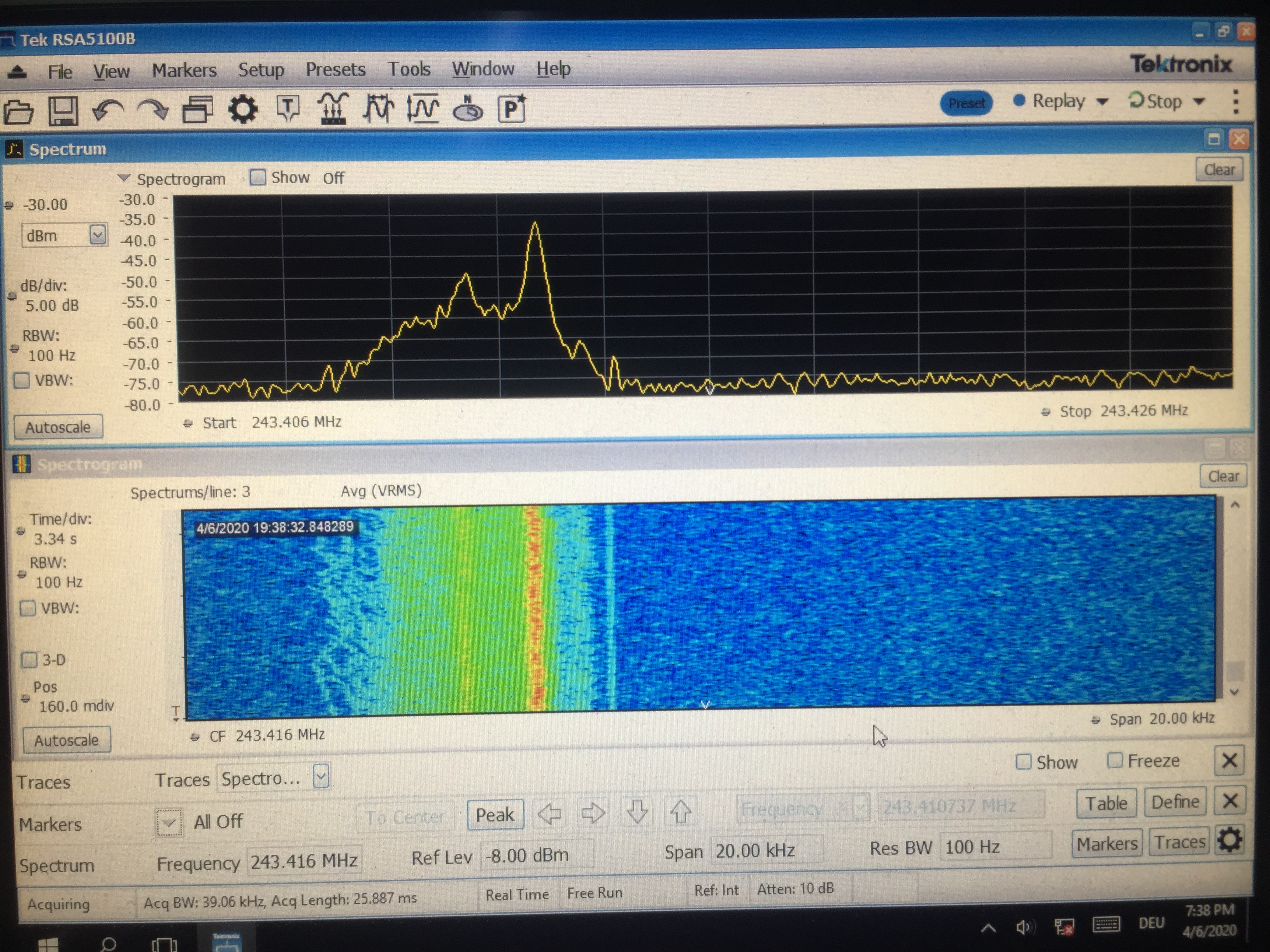

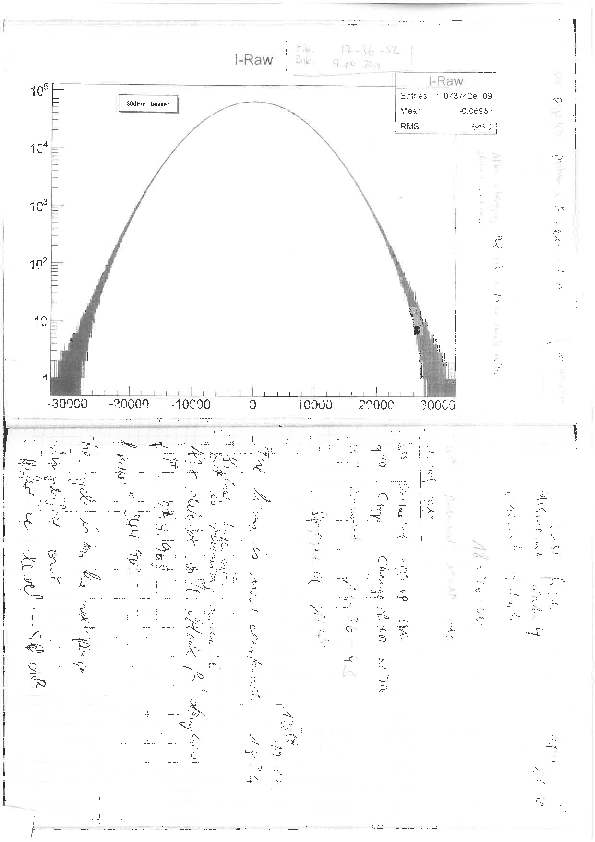

Shahab | Runs | Pictures from one and a half hour measurement | cheers! |

| Attachment 1: wideband_rec_001.PNG

|

|

|

167

|

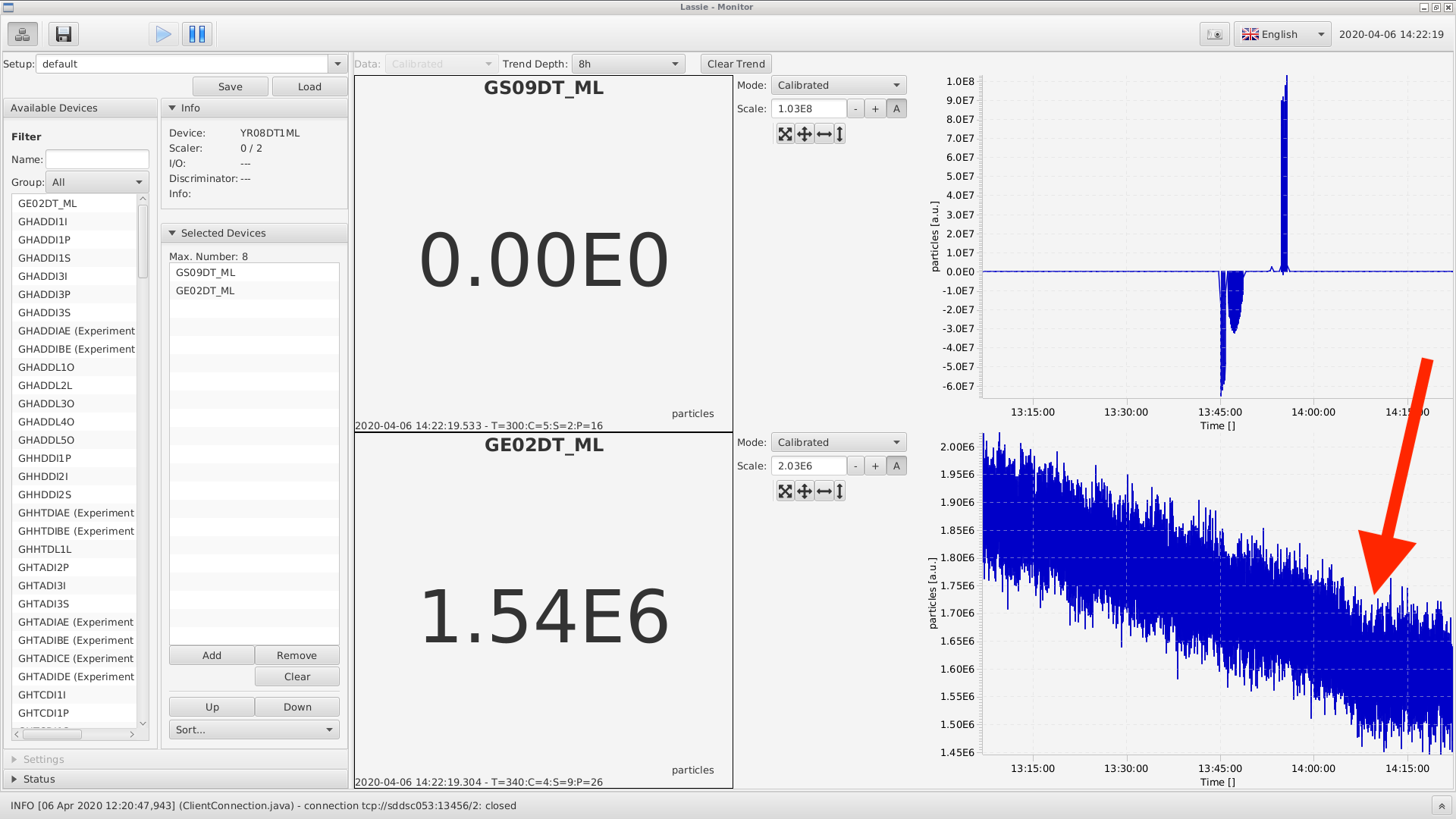

Mon Apr 6 14:17:54 2020 |

Yuri, Shahab | Runs | FRS valves | We saw reduction in ESR beam life. It turned out that FRS has opened valves and venting caused us reduction of the quality of vacuum in ESR leading to beam loss. We manged to closed GEE5VV so that now beam is stable somehow.

how could you guys!!!!

arrrrgggggggg!!!!!!! |

| Attachment 1: 2020-04-06_14-22-20-965.png

|

|

|

168

|

Mon Apr 6 14:57:04 2020 |

Shahab | Runs | cooler down | cooler component GECEBG2T again had to be reset. |

|

169

|

Mon Apr 6 20:03:50 2020 |

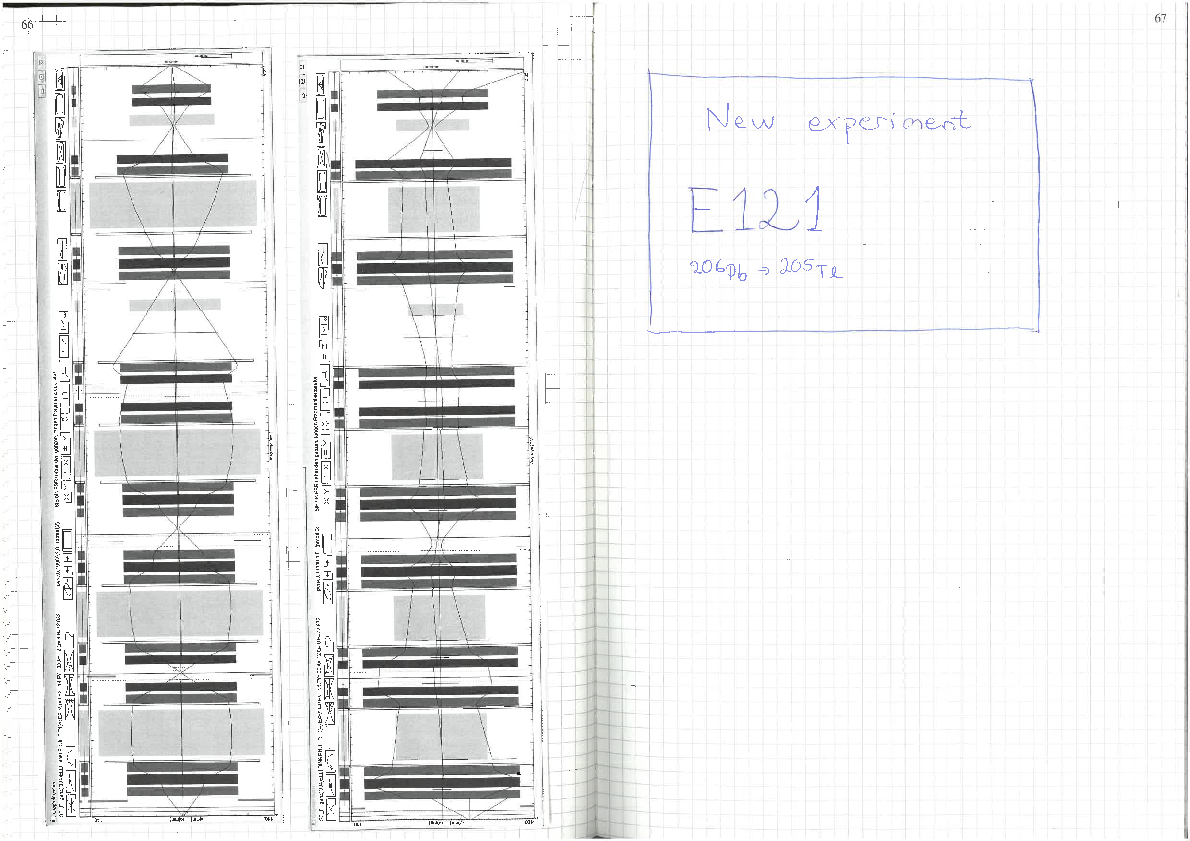

Ragan | General | Experiment finished )) | E121 experiment is finished with the last 10 hours measurement at 19:47 ))

Many thanks to everyone for there significant contributions )) |

|

170

|

Thu Apr 9 11:16:35 2020 |

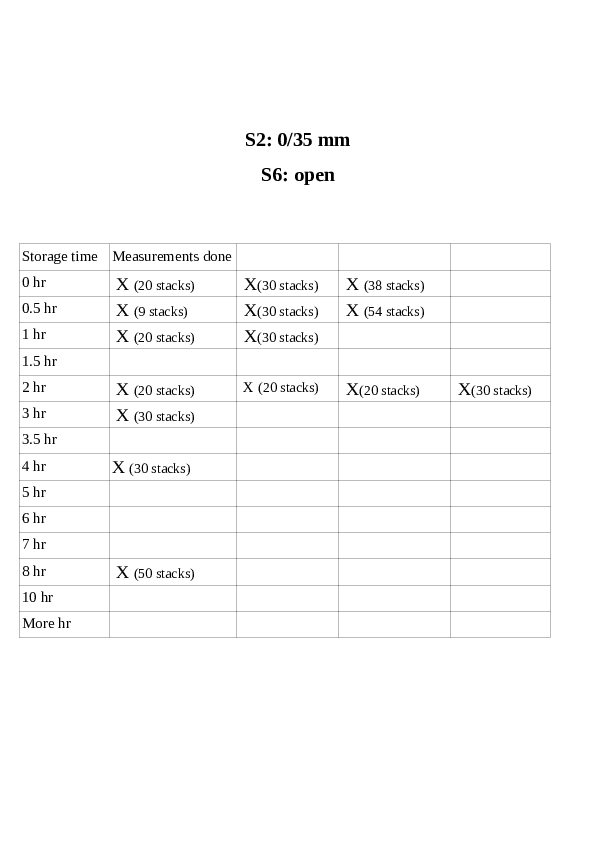

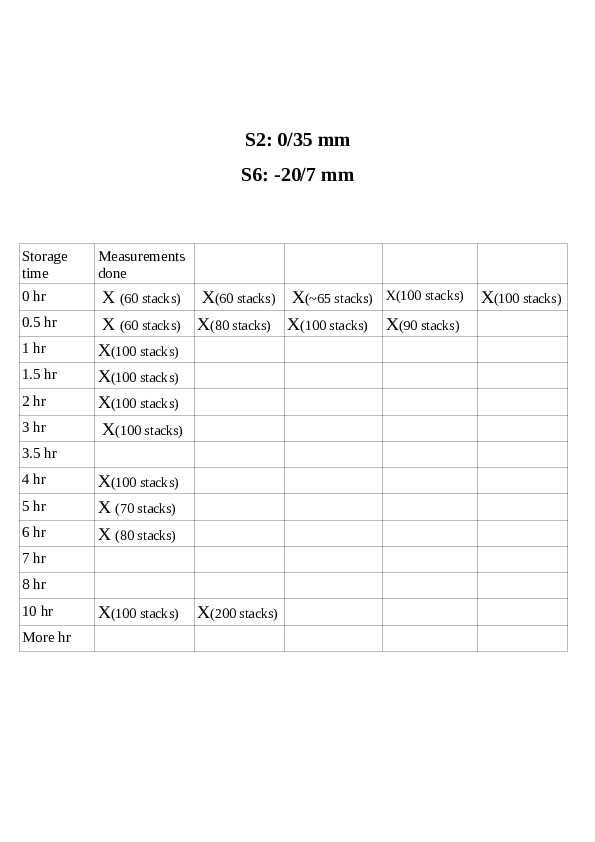

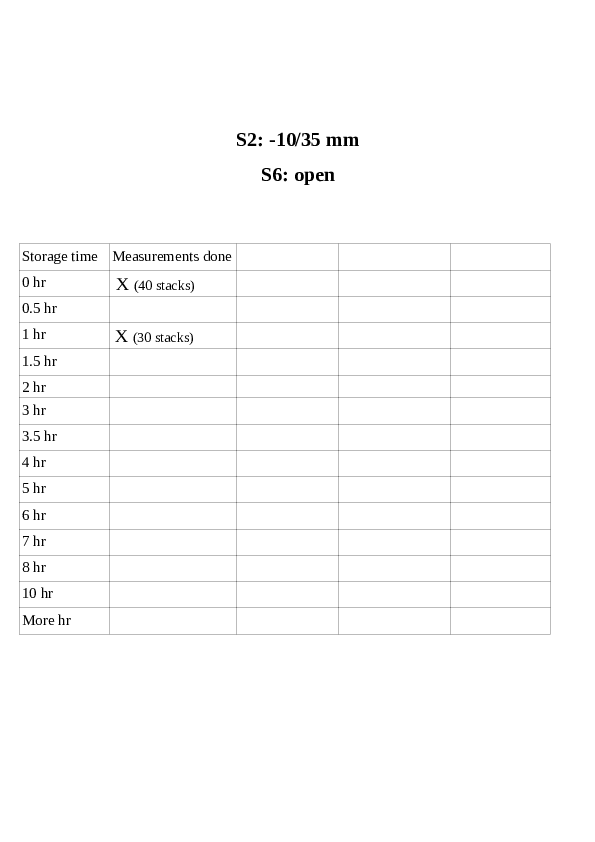

Ragan | General | Measurements done in the experiment | |

| Attachment 1: storage11.pdf

|

|

| Attachment 2: storage12.pdf

|

|

| Attachment 3: storage13.pdf

|

|

|

171

|

Thu Apr 9 11:47:28 2020 |

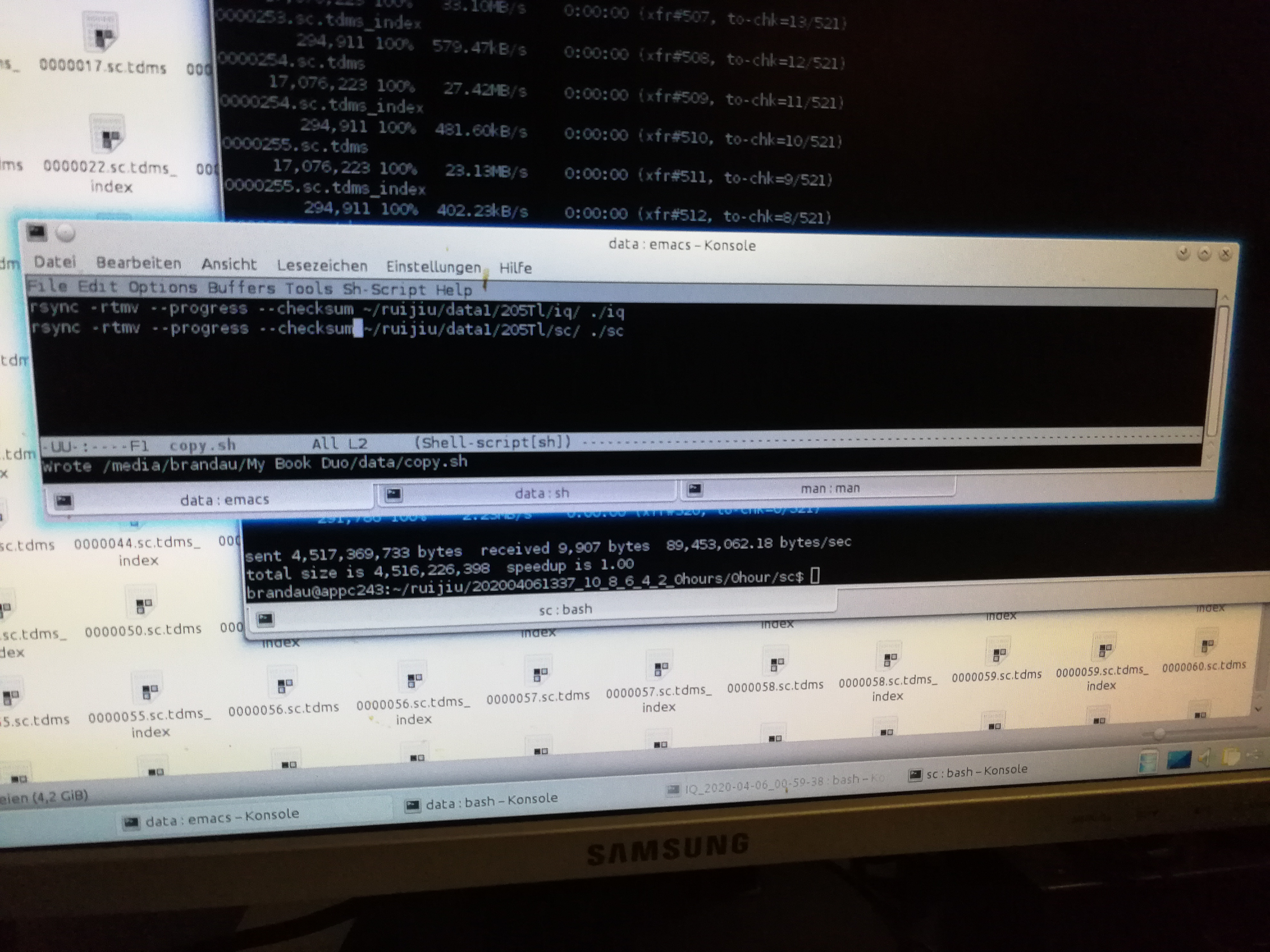

ruijiu | | backup data | 2020.4.8 12:00Started copying

data。

2020.4.9 11:52 Copied 6.3TB

data. The copy speed is 65-67MB/s.

2020.4.15 Bring the two USB hard disk to my office and connect them to lxg1298 computer.

Send email |

| Attachment 1: IMG_20200409_113155.jpg

|

|

|

172

|

Fri Apr 17 18:27:34 2020 |

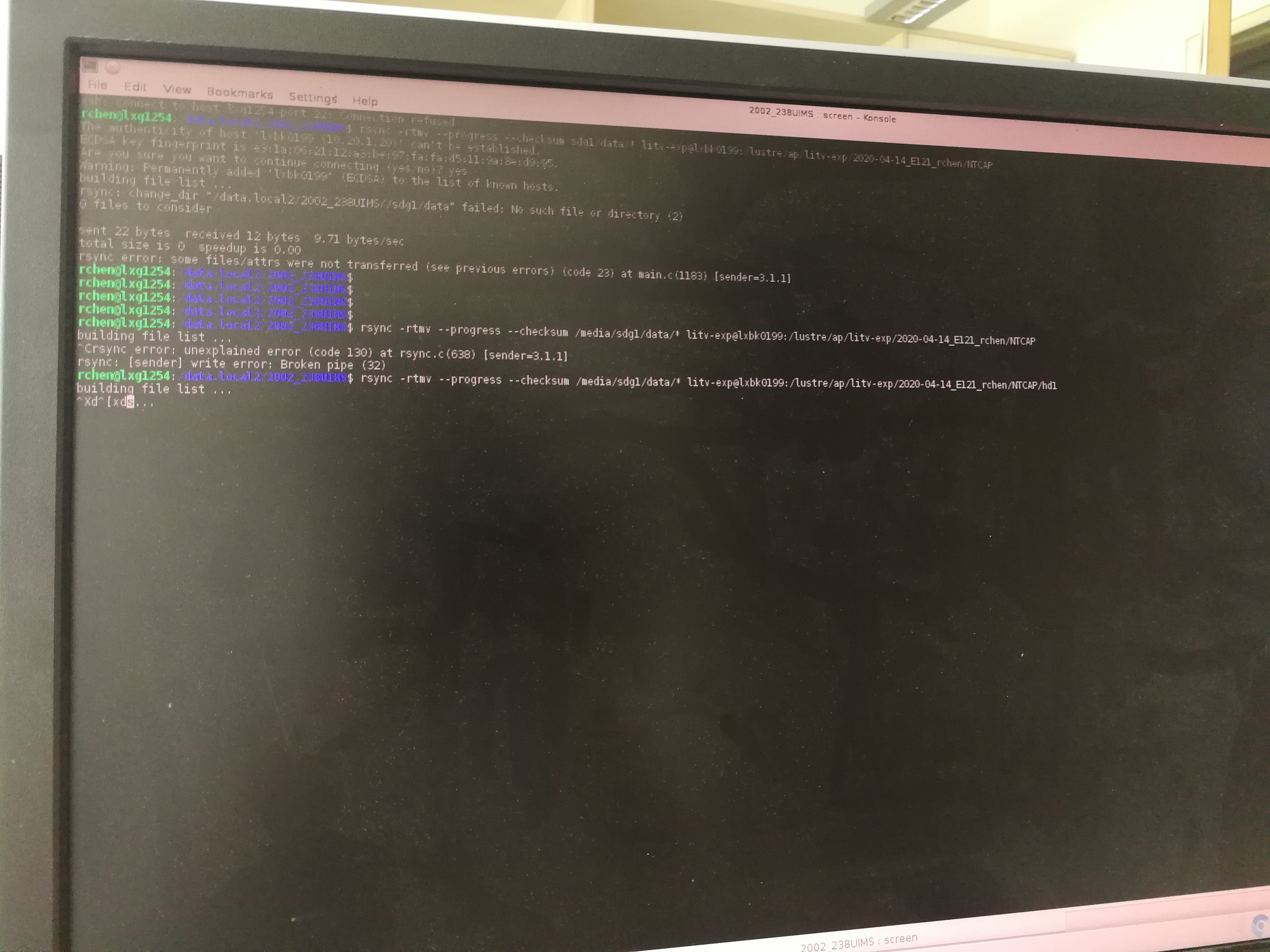

ruijiu | Analysis | backup data | 1.connect USB harddisk to computer lxg1254 and copy data to sever.

sync -rtmv --progress --checkSUD /media/sdgl/data/ litv-exp@sbk0l9:/lustre/ap/litv-exp/2020-

04-14 e121_rchen/NTCAP/hd1

2020.05.02 08:06 copied 11.88 TB to server. 1.8TB rest on hard disk. |

| Attachment 1: IMG_20200417_162202.jpg

|

|

|

173

|

Mon Apr 20 11:17:18 2020 |

Ragan | General | Logbook | |

| Attachment 1: logbook.pdf

|

|

| Attachment 2: combined_FRS.pdf

|

|

| Attachment 3: combined_data.pdf

|

|

|

174

|

Wed Aug 5 17:19:16 2020 |

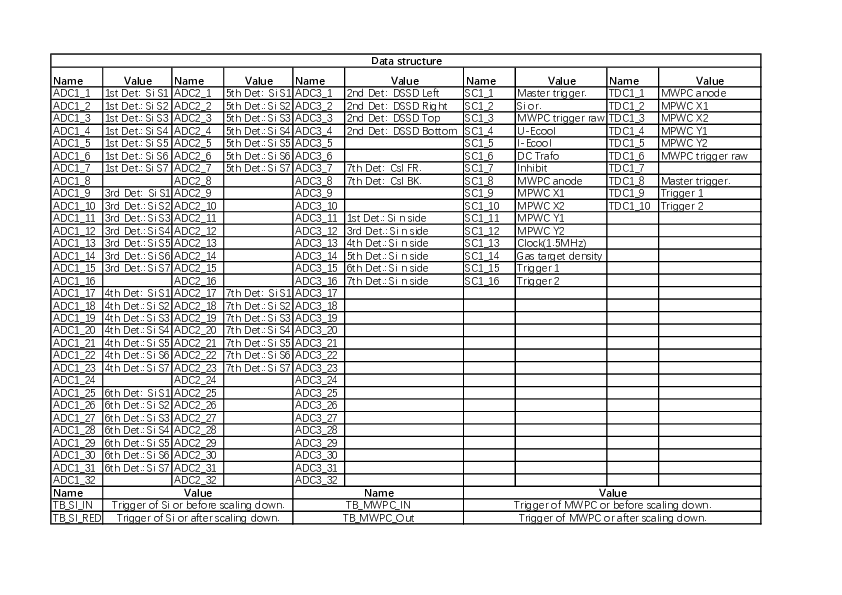

Rui-Jiu Chen | Analysis | Data structure | |

| Attachment 1: DataStructure.pdf

|

|

|

175

|

Thu Oct 1 22:20:03 2020 |

Jan | DAQ | final unpacker config | We identified an issue with randomly missing adc channels in all lmd-files before run 0273.

This led to errors in the unpacking process.

This issue is solved with the new config and mapping for the unpacker.

The respective files are attached here.

The unpacker is ready to use in /u/litv-exp/unpacker/unpackexps/E121

The adc issue is also understood. We deactivated the internal adc thresholds during the experiment, because we encountered the very same unpacker errors. This solved the problem for all later runs, but we forgot to think about a solution for the earlier runs.

Mea culpa.

Jan |

| Attachment 1: E121.spec

|

// -*- C++ -*-

ADC_CH(start, id)

{

MEMBER(DATA12 data[96]);

UINT32 item NOENCODE

{

0_15: channel = MATCH(id);

16_27: value;

28_31: unknown;

ENCODE(data[channel - start], (value=value));

}

}

SCALER(start)

{

MEMBER(DATA32 data[32]);

list(0 <= ch < 32)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel - start) / 2], (value=(high.value << 16) | low.value));

}

}

TDC(start)

{

MEMBER(DATA32 data);

UINT32 high NOENCODE

{

0_15: channel = MATCH(start);

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data,(value=(high.value << 16) | low.value));

}

TBOX(start)

{

MEMBER(DATA32 data[16]);

list(0 <= ch < 16)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel - start) / 2], (value=(high.value << 16) | low.value));

}

}

SUBEVENT(ESR)

{

tb_in[0] = TBOX(start = 0x300);

tb_inhibit[0] = TBOX(start = 0x380);

tb_red[0] = TBOX(start = 0x400);

// adc[0] = ADC(start = 0);

// adc[1] = ADC(start = 32);

// adc[2] = ADC(start = 64);

select several {

adc[0] = ADC_CH(start = 0 , id = 0);

adc[0] = ADC_CH(start = 0 , id = 1);

adc[0] = ADC_CH(start = 0 , id = 2);

adc[0] = ADC_CH(start = 0 , id = 3);

adc[0] = ADC_CH(start = 0 , id = 4);

adc[0] = ADC_CH(start = 0 , id = 5);

adc[0] = ADC_CH(start = 0 , id = 6);

adc[0] = ADC_CH(start = 0 , id = 7);

adc[0] = ADC_CH(start = 0 , id = 8);

adc[0] = ADC_CH(start = 0 , id = 9);

adc[0] = ADC_CH(start = 0 , id = 10);

adc[0] = ADC_CH(start = 0 , id = 11);

adc[0] = ADC_CH(start = 0 , id = 12);

adc[0] = ADC_CH(start = 0 , id = 13);

adc[0] = ADC_CH(start = 0 , id = 14);

adc[0] = ADC_CH(start = 0 , id = 15);

adc[0] = ADC_CH(start = 0 , id = 16);

adc[0] = ADC_CH(start = 0 , id = 17);

adc[0] = ADC_CH(start = 0 , id = 18);

adc[0] = ADC_CH(start = 0 , id = 19);

adc[0] = ADC_CH(start = 0 , id = 20);

adc[0] = ADC_CH(start = 0 , id = 21);

adc[0] = ADC_CH(start = 0 , id = 22);

adc[0] = ADC_CH(start = 0 , id = 23);

adc[0] = ADC_CH(start = 0 , id = 24);

adc[0] = ADC_CH(start = 0 , id = 25);

adc[0] = ADC_CH(start = 0 , id = 26);

adc[0] = ADC_CH(start = 0 , id = 27);

adc[0] = ADC_CH(start = 0 , id = 28);

adc[0] = ADC_CH(start = 0 , id = 29);

adc[0] = ADC_CH(start = 0 , id = 30);

adc[0] = ADC_CH(start = 0 , id = 31);

adc[1] = ADC_CH(start = 32, id = 32);

adc[1] = ADC_CH(start = 32, id = 33);

adc[1] = ADC_CH(start = 32, id = 34);

adc[1] = ADC_CH(start = 32, id = 35);

adc[1] = ADC_CH(start = 32, id = 36);

adc[1] = ADC_CH(start = 32, id = 37);

adc[1] = ADC_CH(start = 32, id = 38);

adc[1] = ADC_CH(start = 32, id = 39);

adc[1] = ADC_CH(start = 32, id = 40);

adc[1] = ADC_CH(start = 32, id = 41);

adc[1] = ADC_CH(start = 32, id = 42);

adc[1] = ADC_CH(start = 32, id = 43);

adc[1] = ADC_CH(start = 32, id = 44);

adc[1] = ADC_CH(start = 32, id = 45);

adc[1] = ADC_CH(start = 32, id = 46);

adc[1] = ADC_CH(start = 32, id = 47);

adc[1] = ADC_CH(start = 32, id = 48);

adc[1] = ADC_CH(start = 32, id = 49);

adc[1] = ADC_CH(start = 32, id = 50);

adc[1] = ADC_CH(start = 32, id = 51);

adc[1] = ADC_CH(start = 32, id = 52);

adc[1] = ADC_CH(start = 32, id = 53);

adc[1] = ADC_CH(start = 32, id = 54);

adc[1] = ADC_CH(start = 32, id = 55);

adc[1] = ADC_CH(start = 32, id = 56);

adc[1] = ADC_CH(start = 32, id = 57);

adc[1] = ADC_CH(start = 32, id = 58);

adc[1] = ADC_CH(start = 32, id = 59);

adc[1] = ADC_CH(start = 32, id = 60);

adc[1] = ADC_CH(start = 32, id = 61);

adc[1] = ADC_CH(start = 32, id = 62);

adc[1] = ADC_CH(start = 32, id = 63);

adc[2] = ADC_CH(start = 64, id = 64);

adc[2] = ADC_CH(start = 64, id = 65);

adc[2] = ADC_CH(start = 64, id = 66);

adc[2] = ADC_CH(start = 64, id = 67);

adc[2] = ADC_CH(start = 64, id = 68);

adc[2] = ADC_CH(start = 64, id = 69);

adc[2] = ADC_CH(start = 64, id = 70);

adc[2] = ADC_CH(start = 64, id = 71);

adc[2] = ADC_CH(start = 64, id = 72);

adc[2] = ADC_CH(start = 64, id = 73);

adc[2] = ADC_CH(start = 64, id = 74);

adc[2] = ADC_CH(start = 64, id = 75);

adc[2] = ADC_CH(start = 64, id = 76);

adc[2] = ADC_CH(start = 64, id = 77);

adc[2] = ADC_CH(start = 64, id = 78);

adc[2] = ADC_CH(start = 64, id = 79);

adc[2] = ADC_CH(start = 64, id = 80);

adc[2] = ADC_CH(start = 64, id = 81);

adc[2] = ADC_CH(start = 64, id = 82);

adc[2] = ADC_CH(start = 64, id = 83);

adc[2] = ADC_CH(start = 64, id = 84);

adc[2] = ADC_CH(start = 64, id = 85);

adc[2] = ADC_CH(start = 64, id = 86);

adc[2] = ADC_CH(start = 64, id = 87);

adc[2] = ADC_CH(start = 64, id = 88);

adc[2] = ADC_CH(start = 64, id = 89);

adc[2] = ADC_CH(start = 64, id = 90);

adc[2] = ADC_CH(start = 64, id = 91);

adc[2] = ADC_CH(start = 64, id = 92);

adc[2] = ADC_CH(start = 64, id = 93);

adc[2] = ADC_CH(start = 64, id = 94);

adc[2] = ADC_CH(start = 64, id = 95);

}

select optional {

scaler[0] = SCALER(start = 0x100);

}

select several {

tdc[0] = TDC(start = 0x200);

tdc[1] = TDC(start = 0x202);

tdc[2] = TDC(start = 0x204);

tdc[3] = TDC(start = 0x206);

tdc[4] = TDC(start = 0x208);

tdc[5] = TDC(start = 0x20a);

tdc[6] = TDC(start = 0x20c);

tdc[7] = TDC(start = 0x20e);

tdc[8] = TDC(start = 0x210);

tdc[9] = TDC(start = 0x212);

}

}

EVENT

{

esr = ESR(type = 10, subtype = 1);

}

#include "det_mapping.hh"

|

| Attachment 2: det_mapping.hh

|

SIGNAL( ADC1_1, esr.adc[0].data[0],

ADC1_32, esr.adc[0].data[31], DATA12);

SIGNAL( ADC2_1, esr.adc[1].data[0],

ADC2_32, esr.adc[1].data[31], DATA12);

SIGNAL( ADC3_1, esr.adc[2].data[0],

ADC3_32, esr.adc[2].data[31], DATA12);

SIGNAL( SC_1, esr.scaler[0].data[0],

SC_32, esr.scaler[0].data[31],DATA32);

SIGNAL( TDC_1, esr.tdc[0].data,

TDC_10, esr.tdc[9].data,DATA32);

SIGNAL( TB_SI_IN, esr.tb_in[0].data[0],DATA32);

SIGNAL( TB_SI_RED, esr.tb_red[0].data[0],DATA32);

SIGNAL( TB_MWPC_IN, esr.tb_in[0].data[1],DATA32);

SIGNAL( TB_MWPC_RED, esr.tb_red[0].data[1],DATA32);

|

|

176

|

Mon Nov 2 16:45:55 2020 |

Jan | DAQ | f_user & mbslog | Attached is the f_user.c and the mbslog.l files.

The readout function is for the following setup:

3x ADC CAEN V785

1x SCA CAEN V830

1x TDC CAEN V1190

1x Vulom TRB5 (triggerbox)

1x Vulom4b PEV (priority encoder)

1x TRIVA7

1x RIO4 R4L-47 |

| Attachment 1: f_user.c

|

/* CAEN V785 32 channel ADC*/

#include "stdio.h"

#include "s_veshe.h"

//----------------------------------------------

#define MWPC_downscale 0 // reduction = 2**MWPC_downscale

#define SI_downscale 0

#define VME_BASE 0x00000000

#define TB__OFFSET 0x05000000

#define TB__No_Ch 16

#define TB__No_Ch_enabled 16

#define TB__lmd_offset 0x300

#define ADC_V785__VME_OFFSET 0x00200000

#define ADC_V785__VME_SIZE 0x10000

#define ADC_V785__No_Ch 32

#define ADC_V785__lmd_offset 0x00

#define ADC_V785__No_Mod 3

#define SCA_V830_VME_OFFSET 0x00000000

#define SCA_V830_VME_SIZE 0x10000

#define SCA_V830__No_Ch 32

#define SCA_V830__lmd_offset 0x100

#define TDC_V1190a__OFFSET 0x01200000

#define TDC_V1190a__VME_SIZE 0x10000

#define TDC_V1190a__No_Ch 128

#define TDC_V1190a__No_hit_per_Ch 1 //only single hit allowed

#define TDC_V1190a__lmd_offset 0x200

#define TDC_V1190a__win_width 200

#define TDC_V1190a__win_offset -180

const long TB_Ch_enable_reg_F_0 = 0x00FF ;

//------------//

// scale down: ch00, ch01, ch02

const long TB_scale_down_0_F[TB__No_Ch] ={ SI_downscale,MWPC_downscale,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

const long ADC_threshold_value = 0x0000 ;

/*****************************************************************************/

/*

* all pointer wllhich are used for read/write operations in the functions

* f_user_init and f_user_readout must be defined here as static variables

*/

static long volatile *pl_VME_virtual_mem_base ;

static long volatile *pl_trig_vme_str; // triva status register

static long ll_evt_ctr = 0;

/* TB - Triggerbox on Vulom3 */

static long volatile *pl_TB__base ;

static long volatile *pl_TB__Ch_enable_reg_F_0 ;

static long volatile *pl_TB__scale_down_7_0 ;

static long volatile *pl_TB__scale_down_F_8 ;

static long volatile *pl_TB__latch_reg ;

static long volatile *pl_TB__version ;

static long volatile *pl_TB__scaler_inp [TB__No_Ch];

static long volatile *pl_TB__scaler_inhib [TB__No_Ch] ;

static long volatile *pl_TB__scaler_after_reduction [TB__No_Ch] ;

long TB__scaler_inp_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

long TB__scaler_inhib_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

long TB__scaler_after_reduction_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

/* ADC - Analog to Digital Converter CAEN V785AH */

static long volatile *pl_ADC_V785__base [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__firm_rev [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__geo_adr [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__oui_msb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__oui [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__oui_lsb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__version [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id_msb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id_lsb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__revision [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__serial_msb [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__serial_lsb [ADC_V785__No_Mod];

static long volatile *pl_ADC_V785__outp_buffer [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_set_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_clr_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__stat_reg_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__ctrl_reg_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__stat_reg_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_set_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_clr_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__threshs[ADC_V785__No_Ch] [ADC_V785__No_Mod];

/* SCA - Scaler CAEN V830 */

static long volatile *pl_SCA_V830__base;

static long volatile *pl_SCA_V830__outp_buffer;

static long volatile *pl_SCA_V830__counter[SCA_V830__No_Ch];

static short volatile *ps_SCA_V830__scaler_clr;

static short volatile *ps_SCA_V830__scaler_status_reg;

static short volatile *ps_SCA_V830__fixed_code;

static short volatile *ps_SCA_V830__manuf_mod_type;

static short volatile *ps_SCA_V830__version_series;

static short volatile *ps_SCA_V830__firm_rev;

static short volatile *ps_SCA_V830__geo_adr;

static short volatile *ps_SCA_V830__oui_msb ;

static short volatile *ps_SCA_V830__oui ;

static short volatile *ps_SCA_V830__oui_lsb ;

static short volatile *ps_SCA_V830__version ;

static short volatile *ps_SCA_V830__board_id_msb ;

static short volatile *ps_SCA_V830__board_id ;

static short volatile *ps_SCA_V830__board_id_lsb ;

static short volatile *ps_SCA_V830__revision ;

static short volatile *ps_SCA_V830__serial_msb;

static short volatile *ps_SCA_V830__serial_lsb;

static short volatile *ps_SCA_V830__bit_set_1 ;

static short volatile *ps_SCA_V830__bit_clr_1 ;

static short volatile *ps_SCA_V830__stat_reg_1;

static short volatile *ps_SCA_V830__ctrl_reg_1;

static short volatile *ps_SCA_V830__sw_clr_reg ;

long SCA_V830__data_old [SCA_V830__No_Ch] ;

/* TDC - Time to Digital Converter CAEN V1190a */

static long volatile *pl_TDC_V1190a__base ;

static long volatile *pl_TDC_V1190a__outp_buffer ;

static short volatile *ps_TDC_V1190a__ctrl_reg_1 ;

static short volatile *ps_TDC_V1190a__stat_reg_1 ;

static short volatile *ps_TDC_V1190a__geo_adr ;

static short volatile *ps_TDC_V1190a__module_reset ;

static short volatile *ps_TDC_V1190a__sw_clr ;

static short volatile *ps_TDC_V1190a__sw_evt_reset ;

static short volatile *ps_TDC_V1190a__sw_trig ;

static short volatile *pl_TDC_V1190a__evt_cnt ;

static short volatile *ps_TDC_V1190a__firmware_rev ;

static short volatile *ps_TDC_V1190a__micro_reg ;

static short volatile *ps_TDC_V1190a__micro_hdshk_reg ;

static short volatile *ps_TDC_V1190a__oui_2 ;

static short volatile *ps_TDC_V1190a__oui_1 ;

static short volatile *ps_TDC_V1190a__oui_0 ;

static short volatile *ps_TDC_V1190a__board_ver ;

static short volatile *ps_TDC_V1190a__board_id_2 ;

static short volatile *ps_TDC_V1190a__board_id_1 ;

static short volatile *ps_TDC_V1190a__board_id_0 ;

static short volatile *ps_TDC_V1190a__revision_3 ;

static short volatile *ps_TDC_V1190a__revision_2 ;

static short volatile *ps_TDC_V1190a__revision_1 ;

static short volatile *ps_TDC_V1190a__revision_0 ;

static short volatile *ps_TDC_V1190a__serial_1 ;

static short volatile *ps_TDC_V1190a__serial_0 ;

int l_mod;

int l_ch;

long l_event_counter;

/*****************************************************************************/

/*****************************************************************************/

int f_user_get_virt_ptr (long *pl_loc_hwacc, long pl_rem_cam[])

{

int i;

long l_i, l_j;

/*

* create virtual pointer to be used in f_user_init and f_user_readout

*/

l_event_counter = 0;

//***************

// CAEN mapping

//***************

{ //#ifdef CAEN

pl_VME_virtual_mem_base = (long*) ((long)pl_loc_hwacc) ;

} //#endif // CAEN

// *****************************************************************************/

{

// * create virtual pointer to be used in f_user_init and f_user_readout

/*------------------------------------------------------------------------------*/

/* TB on VULOM3 */

/*------------------------------------------------------------------------------*/

{

pl_TB__base = (long*) ((long) pl_VME_virtual_mem_base + TB__OFFSET ) ;

pl_TB__Ch_enable_reg_F_0 = (long*) ( (long) pl_TB__base + 0x0000 );

pl_TB__scale_down_7_0 = (long*) ( (long) pl_TB__base + 0x0004 );

pl_TB__scale_down_F_8 = (long*) ( (long) pl_TB__base + 0x0008 ) ;

pl_TB__latch_reg = (long*) ( (long) pl_TB__base + 0x000c );

pl_TB__version = (long*) ( (long) pl_TB__base + 0x003c );

long l_ch ;

for (l_ch=0; l_ch<TB__No_Ch; l_ch++)

{ pl_TB__scaler_inp[l_ch] =

(long*) ( (long) pl_TB__base + 0x0040 +(l_ch*4));

pl_TB__scaler_inhib[l_ch] =

(long*) ( (long) pl_TB__base + 0x0080 +(l_ch*4));

pl_TB__scaler_after_reduction[l_ch] =

(long*) ( (long) pl_TB__base + 0x00c0 +(l_ch*4));

}

}

/*------------------------------------------------------------------------------*/

/* ADC CAEN 785AH */

/*------------------------------------------------------------------------------*/

for (l_mod = 0 ; l_mod < ADC_V785__No_Mod; l_mod++)

{

pl_ADC_V785__base[l_mod] = (long*) ( (long) pl_VME_virtual_mem_base + ADC_V785__VME_OFFSET + l_mod * ADC_V785__VME_SIZE) ;

ps_ADC_V785__firm_rev[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1000 );

ps_ADC_V785__geo_adr[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1002 );

ps_ADC_V785__oui_msb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8026 );

ps_ADC_V785__oui[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802a );

ps_ADC_V785__oui_lsb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802e );

ps_ADC_V785__version[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8032 );

ps_ADC_V785__board_id_msb[l_mod]= (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8036 );

ps_ADC_V785__board_id[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802a );

ps_ADC_V785__board_id_lsb[l_mod]= (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802e );

ps_ADC_V785__revision[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x804e );

ps_ADC_V785__serial_msb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8f02 );

ps_ADC_V785__serial_lsb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8f06 );

pl_ADC_V785__outp_buffer[l_mod]= (long*) ( (long) pl_ADC_V785__base[l_mod] + 0x0000 );

ps_ADC_V785__bit_set_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1006 );

ps_ADC_V785__bit_clr_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1008 );

ps_ADC_V785__stat_reg_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x100e );

ps_ADC_V785__ctrl_reg_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1010 );

ps_ADC_V785__stat_reg_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1022 );

ps_ADC_V785__bit_set_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1032 );

ps_ADC_V785__bit_clr_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1034 );

for (l_ch=0; l_ch<ADC_V785__No_Ch; l_ch++)

{

ps_ADC_V785__threshs[l_ch][l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1080 + l_ch * 0x0002 );

}

}

/*------------------------------------------------------------------------------*/

/* Scaler CAEN V830 */

... 832 more lines ...

|

| Attachment 2: mbslog.l

|

22-Oct-18 16:39:14#R4-54 :msg_log :Message logger running

22-Oct-18 16:39:21+R4-54 :dispatch :>>> Start procedure "startup.scom" break mode 1

22-Oct-18 16:39:21#R4-54 :dispatch :start task m_util

22-Oct-18 16:39:22#R4-54 :util :task m_util started

22-Oct-18 16:39:22#R4-54 :util :load setup setup.usf

22-Oct-18 16:39:22#R4-54 :util :setup file setup.usf successfully loaded

22-Oct-18 16:39:22+R4-54 :util :load setup finished (x0)

22-Oct-18 16:39:22#R4-54 :util :set trig_mod

22-Oct-18 16:39:22#R4-54 :util :trigger module set up as MASTER, crate nr: 0

22-Oct-18 16:39:22+R4-54 :util :set trig_mod finished (x0)

22-Oct-18 16:39:22#R4-54 :util :enable irq

22-Oct-18 16:39:23+R4-54 :util :enable irq finished (x0)

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_read_meb "./m_read_meb"

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_collector

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_transport

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_stream_serv

22-Oct-18 16:39:24#R4-54 :dispatch :start task m_daq_rate

22-Oct-18 16:39:26!R4-54 :read_meb :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:39:27!R4-54 :collector :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:39:27#R4-54 :read_meb :task m_read_meb started

22-Oct-18 16:39:27#R4-54 :stream_serv:task m_stream_serv started

22-Oct-18 16:39:27#R4-54 :collector :task m_collector started

22-Oct-18 16:39:27#R4-54 :transport :task m_transport started

22-Oct-18 16:39:27#R4-54 :transport :enable tcp

22-Oct-18 16:39:27#R4-54 :transport :starting server in inclusive mode

22-Oct-18 16:39:27+R4-54 :transport :enable tcp finished (x0)

22-Oct-18 16:39:27+R4-54 :dispatch :>>> End procedure "startup.scom"

22-Oct-18 16:39:27#R4-54 :transport :waiting for client (port 6000)

22-Oct-18 16:39:30#R4-54 :util :start acquisition

22-Oct-18 16:39:30+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:39:31#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:39:31#R4-54 :collector :acquisition running

22-Oct-18 16:42:19#R4-54 :util :stop acquisition

22-Oct-18 16:42:21+R4-54 :util :stop acquisition finished (x0)

22-Oct-18 16:42:21#R4-54 :collector :acquisition NOT running

22-Oct-18 16:42:21#R4-54 :read_meb :found trig type 15 == stop acquisition

22-Oct-18 16:45:08#R4-54 :util :start acquisition

22-Oct-18 16:45:08+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:45:09#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:45:10#R4-54 :collector :acquisition running

22-Oct-18 16:45:19!R4-54 :dispatch :Key "events" > invalid value "v"!

22-Oct-18 16:45:19!R4-54 :dispatch :Command not executed

22-Oct-18 16:45:19!R4-54 :dispatch :Command "type event v 10" finished with argument error (20)

22-Oct-18 16:45:34#R4-54 :transport :type event -v 10

22-Oct-18 16:45:34+R4-54 :transport :type event finished (x0)

22-Oct-18 16:45:41#R4-54 :util :stop acquisition

22-Oct-18 16:45:43+R4-54 :util :stop acquisition finished (x0)

22-Oct-18 16:45:43#R4-54 :collector :acquisition NOT running

22-Oct-18 16:45:43#R4-54 :read_meb :found trig type 15 == stop acquisition

22-Oct-18 16:45:52#R4-54 :util :start acquisition

22-Oct-18 16:45:52+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:45:52#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:45:53#R4-54 :collector :acquisition running

22-Oct-18 16:46:36#R4-54 :transport :type event -v 10

22-Oct-18 16:46:36+R4-54 :transport :type event finished (x0)

22-Oct-18 16:52:38#R4-54 :stream_serv:140.181.81.77 connected

22-Oct-18 16:55:03!R4-54 :stream_serv:received CLOSE, client disconnected!

22-Oct-18 16:55:25#R4-54 :msg_log :Message logger running

22-Oct-18 16:58:29+R4-54 :dispatch :>>> Start procedure "startup.scom" break mode 1

22-Oct-18 16:58:29#R4-54 :dispatch :start task m_util

22-Oct-18 16:58:30#R4-54 :util :task m_util started

22-Oct-18 16:58:30#R4-54 :util :load setup setup.usf

22-Oct-18 16:58:30#R4-54 :util :setup file setup.usf successfully loaded

22-Oct-18 16:58:30+R4-54 :util :load setup finished (x0)

22-Oct-18 16:58:30#R4-54 :util :set trig_mod

22-Oct-18 16:58:30#R4-54 :util :trigger module set up as MASTER, crate nr: 0

22-Oct-18 16:58:30+R4-54 :util :set trig_mod finished (x0)

22-Oct-18 16:58:30#R4-54 :util :enable irq

22-Oct-18 16:58:30+R4-54 :util :enable irq finished (x0)

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_read_meb "./m_read_meb"

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_collector

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_transport

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_stream_serv

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_daq_rate

22-Oct-18 16:58:34!R4-54 :read_meb :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:58:35!R4-54 :collector :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:58:37#R4-54 :read_meb :task m_read_meb started

22-Oct-18 16:58:37#R4-54 :collector :task m_collector started

22-Oct-18 16:58:37#R4-54 :stream_serv:task m_stream_serv started

22-Oct-18 16:58:37#R4-54 :transport :task m_transport started

22-Oct-18 16:58:37#R4-54 :transport :enable tcp

22-Oct-18 16:58:37#R4-54 :transport :starting server in inclusive mode

22-Oct-18 16:58:37+R4-54 :transport :enable tcp finished (x0)

22-Oct-18 16:58:37+R4-54 :dispatch :>>> End procedure "startup.scom"

22-Oct-18 16:58:37#R4-54 :transport :waiting for client (port 6000)

22-Oct-18 16:59:50#R4-54 :stream_serv:140.181.81.77 connected

22-Oct-18 17:00:03#R4-54 :util :start acquisition

22-Oct-18 17:00:03+R4-54 :util :start acquisition finished (x0)

22-Oct-18 17:00:03#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 17:00:03#R4-54 :collector :acquisition running

22-Oct-18 17:01:26!R4-54 :dispatch :Key "events" > invalid value "v"!

22-Oct-18 17:01:26!R4-54 :dispatch :Command not executed

22-Oct-18 17:01:26!R4-54 :dispatch :Command "type event v" finished with argument error (20)

22-Oct-18 17:01:29#R4-54 :transport :type event -v

22-Oct-18 17:01:29+R4-54 :transport :type event finished (x0)

22-Oct-18 17:02:29#R4-54 :transport :type event -v

22-Oct-18 17:02:29+R4-54 :transport :type event finished (x0)

23-Oct-18 10:47:03#R4-54 :transport :type event -v 5

23-Oct-18 10:47:03+R4-54 :transport :type event finished (x0)

23-Oct-18 14:07:59!R4-54 :stream_serv:NODATA, client disconnected!

23-Oct-18 14:37:32#R4-54 :msg_log :Message logger running

23-Oct-18 14:38:37!R4-54 :dispatch :>>> Procedure "startup.scom" not found!

23-Oct-18 14:38:43#R4-54 :util :data acquisition was already started ���

23-Oct-18 14:39:03#R4-54 :util :show acquisition

23-Oct-18 14:39:04+R4-54 :util :show acquisition finished (x0)

23-Oct-18 14:41:16!R4-54 :dispatch :Command not found: "-R4-54"!

23-Oct-18 14:41:23!R4-54 :dispatch :Command key missing: type

23-Oct-18 14:41:55#R4-54 :transport :type event -v

23-Oct-18 14:42:11#R4-54 :transport :type event -v 3

23-Oct-18 14:59:29#R4-54 :util :start acquisition

23-Oct-18 14:59:29+R4-54 :util :start acquisition finished (x0)

23-Oct-18 14:59:45#R4-54 :transport :type event -v

23-Oct-18 15:00:39#R4-54 :util :show acquisition

23-Oct-18 15:00:40+R4-54 :util :show acquisition finished (x0)

23-Oct-18 15:49:53#R4-54 :util :show acquisition

23-Oct-18 15:49:54+R4-54 :util :show acquisition finished (x0)

23-Oct-18 15:50:15+R4-54 :transport :type event finished (x0)

23-Oct-18 15:55:44!R4-54 :stream_serv:received CLOSE, client disconnected!

23-Oct-18 16:11:45!R4-54 :stream_serv:received CLOSE, client disconnected!

23-Oct-18 16:17:30#R4-54 :stream_serv:show stream_serv

23-Oct-18 16:17:30#R4-54 :stream_serv:Streams: total 7622, sent 3811 (50.0%), free 8.

23-Oct-18 16:17:58#R4-54 :stream_serv:set stream_serv 1

23-Oct-18 16:17:58+R4-54 :stream_serv:set stream_serv finished (x0)

23-Oct-18 16:18:04#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:18:04+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:18:15#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:18:15+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:10#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:10+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:14#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:14+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:22#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:22+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:25#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:25+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:34!R4-54 :dispatch :value 0

23-Oct-18 16:19:34!R4-54 :dispatch :Command not executed

23-Oct-18 16:19:41#R4-54 :stream_serv:set stream_serv 1

23-Oct-18 16:19:41+R4-54 :stream_serv:set stream_serv finished (x0)

23-Oct-18 16:20:03#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:03+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:20:08#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:08+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:20:11#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:11+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:24:14#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:24:14+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:26:57#R4-54 :stream_serv:140.181.81.77 connected

24-Oct-18 15:05:22#R4-54 :util :stop acquisition

24-Oct-18 15:05:24#R4-54 :collector :acquisition NOT running

26-Oct-18 14:38:49#R4-55 :msg_log :Message logger running

26-Oct-18 14:38:59+R4-55 :dispatch :>>> Start procedure "startup.scom" break mode 1

26-Oct-18 14:38:59#R4-55 :dispatch :start task m_util

26-Oct-18 14:39:02#R4-55 :util :task m_util started

26-Oct-18 14:39:02#R4-55 :util :load setup setup.usf

26-Oct-18 14:39:02#R4-55 :util :setup file setup.usf successfully loaded

26-Oct-18 14:39:02+R4-55 :util :load setup finished (x0)

26-Oct-18 14:39:02#R4-55 :util :set trig_mod

26-Oct-18 14:39:02#R4-55 :util :trigger module set up as MASTER, crate nr: 0

26-Oct-18 14:39:02+R4-55 :util :set trig_mod finished (x0)

26-Oct-18 14:39:02#R4-55 :util :enable irq

26-Oct-18 14:39:02+R4-55 :util :enable irq finished (x0)

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_read_meb "./m_read_meb"

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_collector

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_transport

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_stream_serv

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_daq_rate

26-Oct-18 14:39:07!R4-55 :read_meb :Pipe type 0: smem_create for base 0x8000000

26-Oct-18 14:39:07!R4-55 :collector :Pipe type 0: smem_create for base 0x8000000

26-Oct-18 14:39:08#R4-55 :read_meb :task m_read_meb started

26-Oct-18 14:39:09#R4-55 :stream_serv:task m_stream_serv started

26-Oct-18 14:39:09#R4-55 :collector :task m_collector started

26-Oct-18 14:39:09#R4-55 :transport :task m_transport started

26-Oct-18 14:39:09#R4-55 :transport :enable tcp

26-Oct-18 14:39:09#R4-55 :transport :starting server in inclusive mode

26-Oct-18 14:39:09+R4-55 :transport :enable tcp finished (x0)

26-Oct-18 14:39:09+R4-55 :dispatch :>>> End procedure "startup.scom"

26-Oct-18 14:39:09#R4-55 :transport :waiting for client (port 6000)

26-Oct-18 14:39:23#R4-55 :util :start acquisition

26-Oct-18 14:39:23+R4-55 :util :start acquisition finished (x0)

26-Oct-18 14:39:23#R4-55 :read_meb :found trig type 14 == start acquisition

26-Oct-18 14:39:24#R4-55 :collector :acquisition running

26-Oct-18 14:39:30#R4-55 :transport :type event -v 4

26-Oct-18 14:39:30+R4-55 :transport :type event finished (x0)

26-Oct-18 14:39:33#R4-55 :transport :type event -v 4

26-Oct-18 14:39:33+R4-55 :transport :type event finished (x0)

26-Oct-18 14:49:28#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 14:56:07!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 14:58:24#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 15:11:09!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 15:11:54#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 15:13:41!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 15:46:38#R4-55 :util :stop acquisition

26-Oct-18 15:46:40+R4-55 :util :stop acquisition finished (x0)

26-Oct-18 15:46:40#R4-55 :collector :acquisition NOT running

26-Oct-18 15:46:40#R4-55 :read_meb :found trig type 15 == stop acquisition

28-Nov-18 10:43:17#R4L-60 :msg_log :Message logger running

28-Nov-18 10:43:22+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_util

28-Nov-18 10:43:22#R4L-60 :util :task m_util started

28-Nov-18 10:43:22#R4L-60 :util :load setup setup.usf

28-Nov-18 10:43:22#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 10:43:22+R4L-60 :util :load setup finished (x0)

28-Nov-18 10:43:22#R4L-60 :util :set trig_mod

28-Nov-18 10:43:22#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 10:43:22+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 10:43:22#R4L-60 :util :enable irq

28-Nov-18 10:43:22+R4L-60 :util :enable irq finished (x0)

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_collector

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_transport

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 10:43:22!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:43:22#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:43:23!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:43:23#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:43:23#R4L-60 :transport :task m_transport started

28-Nov-18 10:43:23#R4L-60 :transport :enable tcp

28-Nov-18 10:43:23#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 10:43:23+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 10:43:23+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 10:43:23#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 10:43:23#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 10:48:22#R4L-60 :msg_log :Message logger running

28-Nov-18 10:48:25+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_util

28-Nov-18 10:48:25#R4L-60 :util :task m_util started

28-Nov-18 10:48:25#R4L-60 :util :load setup setup.usf

28-Nov-18 10:48:25#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 10:48:25+R4L-60 :util :load setup finished (x0)

28-Nov-18 10:48:25#R4L-60 :util :set trig_mod

28-Nov-18 10:48:25#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 10:48:25+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 10:48:25#R4L-60 :util :enable irq

28-Nov-18 10:48:25+R4L-60 :util :enable irq finished (x0)

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_collector

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_transport

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 10:48:25!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:48:25#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:48:25!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:48:25#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:48:25#R4L-60 :transport :task m_transport started

28-Nov-18 10:48:25#R4L-60 :transport :enable tcp

28-Nov-18 10:48:25#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 10:48:25+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 10:48:25+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 10:48:25#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 10:48:25#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 10:48:41#R4L-60 :msg_log :exiting.. SIGTERM (kill) signal ���

28-Nov-18 11:01:34#R4L-60 :msg_log :Message logger running

28-Nov-18 11:01:37+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_util

28-Nov-18 11:01:37#R4L-60 :util :task m_util started

28-Nov-18 11:01:37#R4L-60 :util :load setup setup.usf

28-Nov-18 11:01:37#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 11:01:37+R4L-60 :util :load setup finished (x0)

28-Nov-18 11:01:37#R4L-60 :util :set trig_mod

28-Nov-18 11:01:37#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 11:01:37+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 11:01:37#R4L-60 :util :enable irq

28-Nov-18 11:01:37+R4L-60 :util :enable irq finished (x0)

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_collector

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_transport

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 11:01:38!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 11:01:38#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 11:01:38!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 11:01:38#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 11:01:38#R4L-60 :transport :task m_transport started

28-Nov-18 11:01:38#R4L-60 :transport :enable tcp

28-Nov-18 11:01:38#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 11:01:38+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 11:01:38+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 11:01:38#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 11:01:38#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 11:01:55!R4L-60 :dispatch :Command not found: "ls"!

28-Nov-18 11:01:57!R4L-60 :dispatch :Command not found: "cd .."!

28-Nov-18 11:44:45#R4L-60 :msg_log :Message logger running

28-Nov-18 11:44:51+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_util

28-Nov-18 11:44:51#R4L-60 :util :task m_util started

28-Nov-18 11:44:51#R4L-60 :util :load setup setup.usf

28-Nov-18 11:44:51#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 11:44:51+R4L-60 :util :load setup finished (x0)

28-Nov-18 11:44:51#R4L-60 :util :set trig_mod

28-Nov-18 11:44:51#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 11:44:51+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 11:44:51#R4L-60 :util :enable irq

28-Nov-18 11:44:51+R4L-60 :util :enable irq finished (x0)

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_collector

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_transport

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_daq_rate

... 21082 more lines ...

|

|

177

|

Thu Nov 5 15:13:43 2020 |

Jan | Analysis | root script example | Attached is an example root script/macro that shows how to use scripts for analysis.

Usage:

1. change INPUT and OUTPUT preprocessor variables in e121_analysis.c pointing to your desired input and output root-files.

2. open root and type: root [1] .L e121_analysis.C++

root [2] run() 3. check plots popping up and output files

Hints:

in e121_analysis.C use #include "e121_raw.h" for the original channel names/mapping (e.g. ADC1_1,...)

and use#include "e121_mapped.h" for named channels (e.g. e_csi[0] or e_dssd_top) |

| Attachment 1: e121_analysis.C

|

#define e121_analysis_cxx

// INPUT FILES

#define INPUT1 "/data.local1/E121/root-files/part1/e121_run_0253.root"

//#define INPUT2 ""

//#define INPUT3 ""

//#define INPUT4 ""

//#define INPUT5 ""

//#define INPUT6 ""

//#define INPUT7 ""

//#define INPUT8 ""

//#define INPUT9 ""

//#define INPUT10 ""

//OUTPUT FILE

#define OUTPUT "run253.ana.root"

#include <TH2.h>

#include <TStyle.h>

#include <TCanvas.h>

#include <cmath>

#include <string>

#include <cstdlib>

#include <cstdio>

#include <ctime>

#include <fstream>

#include <iostream>

#include <stdint.h>

#include "TROOT.h"

#include "TAttText.h"

#include "TAxis.h"

#include "TCanvas.h"

#include "TChain.h"

#include "TCut.h"

#include "TF1.h"

#include "TFile.h"

#include "TGraph.h"

#include "TGraphAsymmErrors.h"

#include "TGraphErrors.h"

#include "TH1.h"

#include "THistPainter.h"

#include "TKey.h"

#include "TLatex.h"

#include "TLegend.h"

#include "TMath.h"

#include "TMatrixD.h"

#include "TMinuit.h"

#include "TMultiGraph.h"

#include "TNtuple.h"

#include "TPave.h"

#include "TPaveText.h"

#include "TPoint.h"

#include "TRandom.h"

#include "TRint.h"

#include "TString.h"

#include "TTree.h"

#include "TH1F.h"

#include "TH2F.h"

#include "TSystem.h"

#include "TProfile.h"

#include "TVirtualFitter.h"

#include "TLegend.h"

#include "TColor.h"

#include "TBranch.h"

#include "TList.h"

using namespace std;

void loop(TChain *fChain)

{

if (fChain == 0) return;

//#include "e121_raw.h" // use this for raw mapping of channels

#include "e121_mapped.h" // use this for mapped channel names

///////////////////////////

// histogram definitions //

///////////////////////////

// energy

TList *e_histo= new TList();

TH1D *h_e_pad_1[7];

TH1D *h_e_pad_2[7];

TH1D *h_e_pad_3[7];

TH1D *h_e_pad_4[7];

TH1D *h_e_pad_5[7];

TH1D *h_e_pad_6[7];

TH1D *h_e_pad_n[7];

TH1D *h_e_pad_n_lo[7];

TH1D *h_e_pad_n_hi[7];

char chnumber[300];

for (int i=0;i<7;i++)

{

sprintf(chnumber,"e_pad_1_strip_%d",i);

h_e_pad_1[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_1[i]);

sprintf(chnumber,"e_pad_2_strip_%d",i);

h_e_pad_2[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_2[i]);

sprintf(chnumber,"e_pad_3_strip_%d",i);

h_e_pad_3[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_3[i]);

sprintf(chnumber,"e_pad_4_strip_%d",i);

h_e_pad_4[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_4[i]);

sprintf(chnumber,"e_pad_5_strip_%d",i);

h_e_pad_5[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_5[i]);

sprintf(chnumber,"e_pad_6_strip_%d",i);

h_e_pad_6[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_6[i]);

sprintf(chnumber,"e_pad_%d_n-side",i);

h_e_pad_n[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n[i]);

sprintf(chnumber,"e_pad_%d_n-side_lo",i);

h_e_pad_n_lo[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n_lo[i]);

sprintf(chnumber,"e_pad_%d_n-side_hi",i);

h_e_pad_n_hi[i]=new TH1D(chnumber,chnumber,4096,0.5,4096.5);

e_histo->Add(h_e_pad_n_hi[i]);

}

TH1D *h_e_dssd_left=new TH1D("e_dssd_left","e_dssd_left",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_left);

TH1D *h_e_dssd_right=new TH1D("e_dssd_right","e_dssd_right",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_right);

TH1D *h_e_dssd_top=new TH1D("e_dssd_top","e_dssd_top",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_top);

TH1D *h_e_dssd_bottom=new TH1D("e_dssd_bottom","e_dssd_bottom",4096,0.5,4096.5);

e_histo->Add(h_e_dssd_bottom);

TH1D *h_e_csi[2];

h_e_csi[0]=new TH1D("e_csi_0","e_csi_0",4096,0.5,4096.5);

e_histo->Add(h_e_csi[0]);

h_e_csi[1]=new TH1D("e_csi_1","e_csi_1",4096,0.5,4096.5);

e_histo->Add(h_e_csi[1]);

// position

// time

// scaler

TList *sc_histo= new TList();

Int_t sc_bins = 500;

TGraph *g_sc_si=new TGraph();

g_sc_si->SetNameTitle("g_sc_si", "rate Si OR");

sc_histo->Add(g_sc_si);

TGraph *g_sc_mwpc=new TGraph();

g_sc_mwpc->SetNameTitle("g_sc_mwpc", "rate MWPC anode");

sc_histo->Add(g_sc_mwpc);

TGraph *g_sc_target=new TGraph();

g_sc_target->SetNameTitle("g_sc_target", "target density");

sc_histo->Add(g_sc_target);

TGraph *g_sc_trafo=new TGraph();

g_sc_trafo->SetNameTitle("g_sc_trafo", "ESR ion current");

sc_histo->Add(g_sc_trafo);

TGraph *g_sc_inhibit=new TGraph();

g_sc_inhibit->SetNameTitle("g_sc_inhibit", "target inhibit");

sc_histo->Add(g_sc_inhibit);

TGraph *g_sc_clock=new TGraph();

g_sc_clock->SetNameTitle("g_sc_clock", "1.5 MHz clock");

sc_histo->Add(g_sc_clock);

ULong64_t sc_si_sum = 0;

ULong64_t sc_mwpc_sum = 0;

ULong64_t sc_clock_sum = 0;

ULong64_t sc_target_sum = 0;

ULong64_t sc_trafo_sum = 0;

ULong64_t sc_inhibit_sum = 0;

Int_t sc_interval = 1; //interval time [sec] for scaler plotting

Double_t clock_ref = 1.5e6; // clock reference rate = 1.5 MHz

Double_t t_diff = 0;

Double_t t_elapsed = 0;

// get number of events to process

Long64_t nentries = fChain->GetEntries();

Long64_t nbytes = 0, nb = 0;

//////////////////////

// EVENT LOOP START //

//////////////////////

for (Long64_t i=0; i<nentries;i++)

// for (Long64_t i=0; i<10000;i++)

{

nb = fChain->GetEntry(i); nbytes += nb;

// event countdown

if ((float(i)/100000.)==int(i/100000)){cout << "event: " << i << " \tof " << nentries << endl;}

//////////////////////

//scaler processing //

//////////////////////

sc_si_sum += sc_silicon_or;

sc_mwpc_sum += sc_mwpc_anode;

sc_clock_sum += sc_clock;

sc_target_sum += sc_target;

sc_trafo_sum += sc_trafo;

sc_inhibit_sum += sc_inhibit;

t_elapsed += (double)(sc_clock/clock_ref);

t_diff = (double)(sc_clock_sum/clock_ref);

// fill the scaler sums to histo for very interval

if( !((int)t_diff % sc_interval) && (int)t_diff > 0 )

//if( true )

{

if ( (int)t_diff <= 2*sc_interval ) //exclude large time intervals >> crap data

{

// cout << "time: " << t_elapsed << " trafo:" << sc_trafo_sum;

// cout << " diff: " << t_diff << " modulo: " << ((int)t_diff % sc_interval) << endl;

g_sc_si->SetPoint(g_sc_si->GetN() ,t_elapsed, sc_si_sum);

g_sc_mwpc->SetPoint(g_sc_mwpc->GetN() ,t_elapsed, sc_mwpc_sum);

g_sc_target->SetPoint(g_sc_target->GetN() ,t_elapsed, sc_target_sum);

g_sc_trafo->SetPoint(g_sc_trafo->GetN() ,t_elapsed, sc_trafo_sum);

g_sc_inhibit->SetPoint(g_sc_inhibit->GetN(),t_elapsed, sc_inhibit_sum);

g_sc_clock->SetPoint(g_sc_clock->GetN() ,t_elapsed, sc_clock_sum);

}

sc_si_sum = 0;

sc_mwpc_sum = 0;

sc_clock_sum = 0;

sc_target_sum = 0;

sc_trafo_sum = 0;

sc_inhibit_sum = 0;

}

////////////////////

// energy spectra //

////////////////////

if(TRIGGER==1)

{

for (int i=0;i<7;i++)

{

h_e_pad_1[i]->Fill(e_pad_1[i]);

h_e_pad_2[i]->Fill(e_pad_2[i]);

h_e_pad_3[i]->Fill(e_pad_3[i]);

h_e_pad_4[i]->Fill(e_pad_4[i]);

h_e_pad_5[i]->Fill(e_pad_5[i]);

h_e_pad_6[i]->Fill(e_pad_6[i]);

if ( i > 0 )

{

h_e_pad_n[i]->Fill(e_pad_n[i]);

if ( t_elapsed >= 30 && t_elapsed <= 100 ) h_e_pad_n_hi[i]->Fill(e_pad_n[i]);

if ( t_elapsed >= 250 && t_elapsed <= 350 ) h_e_pad_n_lo[i]->Fill(e_pad_n[i]);

}

}

}

}

////////////////////

// EVENT LOOP END //

////////////////////

// write output file

TFile *outfile = TFile::Open(OUTPUT, "RECREATE");

e_histo->Write("energy", TObject::kSingleKey);

sc_histo->Write("scaler", TObject::kSingleKey);

outfile->Close();

cout << "\033[0;32m" << OUTPUT << " is created!\033[0m" << endl;

// direct plotting (optional)

TCanvas *c_test = new TCanvas("test","test", 1000, 1200);

c_test->Divide(1,5);

c_test->cd(1);

g_sc_si->SetFillColor(15);

g_sc_si->Draw("AB");

c_test->cd(2);

g_sc_mwpc->SetFillColor(15);

g_sc_mwpc->Draw("AB");

c_test->cd(3);

g_sc_target->SetFillColor(15);

g_sc_target->Draw("AB");

c_test->cd(4);

g_sc_trafo->SetFillColor(15);

g_sc_trafo->Draw("AB");

c_test->cd(5);

... 108 more lines ...

|

| Attachment 2: e121_mapped.h

|

//////////////////////////////////////////////////////////

// This class has been automatically generated on

// Wed Nov 4 09:54:00 2020 by ROOT version 6.18/04

// from TTree h101/CWNtuple

// found on file: /data.local1/E121/root-files/part1/e121_run_0252.root

//////////////////////////////////////////////////////////

// Declaration of leaf types

// DAQ

UInt_t TRIGGER; //

UInt_t EVENTNO; //

UInt_t TB_SI_IN;

UInt_t TB_SI_RED;

UInt_t TB_MWPC_IN;

UInt_t TB_MWPC_RED;

// ADCs

UInt_t e_pad_1[7];

UInt_t e_pad_2[7];

UInt_t e_pad_3[7];

UInt_t e_pad_4[7];

UInt_t e_pad_5[7];

UInt_t e_pad_6[7];

UInt_t e_pad_n[7];

UInt_t e_dssd_top, e_dssd_bottom, e_dssd_left, e_dssd_right;

UInt_t e_csi[2];

//TDCs

UInt_t t_mwpc_x1, t_mwpc_x2, t_mwpc_y1, t_mwpc_y2, t_mwpc_anode, t_mwpc_raw;

UInt_t t_master_trig, t_trig_1, t_trig_2;

//Scalers

UInt_t sc_master_trig;

UInt_t sc_silicon_or;

UInt_t sc_mwpc_raw;

UInt_t sc_u_cool;

UInt_t sc_i_cool;

UInt_t sc_trafo;

UInt_t sc_inhibit;

UInt_t sc_mwpc_anode;

UInt_t sc_mwpc_x1;

UInt_t sc_mwpc_x2;

UInt_t sc_mwpc_y1;

UInt_t sc_mwpc_y2;

UInt_t sc_clock;

UInt_t sc_target;

UInt_t sc_trig_1;

UInt_t sc_trig_2;

// Set branch addresses

fChain->SetBranchAddress("TRIGGER", &TRIGGER);

fChain->SetBranchAddress("EVENTNO", &EVENTNO);

fChain->SetBranchAddress("ADC1_1", &e_pad_1[0]);

fChain->SetBranchAddress("ADC1_2", &e_pad_1[1]);

fChain->SetBranchAddress("ADC1_3", &e_pad_1[2]);

fChain->SetBranchAddress("ADC1_4", &e_pad_1[3]);

fChain->SetBranchAddress("ADC1_5", &e_pad_1[4]);

fChain->SetBranchAddress("ADC1_6", &e_pad_1[5]);

fChain->SetBranchAddress("ADC1_7", &e_pad_1[6]);

//fChain->SetBranchAddress("ADC1_8", &);

fChain->SetBranchAddress("ADC1_9", &e_pad_2[0]);

fChain->SetBranchAddress("ADC1_10", &e_pad_2[1]);

fChain->SetBranchAddress("ADC1_11", &e_pad_2[2]);

fChain->SetBranchAddress("ADC1_12", &e_pad_2[3]);

fChain->SetBranchAddress("ADC1_13", &e_pad_2[4]);

fChain->SetBranchAddress("ADC1_14", &e_pad_2[5]);

fChain->SetBranchAddress("ADC1_15", &e_pad_2[6]);

// fChain->SetBranchAddress("ADC1_16", &);

fChain->SetBranchAddress("ADC1_17", &e_pad_3[0]);

fChain->SetBranchAddress("ADC1_18", &e_pad_3[1]);

fChain->SetBranchAddress("ADC1_19", &e_pad_3[2]);

fChain->SetBranchAddress("ADC1_20", &e_pad_3[3]);

fChain->SetBranchAddress("ADC1_21", &e_pad_3[4]);

fChain->SetBranchAddress("ADC1_22", &e_pad_3[5]);

fChain->SetBranchAddress("ADC1_23", &e_pad_3[6]);

// fChain->SetBranchAddress("ADC1_24", &);

fChain->SetBranchAddress("ADC1_25", &e_pad_4[0]);

fChain->SetBranchAddress("ADC1_26", &e_pad_4[1]);

fChain->SetBranchAddress("ADC1_27", &e_pad_4[2]);

fChain->SetBranchAddress("ADC1_28", &e_pad_4[3]);

fChain->SetBranchAddress("ADC1_29", &e_pad_4[4]);

fChain->SetBranchAddress("ADC1_30", &e_pad_4[5]);

fChain->SetBranchAddress("ADC1_31", &e_pad_4[6]);

// fChain->SetBranchAddress("ADC1_32", &);

fChain->SetBranchAddress("ADC2_1", &e_pad_5[0]);

fChain->SetBranchAddress("ADC2_2", &e_pad_5[1]);

fChain->SetBranchAddress("ADC2_3", &e_pad_5[2]);

fChain->SetBranchAddress("ADC2_4", &e_pad_5[3]);

fChain->SetBranchAddress("ADC2_5", &e_pad_5[4]);

fChain->SetBranchAddress("ADC2_6", &e_pad_5[5]);

fChain->SetBranchAddress("ADC2_7", &e_pad_5[6]);

// fChain->SetBranchAddress("ADC2_8", &);

// fChain->SetBranchAddress("ADC2_9", &);

// fChain->SetBranchAddress("ADC2_10", &);

// fChain->SetBranchAddress("ADC2_11", &);

// fChain->SetBranchAddress("ADC2_12", &);

// fChain->SetBranchAddress("ADC2_13", &);

// fChain->SetBranchAddress("ADC2_14", &);

// fChain->SetBranchAddress("ADC2_15", &);

// fChain->SetBranchAddress("ADC2_16", &);

fChain->SetBranchAddress("ADC2_17", &e_pad_6[0]);

fChain->SetBranchAddress("ADC2_18", &e_pad_6[1]);

fChain->SetBranchAddress("ADC2_19", &e_pad_6[2]);

fChain->SetBranchAddress("ADC2_20", &e_pad_6[3]);

fChain->SetBranchAddress("ADC2_21", &e_pad_6[4]);

fChain->SetBranchAddress("ADC2_22", &e_pad_6[5]);

fChain->SetBranchAddress("ADC2_23", &e_pad_6[6]);

// fChain->SetBranchAddress("ADC2_24", &);

// fChain->SetBranchAddress("ADC2_25", &);

// fChain->SetBranchAddress("ADC2_26", &);

// fChain->SetBranchAddress("ADC2_27", &);

// fChain->SetBranchAddress("ADC2_28", &);

// fChain->SetBranchAddress("ADC2_29", &);

// fChain->SetBranchAddress("ADC2_30", &);

// fChain->SetBranchAddress("ADC2_31", &);

// fChain->SetBranchAddress("ADC2_32", &);

fChain->SetBranchAddress("ADC3_1", &e_dssd_left);

fChain->SetBranchAddress("ADC3_2", &e_dssd_right);

fChain->SetBranchAddress("ADC3_3", &e_dssd_top);

fChain->SetBranchAddress("ADC3_4", &e_dssd_bottom);

// fChain->SetBranchAddress("ADC3_5", &);

// fChain->SetBranchAddress("ADC3_6", &);

fChain->SetBranchAddress("ADC3_7", &e_csi[0]);

fChain->SetBranchAddress("ADC3_8", &e_csi[1]);

// fChain->SetBranchAddress("ADC3_9", &);

// fChain->SetBranchAddress("ADC3_10", &);

fChain->SetBranchAddress("ADC3_11", &e_pad_n[1]);

fChain->SetBranchAddress("ADC3_12", &e_pad_n[2]);

fChain->SetBranchAddress("ADC3_13", &e_pad_n[3]);

fChain->SetBranchAddress("ADC3_14", &e_pad_n[4]);

fChain->SetBranchAddress("ADC3_15", &e_pad_n[5]);

fChain->SetBranchAddress("ADC3_16", &e_pad_n[6]);

// fChain->SetBranchAddress("ADC3_17", &);

// fChain->SetBranchAddress("ADC3_18", &);

// fChain->SetBranchAddress("ADC3_19", &);

// fChain->SetBranchAddress("ADC3_20", &);

// fChain->SetBranchAddress("ADC3_21", &);

// fChain->SetBranchAddress("ADC3_22", &);

// fChain->SetBranchAddress("ADC3_23", &);

// fChain->SetBranchAddress("ADC3_24", &);

// fChain->SetBranchAddress("ADC3_25", &);

// fChain->SetBranchAddress("ADC3_26", &);

// fChain->SetBranchAddress("ADC3_27", &);

// fChain->SetBranchAddress("ADC3_28", &);

// fChain->SetBranchAddress("ADC3_29", &);

// fChain->SetBranchAddress("ADC3_30", &);

// fChain->SetBranchAddress("ADC3_31", &);

// fChain->SetBranchAddress("ADC3_32", &);

fChain->SetBranchAddress("SC1", &sc_master_trig);

fChain->SetBranchAddress("SC2", &sc_silicon_or);

fChain->SetBranchAddress("SC3", &sc_mwpc_raw);

fChain->SetBranchAddress("SC4", &sc_u_cool);

fChain->SetBranchAddress("SC5", &sc_i_cool);

fChain->SetBranchAddress("SC6", &sc_trafo);

fChain->SetBranchAddress("SC7", &sc_inhibit);

fChain->SetBranchAddress("SC8", &sc_mwpc_anode);

fChain->SetBranchAddress("SC9", &sc_mwpc_x1);

fChain->SetBranchAddress("SC10", &sc_mwpc_x2);

fChain->SetBranchAddress("SC11", &sc_mwpc_y1);

fChain->SetBranchAddress("SC12", &sc_mwpc_y2);

fChain->SetBranchAddress("SC13", &sc_clock);

fChain->SetBranchAddress("SC14", &sc_target);

fChain->SetBranchAddress("SC15", &sc_trig_1);

fChain->SetBranchAddress("SC16", &sc_trig_2);

// fChain->SetBranchAddress("SC17", &);

// fChain->SetBranchAddress("SC18", &);

// fChain->SetBranchAddress("SC19", &);

// fChain->SetBranchAddress("SC20", &);

// fChain->SetBranchAddress("SC21", &);

// fChain->SetBranchAddress("SC22", &);

// fChain->SetBranchAddress("SC23", &);

// fChain->SetBranchAddress("SC24", &);

// fChain->SetBranchAddress("SC25", &);

// fChain->SetBranchAddress("SC26", &);

// fChain->SetBranchAddress("SC27", &);

// fChain->SetBranchAddress("SC28", &);

// fChain->SetBranchAddress("SC29", &);

// fChain->SetBranchAddress("SC30", &);

// fChain->SetBranchAddress("SC31", &);

// fChain->SetBranchAddress("SC32", &);

fChain->SetBranchAddress("TDC1", &t_mwpc_anode);

fChain->SetBranchAddress("TDC2", &t_mwpc_x1);

fChain->SetBranchAddress("TDC3", &t_mwpc_x2);

fChain->SetBranchAddress("TDC4", &t_mwpc_y1);

fChain->SetBranchAddress("TDC5", &t_mwpc_y2);

fChain->SetBranchAddress("TDC6", &t_mwpc_raw);

// fChain->SetBranchAddress("TDC7", &t_);

fChain->SetBranchAddress("TDC8", &t_master_trig);

fChain->SetBranchAddress("TDC9", &t_trig_1);

fChain->SetBranchAddress("TDC10", &t_trig_2);

fChain->SetBranchAddress("TB_SI_IN", &TB_SI_IN);

fChain->SetBranchAddress("TB_SI_RED", &TB_SI_RED);

fChain->SetBranchAddress("TB_MWPC_IN", &TB_MWPC_IN);

fChain->SetBranchAddress("TB_MWPC_RED", &TB_MWPC_RED);

|

| Attachment 3: e121_raw.h

|

//////////////////////////////////////////////////////////

// This class has been automatically generated on

// Wed Nov 4 09:54:00 2020 by ROOT version 6.18/04

// from TTree h101/CWNtuple

// found on file: /data.local1/E121/root-files/part1/e121_run_0252.root

//////////////////////////////////////////////////////////

// Declaration of leaf types

UInt_t TRIGGER; //

UInt_t EVENTNO; //

UInt_t ADC1_1;

UInt_t ADC1_2;

UInt_t ADC1_3;

UInt_t ADC1_4;

UInt_t ADC1_5;

UInt_t ADC1_6;

UInt_t ADC1_7;

UInt_t ADC1_8;

UInt_t ADC1_9;

UInt_t ADC1_10;

UInt_t ADC1_11;

UInt_t ADC1_12;

UInt_t ADC1_13;

UInt_t ADC1_14;

UInt_t ADC1_15;

UInt_t ADC1_16;

UInt_t ADC1_17;

UInt_t ADC1_18;

UInt_t ADC1_19;

UInt_t ADC1_20;

UInt_t ADC1_21;

UInt_t ADC1_22;

UInt_t ADC1_23;

UInt_t ADC1_24;

UInt_t ADC1_25;

UInt_t ADC1_26;

UInt_t ADC1_27;

UInt_t ADC1_28;

UInt_t ADC1_29;

UInt_t ADC1_30;

UInt_t ADC1_31;

UInt_t ADC1_32;

UInt_t ADC2_1;

UInt_t ADC2_2;

UInt_t ADC2_3;

UInt_t ADC2_4;

UInt_t ADC2_5;

UInt_t ADC2_6;

UInt_t ADC2_7;

UInt_t ADC2_8;

UInt_t ADC2_9;

UInt_t ADC2_10;

UInt_t ADC2_11;

UInt_t ADC2_12;

UInt_t ADC2_13;

UInt_t ADC2_14;

UInt_t ADC2_15;

UInt_t ADC2_16;

UInt_t ADC2_17;

UInt_t ADC2_18;

UInt_t ADC2_19;

UInt_t ADC2_20;

UInt_t ADC2_21;

UInt_t ADC2_22;

UInt_t ADC2_23;

UInt_t ADC2_24;

UInt_t ADC2_25;

UInt_t ADC2_26;

UInt_t ADC2_27;

UInt_t ADC2_28;

UInt_t ADC2_29;

UInt_t ADC2_30;

UInt_t ADC2_31;

UInt_t ADC2_32;

UInt_t ADC3_1;

UInt_t ADC3_2;

UInt_t ADC3_3;

UInt_t ADC3_4;

UInt_t ADC3_5;

UInt_t ADC3_6;

UInt_t ADC3_7;

UInt_t ADC3_8;

UInt_t ADC3_9;

UInt_t ADC3_10;

UInt_t ADC3_11;

UInt_t ADC3_12;

UInt_t ADC3_13;

UInt_t ADC3_14;

UInt_t ADC3_15;

UInt_t ADC3_16;

UInt_t ADC3_17;

UInt_t ADC3_18;

UInt_t ADC3_19;

UInt_t ADC3_20;

UInt_t ADC3_21;

UInt_t ADC3_22;

UInt_t ADC3_23;

UInt_t ADC3_24;

UInt_t ADC3_25;

UInt_t ADC3_26;

UInt_t ADC3_27;

UInt_t ADC3_28;

UInt_t ADC3_29;

UInt_t ADC3_30;

UInt_t ADC3_31;

UInt_t ADC3_32;

UInt_t SC1;

UInt_t SC2;

UInt_t SC3;

UInt_t SC4;

UInt_t SC5;

UInt_t SC6;

UInt_t SC7;

UInt_t SC8;

UInt_t SC9;

UInt_t SC10;

UInt_t SC11;

UInt_t SC12;

UInt_t SC13;

UInt_t SC14;

UInt_t SC15;

UInt_t SC16;

UInt_t SC17;

UInt_t SC18;

UInt_t SC19;

UInt_t SC20;

UInt_t SC21;

UInt_t SC22;

UInt_t SC23;

UInt_t SC24;

UInt_t SC25;

UInt_t SC26;

UInt_t SC27;

UInt_t SC28;

UInt_t SC29;

UInt_t SC30;

UInt_t SC31;

UInt_t SC32;

UInt_t TDC1;

UInt_t TDC2;

UInt_t TDC3;

UInt_t TDC4;

UInt_t TDC5;

UInt_t TDC6;

UInt_t TDC7;

UInt_t TDC8;

UInt_t TDC9;

UInt_t TDC10;

UInt_t TB_SI_IN;

UInt_t TB_SI_RED;

UInt_t TB_MWPC_IN;

UInt_t TB_MWPC_RED;

// Set branch addresses

fChain->SetBranchAddress("TRIGGER", &TRIGGER );

fChain->SetBranchAddress("EVENTNO", &EVENTNO );

fChain->SetBranchAddress("ADC1_1", &ADC1_1 );

fChain->SetBranchAddress("ADC1_2", &ADC1_2 );

fChain->SetBranchAddress("ADC1_3", &ADC1_3 );

fChain->SetBranchAddress("ADC1_4", &ADC1_4 );

fChain->SetBranchAddress("ADC1_5", &ADC1_5 );

fChain->SetBranchAddress("ADC1_6", &ADC1_6 );

fChain->SetBranchAddress("ADC1_7", &ADC1_7 );

fChain->SetBranchAddress("ADC1_8", &ADC1_8 );

fChain->SetBranchAddress("ADC1_9", &ADC1_9 );

fChain->SetBranchAddress("ADC1_10", &ADC1_10 );

fChain->SetBranchAddress("ADC1_11", &ADC1_11 );

fChain->SetBranchAddress("ADC1_12", &ADC1_12 );

fChain->SetBranchAddress("ADC1_13", &ADC1_13 );

fChain->SetBranchAddress("ADC1_14", &ADC1_14 );

fChain->SetBranchAddress("ADC1_15", &ADC1_15 );

fChain->SetBranchAddress("ADC1_16", &ADC1_16 );

fChain->SetBranchAddress("ADC1_17", &ADC1_17 );

fChain->SetBranchAddress("ADC1_18", &ADC1_18 );

fChain->SetBranchAddress("ADC1_19", &ADC1_19 );

fChain->SetBranchAddress("ADC1_20", &ADC1_20 );

fChain->SetBranchAddress("ADC1_21", &ADC1_21 );

fChain->SetBranchAddress("ADC1_22", &ADC1_22 );

fChain->SetBranchAddress("ADC1_23", &ADC1_23 );

fChain->SetBranchAddress("ADC1_24", &ADC1_24 );

fChain->SetBranchAddress("ADC1_25", &ADC1_25 );

fChain->SetBranchAddress("ADC1_26", &ADC1_26 );

fChain->SetBranchAddress("ADC1_27", &ADC1_27 );

fChain->SetBranchAddress("ADC1_28", &ADC1_28 );

fChain->SetBranchAddress("ADC1_29", &ADC1_29 );

fChain->SetBranchAddress("ADC1_30", &ADC1_30 );

fChain->SetBranchAddress("ADC1_31", &ADC1_31 );

fChain->SetBranchAddress("ADC1_32", &ADC1_32 );

fChain->SetBranchAddress("ADC2_1", &ADC2_1 );

fChain->SetBranchAddress("ADC2_2", &ADC2_2 );

fChain->SetBranchAddress("ADC2_3", &ADC2_3 );

fChain->SetBranchAddress("ADC2_4", &ADC2_4 );

fChain->SetBranchAddress("ADC2_5", &ADC2_5 );

fChain->SetBranchAddress("ADC2_6", &ADC2_6 );

fChain->SetBranchAddress("ADC2_7", &ADC2_7 );

fChain->SetBranchAddress("ADC2_8", &ADC2_8 );

fChain->SetBranchAddress("ADC2_9", &ADC2_9 );

fChain->SetBranchAddress("ADC2_10", &ADC2_10 );

fChain->SetBranchAddress("ADC2_11", &ADC2_11 );

fChain->SetBranchAddress("ADC2_12", &ADC2_12 );

fChain->SetBranchAddress("ADC2_13", &ADC2_13 );

fChain->SetBranchAddress("ADC2_14", &ADC2_14 );

fChain->SetBranchAddress("ADC2_15", &ADC2_15 );

fChain->SetBranchAddress("ADC2_16", &ADC2_16 );

fChain->SetBranchAddress("ADC2_17", &ADC2_17 );

fChain->SetBranchAddress("ADC2_18", &ADC2_18 );

fChain->SetBranchAddress("ADC2_19", &ADC2_19 );

fChain->SetBranchAddress("ADC2_20", &ADC2_20 );

fChain->SetBranchAddress("ADC2_21", &ADC2_21 );

fChain->SetBranchAddress("ADC2_22", &ADC2_22 );

fChain->SetBranchAddress("ADC2_23", &ADC2_23 );

fChain->SetBranchAddress("ADC2_24", &ADC2_24 );

fChain->SetBranchAddress("ADC2_25", &ADC2_25 );

fChain->SetBranchAddress("ADC2_26", &ADC2_26 );

fChain->SetBranchAddress("ADC2_27", &ADC2_27 );

fChain->SetBranchAddress("ADC2_28", &ADC2_28 );

fChain->SetBranchAddress("ADC2_29", &ADC2_29 );

fChain->SetBranchAddress("ADC2_30", &ADC2_30 );

fChain->SetBranchAddress("ADC2_31", &ADC2_31 );

fChain->SetBranchAddress("ADC2_32", &ADC2_32 );

fChain->SetBranchAddress("ADC3_1", &ADC3_1 );

fChain->SetBranchAddress("ADC3_2", &ADC3_2 );

fChain->SetBranchAddress("ADC3_3", &ADC3_3 );

fChain->SetBranchAddress("ADC3_4", &ADC3_4 );

fChain->SetBranchAddress("ADC3_5", &ADC3_5 );

fChain->SetBranchAddress("ADC3_6", &ADC3_6 );

fChain->SetBranchAddress("ADC3_7", &ADC3_7 );

fChain->SetBranchAddress("ADC3_8", &ADC3_8 );

fChain->SetBranchAddress("ADC3_9", &ADC3_9 );

fChain->SetBranchAddress("ADC3_10", &ADC3_10 );

fChain->SetBranchAddress("ADC3_11", &ADC3_11 );

fChain->SetBranchAddress("ADC3_12", &ADC3_12 );

fChain->SetBranchAddress("ADC3_13", &ADC3_13 );

fChain->SetBranchAddress("ADC3_14", &ADC3_14 );

fChain->SetBranchAddress("ADC3_15", &ADC3_15 );

fChain->SetBranchAddress("ADC3_16", &ADC3_16 );

fChain->SetBranchAddress("ADC3_17", &ADC3_17 );

fChain->SetBranchAddress("ADC3_18", &ADC3_18 );

fChain->SetBranchAddress("ADC3_19", &ADC3_19 );

fChain->SetBranchAddress("ADC3_20", &ADC3_20 );

fChain->SetBranchAddress("ADC3_21", &ADC3_21 );

fChain->SetBranchAddress("ADC3_22", &ADC3_22 );

fChain->SetBranchAddress("ADC3_23", &ADC3_23 );

fChain->SetBranchAddress("ADC3_24", &ADC3_24 );

fChain->SetBranchAddress("ADC3_25", &ADC3_25 );

fChain->SetBranchAddress("ADC3_26", &ADC3_26 );

fChain->SetBranchAddress("ADC3_27", &ADC3_27 );

fChain->SetBranchAddress("ADC3_28", &ADC3_28 );

fChain->SetBranchAddress("ADC3_29", &ADC3_29 );

fChain->SetBranchAddress("ADC3_30", &ADC3_30 );

fChain->SetBranchAddress("ADC3_31", &ADC3_31 );

fChain->SetBranchAddress("ADC3_32", &ADC3_32 );

fChain->SetBranchAddress("SC1", &SC1 );

fChain->SetBranchAddress("SC2", &SC2 );

fChain->SetBranchAddress("SC3", &SC3 );

fChain->SetBranchAddress("SC4", &SC4 );

fChain->SetBranchAddress("SC5", &SC5 );

fChain->SetBranchAddress("SC6", &SC6 );

fChain->SetBranchAddress("SC7", &SC7 );

fChain->SetBranchAddress("SC8", &SC8 );

fChain->SetBranchAddress("SC9", &SC9 );

fChain->SetBranchAddress("SC10", &SC10 );

fChain->SetBranchAddress("SC11", &SC11 );

fChain->SetBranchAddress("SC12", &SC12 );

fChain->SetBranchAddress("SC13", &SC13 );

fChain->SetBranchAddress("SC14", &SC14 );

fChain->SetBranchAddress("SC15", &SC15 );

fChain->SetBranchAddress("SC16", &SC16 );

fChain->SetBranchAddress("SC17", &SC17 );

fChain->SetBranchAddress("SC18", &SC18 );

fChain->SetBranchAddress("SC19", &SC19 );

fChain->SetBranchAddress("SC20", &SC20 );

fChain->SetBranchAddress("SC21", &SC21 );

fChain->SetBranchAddress("SC22", &SC22 );

fChain->SetBranchAddress("SC23", &SC23 );

fChain->SetBranchAddress("SC24", &SC24 );

fChain->SetBranchAddress("SC25", &SC25 );

fChain->SetBranchAddress("SC26", &SC26 );

fChain->SetBranchAddress("SC27", &SC27 );

fChain->SetBranchAddress("SC28", &SC28 );

fChain->SetBranchAddress("SC29", &SC29 );

fChain->SetBranchAddress("SC30", &SC30 );

fChain->SetBranchAddress("SC31", &SC31 );

fChain->SetBranchAddress("SC32", &SC32 );

fChain->SetBranchAddress("TDC1", &TDC1 );

fChain->SetBranchAddress("TDC2", &TDC2 );

fChain->SetBranchAddress("TDC3", &TDC3 );

fChain->SetBranchAddress("TDC4", &TDC4 );

fChain->SetBranchAddress("TDC5", &TDC5 );

fChain->SetBranchAddress("TDC6", &TDC6 );

fChain->SetBranchAddress("TDC7", &TDC7 );

fChain->SetBranchAddress("TDC8", &TDC8 );

fChain->SetBranchAddress("TDC9", &TDC9 );

fChain->SetBranchAddress("TDC10", &TDC10 );

fChain->SetBranchAddress("TB_SI_IN", &TB_SI_IN);

fChain->SetBranchAddress("TB_SI_RED", &TB_SI_RED);

fChain->SetBranchAddress("TB_MWPC_IN", &TB_MWPC_IN);

fChain->SetBranchAddress("TB_MWPC_RED", &TB_MWPC_RED);

|

|

178

|

Thu Nov 19 09:14:40 2020 |

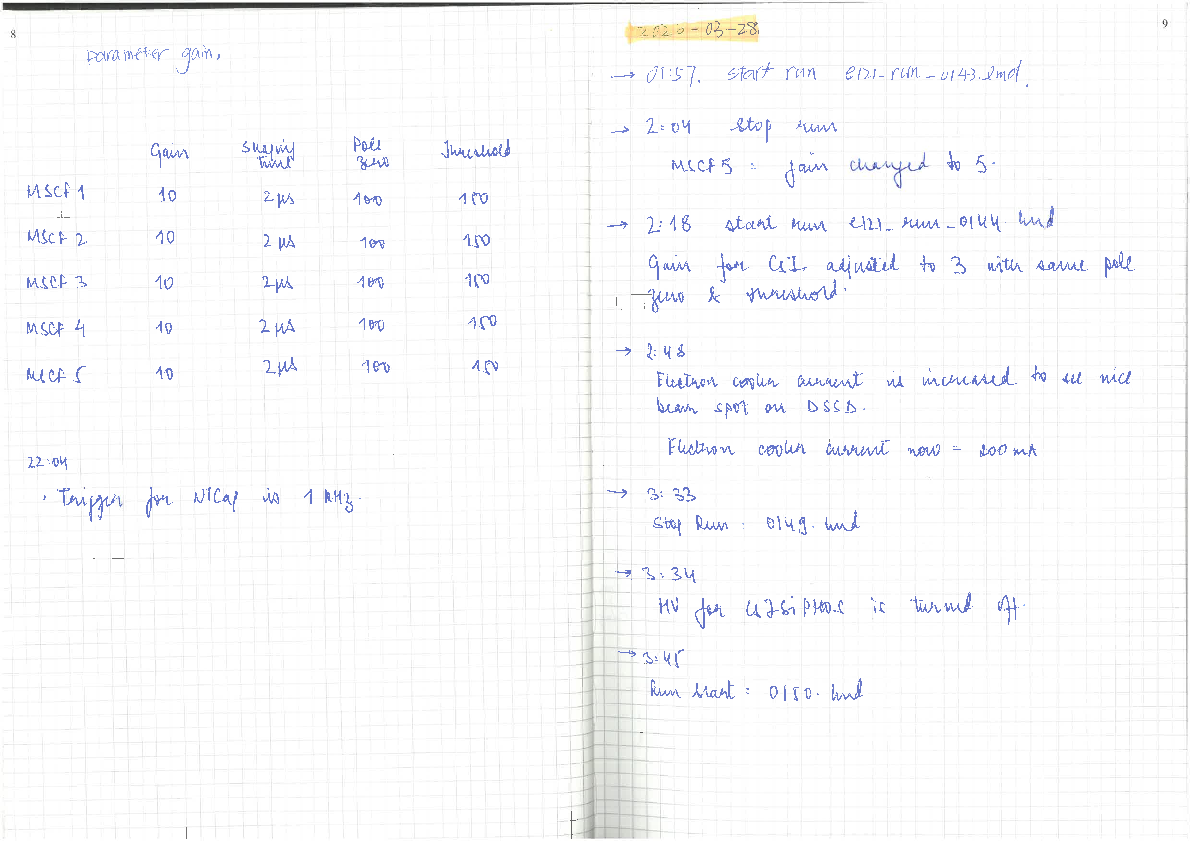

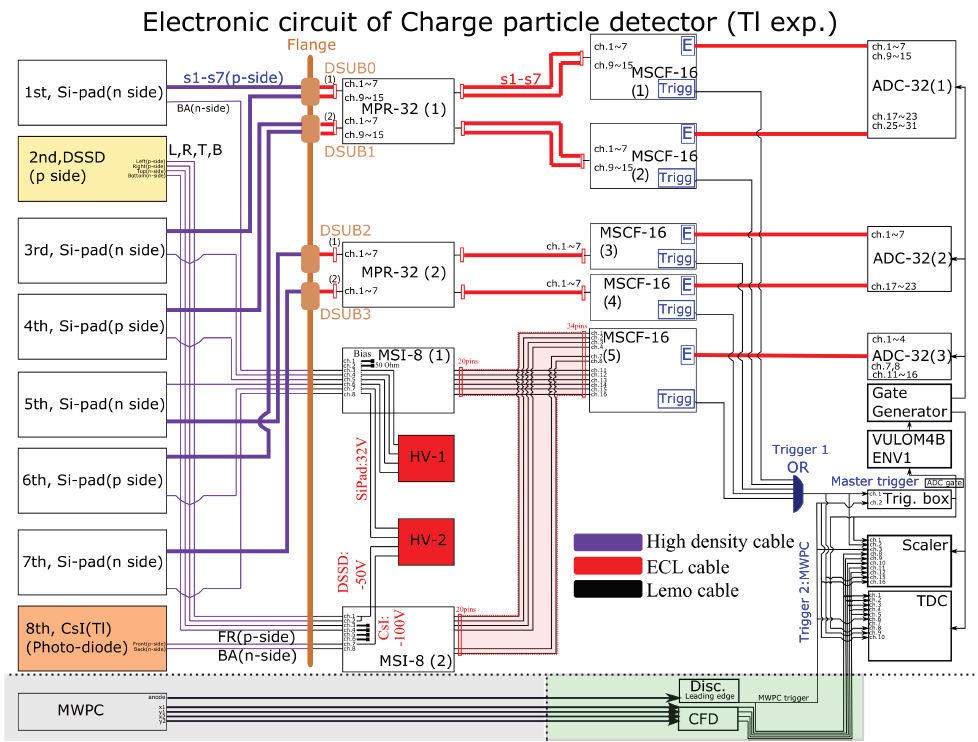

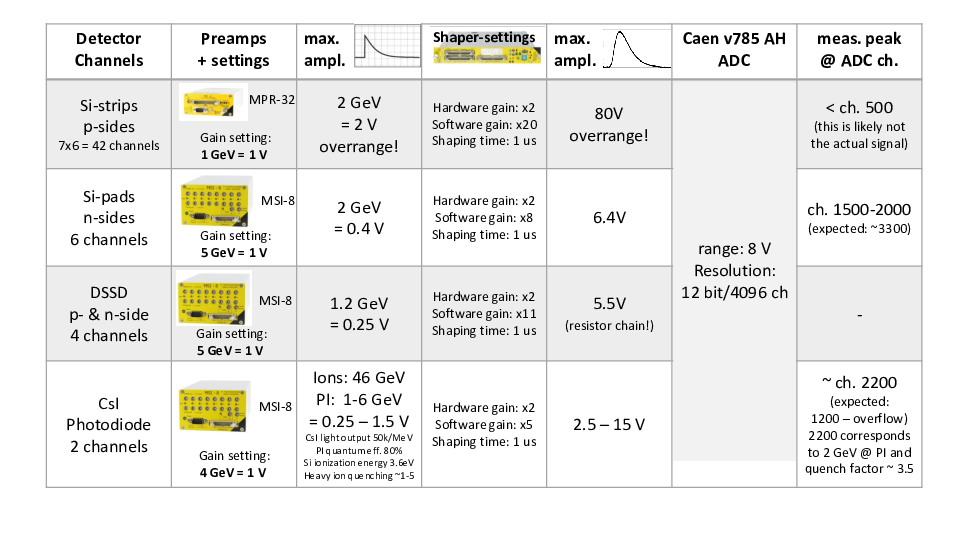

Jan | Detectors | remote MSCF settings for CsISiPHOS | Attached is a list of all set values for the 5 MSCF shaper modules.

This was done prior to run0251, which served as a final benchmark for those settings.

See: https://elog.gsi.de/esr/E121/62

And https://elog.gsi.de/esr/E121/104

The det. to MSCF assignment is the following:

MSCF 1: Si-pad 1 + 2 p-side/strips (ch. 1-7 + ch. 9-15)

MSCF 2: Si-pad 3 + 4 p-side/strips (ch. 1-7 + ch. 9-15)

MSCF 3: Si-pad 5 p-side/strips (ch. 1-7)

MSCF 4: Si-pad 6 p-side/strips (ch. 1-7)

MSCF 5: DSSD (ch. 1 - 4); CsI (ch. 7 & 8); Si-pad n-sides (ch. 11 - 16)

Note that only the pre-amplification stage of the MSI-8 amplifiers were used for all channels. |

| Attachment 1: setting.1585477986

|

1585477986

Sun Mar 29 12:33:06 CEST 2020

ringpi:mrcc:mscf1:getGainCommon 15

ringpi:mrcc:mscf1:getShapingTimeCommon 2

ringpi:mrcc:mscf1:getThresholdCommon 244

ringpi:mrcc:mscf1:getPzCommon 100

ringpi:mrcc:mscf2:getGainCommon 15

ringpi:mrcc:mscf2:getShapingTimeCommon 2

ringpi:mrcc:mscf2:getThresholdCommon 244

ringpi:mrcc:mscf2:getPzCommon 100

ringpi:mrcc:mscf3:getGainCommon 15

ringpi:mrcc:mscf3:getShapingTimeCommon 2

ringpi:mrcc:mscf3:getThresholdCommon 244

ringpi:mrcc:mscf3:getPzCommon 100

ringpi:mrcc:mscf4:getGainCommon 15

ringpi:mrcc:mscf4:getShapingTimeCommon 2

ringpi:mrcc:mscf4:getThresholdCommon 244

ringpi:mrcc:mscf4:getPzCommon 100

ringpi:mrcc:mscf5:getGainCommon 5

ringpi:mrcc:mscf5:getShapingTimeCommon 2

ringpi:mrcc:mscf5:getThresholdCommon 150

ringpi:mrcc:mscf5:getPzCommon 100

ringpi:mrcc:mscf1:getGain1 15

ringpi:mrcc:mscf1:getGain2 15

ringpi:mrcc:mscf1:getGain3 15

ringpi:mrcc:mscf1:getGain4 15

ringpi:mrcc:mscf1:getShapingTime1 2

ringpi:mrcc:mscf1:getShapingTime2 2

ringpi:mrcc:mscf1:getShapingTime3 2

ringpi:mrcc:mscf1:getShapingTime4 2

ringpi:mrcc:mscf2:getGain1 15

ringpi:mrcc:mscf2:getGain2 15

ringpi:mrcc:mscf2:getGain3 15

ringpi:mrcc:mscf2:getGain4 15