| ID |

Date |

Author |

Category |

Subject |

|

101

|

Mon Mar 30 16:25:05 2020 |

ruijiu | Detectors | turn down the HV | turn down the hv and pull out the detector.

suggest by

Hi everybody,

is there now much more rate on the detectors?

Perhaps it helps to turn down the bias for a while and to take the detectors out of the beam, by pulling the pocket out?

And then see if the leakage current comes down again.

good luck, Thomas

***********************************************

Dr. Thomas Faestermann | Tel: +49-89-2723868

Physik Department E12 |

Techn. Univ. Muenchen | Mob: +49-1626193388 |

|

103

|

Mon Mar 30 20:51:06 2020 |

Ragan | Detectors | Bias Voltage for Si-pads | The limit of the leakage current for all Si pads was increased from 1500 nA to 5000nA and

leakage current was recorded for different Bias Voltages (32V, 35V, 40V, 45V, 50V, 55V

and 60V).

Since, I_leakage remains < 3 uA for 60 V, it is decided to increase the Bias Voltage for

all the Si-pads from 32 V to 60 V.

For DSSD and CsI, bias voltages remains same (-50V and -160V respectively). |

| Attachment 1: Si_pad_bias-voltage.ods

|

|

111

|

Wed Apr 1 01:02:24 2020 |

ruijiu | Detectors | the detector cable is disconnected. | |

|

112

|

Wed Apr 1 01:05:36 2020 |

ruijiu | Detectors | detector position fixed at 60 mm | The detector cable was disconnected . We entered and reconnected the cable. |

| Attachment 1: VID_20200401_010416.mp4

|

|

178

|

Thu Nov 19 09:14:40 2020 |

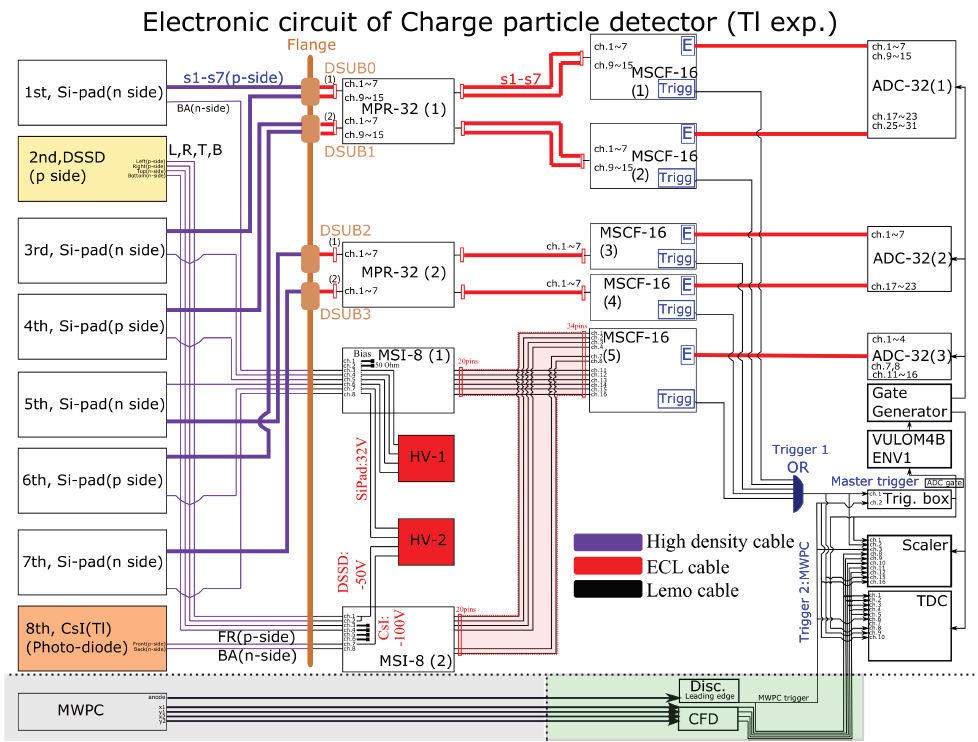

Jan | Detectors | remote MSCF settings for CsISiPHOS | Attached is a list of all set values for the 5 MSCF shaper modules.

This was done prior to run0251, which served as a final benchmark for those settings.

See: https://elog.gsi.de/esr/E121/62

And https://elog.gsi.de/esr/E121/104

The det. to MSCF assignment is the following:

MSCF 1: Si-pad 1 + 2 p-side/strips (ch. 1-7 + ch. 9-15)

MSCF 2: Si-pad 3 + 4 p-side/strips (ch. 1-7 + ch. 9-15)

MSCF 3: Si-pad 5 p-side/strips (ch. 1-7)

MSCF 4: Si-pad 6 p-side/strips (ch. 1-7)

MSCF 5: DSSD (ch. 1 - 4); CsI (ch. 7 & 8); Si-pad n-sides (ch. 11 - 16)

Note that only the pre-amplification stage of the MSI-8 amplifiers were used for all channels. |

| Attachment 1: setting.1585477986

|

1585477986

Sun Mar 29 12:33:06 CEST 2020

ringpi:mrcc:mscf1:getGainCommon 15

ringpi:mrcc:mscf1:getShapingTimeCommon 2

ringpi:mrcc:mscf1:getThresholdCommon 244

ringpi:mrcc:mscf1:getPzCommon 100

ringpi:mrcc:mscf2:getGainCommon 15

ringpi:mrcc:mscf2:getShapingTimeCommon 2

ringpi:mrcc:mscf2:getThresholdCommon 244

ringpi:mrcc:mscf2:getPzCommon 100

ringpi:mrcc:mscf3:getGainCommon 15

ringpi:mrcc:mscf3:getShapingTimeCommon 2

ringpi:mrcc:mscf3:getThresholdCommon 244

ringpi:mrcc:mscf3:getPzCommon 100

ringpi:mrcc:mscf4:getGainCommon 15

ringpi:mrcc:mscf4:getShapingTimeCommon 2

ringpi:mrcc:mscf4:getThresholdCommon 244

ringpi:mrcc:mscf4:getPzCommon 100

ringpi:mrcc:mscf5:getGainCommon 5

ringpi:mrcc:mscf5:getShapingTimeCommon 2

ringpi:mrcc:mscf5:getThresholdCommon 150

ringpi:mrcc:mscf5:getPzCommon 100

ringpi:mrcc:mscf1:getGain1 15

ringpi:mrcc:mscf1:getGain2 15

ringpi:mrcc:mscf1:getGain3 15

ringpi:mrcc:mscf1:getGain4 15

ringpi:mrcc:mscf1:getShapingTime1 2

ringpi:mrcc:mscf1:getShapingTime2 2

ringpi:mrcc:mscf1:getShapingTime3 2

ringpi:mrcc:mscf1:getShapingTime4 2

ringpi:mrcc:mscf2:getGain1 15

ringpi:mrcc:mscf2:getGain2 15

ringpi:mrcc:mscf2:getGain3 15

ringpi:mrcc:mscf2:getGain4 15

ringpi:mrcc:mscf2:getShapingTime1 2

ringpi:mrcc:mscf2:getShapingTime2 2

ringpi:mrcc:mscf2:getShapingTime3 2

ringpi:mrcc:mscf2:getShapingTime4 2

ringpi:mrcc:mscf3:getGain1 15

ringpi:mrcc:mscf3:getGain2 15

ringpi:mrcc:mscf3:getGain3 15

ringpi:mrcc:mscf3:getGain4 15

ringpi:mrcc:mscf3:getShapingTime1 2

ringpi:mrcc:mscf3:getShapingTime2 2

ringpi:mrcc:mscf3:getShapingTime3 2

ringpi:mrcc:mscf3:getShapingTime4 2

ringpi:mrcc:mscf4:getGain1 15

ringpi:mrcc:mscf4:getGain2 15

ringpi:mrcc:mscf4:getGain3 0

ringpi:mrcc:mscf4:getGain4 0

ringpi:mrcc:mscf4:getShapingTime1 2

ringpi:mrcc:mscf4:getShapingTime2 2

ringpi:mrcc:mscf4:getShapingTime3 2

ringpi:mrcc:mscf4:getShapingTime4 2

ringpi:mrcc:mscf5:getGain1 8

ringpi:mrcc:mscf5:getGain2 3

ringpi:mrcc:mscf5:getGain3 6

ringpi:mrcc:mscf5:getGain4 6

ringpi:mrcc:mscf5:getShapingTime1 2

ringpi:mrcc:mscf5:getShapingTime2 2

ringpi:mrcc:mscf5:getShapingTime3 2

ringpi:mrcc:mscf5:getShapingTime4 2

ringpi:mrcc:mscf1:getThreshold1 20

ringpi:mrcc:mscf1:getThreshold2 20

ringpi:mrcc:mscf1:getThreshold3 20

ringpi:mrcc:mscf1:getThreshold4 20

ringpi:mrcc:mscf1:getThreshold5 20

ringpi:mrcc:mscf1:getThreshold6 20

ringpi:mrcc:mscf1:getThreshold7 0

ringpi:mrcc:mscf1:getThreshold8 0

ringpi:mrcc:mscf1:getThreshold9 20

ringpi:mrcc:mscf1:getThreshold10 20

ringpi:mrcc:mscf1:getThreshold11 20

ringpi:mrcc:mscf1:getThreshold12 20

ringpi:mrcc:mscf1:getThreshold13 20

ringpi:mrcc:mscf1:getThreshold14 0

ringpi:mrcc:mscf1:getThreshold15 0

ringpi:mrcc:mscf1:getThreshold16 0

ringpi:mrcc:mscf1:getPz1 100

ringpi:mrcc:mscf1:getPz2 100

ringpi:mrcc:mscf1:getPz3 100

ringpi:mrcc:mscf1:getPz4 128

ringpi:mrcc:mscf1:getPz5 100

ringpi:mrcc:mscf1:getPz6 100

ringpi:mrcc:mscf1:getPz7 0

ringpi:mrcc:mscf1:getPz8 0

ringpi:mrcc:mscf1:getPz9 100

ringpi:mrcc:mscf1:getPz10 100

ringpi:mrcc:mscf1:getPz11 100

ringpi:mrcc:mscf1:getPz12 100

ringpi:mrcc:mscf1:getPz13 128

ringpi:mrcc:mscf1:getPz14 0

ringpi:mrcc:mscf1:getPz15 0

ringpi:mrcc:mscf1:getPz16 0

ringpi:mrcc:mscf2:getThreshold1 20

ringpi:mrcc:mscf2:getThreshold2 20

ringpi:mrcc:mscf2:getThreshold3 20

ringpi:mrcc:mscf2:getThreshold4 20

ringpi:mrcc:mscf2:getThreshold5 20

ringpi:mrcc:mscf2:getThreshold6 0

ringpi:mrcc:mscf2:getThreshold7 0

ringpi:mrcc:mscf2:getThreshold8 0

ringpi:mrcc:mscf2:getThreshold9 20

ringpi:mrcc:mscf2:getThreshold10 20

ringpi:mrcc:mscf2:getThreshold11 20

ringpi:mrcc:mscf2:getThreshold12 20

ringpi:mrcc:mscf2:getThreshold13 0

ringpi:mrcc:mscf2:getThreshold14 0

ringpi:mrcc:mscf2:getThreshold15 0

ringpi:mrcc:mscf2:getThreshold16 0

ringpi:mrcc:mscf2:getPz1 128

ringpi:mrcc:mscf2:getPz2 128

ringpi:mrcc:mscf2:getPz3 100

ringpi:mrcc:mscf2:getPz4 128

ringpi:mrcc:mscf2:getPz5 100

ringpi:mrcc:mscf2:getPz6 100

ringpi:mrcc:mscf2:getPz7 0

ringpi:mrcc:mscf2:getPz8 0

ringpi:mrcc:mscf2:getPz9 100

ringpi:mrcc:mscf2:getPz10 100

ringpi:mrcc:mscf2:getPz11 100

ringpi:mrcc:mscf2:getPz12 100

ringpi:mrcc:mscf2:getPz13 0

ringpi:mrcc:mscf2:getPz14 0

ringpi:mrcc:mscf2:getPz15 0

ringpi:mrcc:mscf2:getPz16 0

ringpi:mrcc:mscf3:getThreshold1 20

ringpi:mrcc:mscf3:getThreshold2 20

ringpi:mrcc:mscf3:getThreshold3 20

ringpi:mrcc:mscf3:getThreshold4 20

ringpi:mrcc:mscf3:getThreshold5 20

ringpi:mrcc:mscf3:getThreshold6 0

ringpi:mrcc:mscf3:getThreshold7 0

ringpi:mrcc:mscf3:getThreshold8 0

ringpi:mrcc:mscf3:getThreshold9 20

ringpi:mrcc:mscf3:getThreshold10 20

ringpi:mrcc:mscf3:getThreshold11 20

ringpi:mrcc:mscf3:getThreshold12 20

ringpi:mrcc:mscf3:getThreshold13 0

ringpi:mrcc:mscf3:getThreshold14 0

ringpi:mrcc:mscf3:getThreshold15 0

ringpi:mrcc:mscf3:getThreshold16 0

ringpi:mrcc:mscf3:getPz1 128

ringpi:mrcc:mscf3:getPz2 128

ringpi:mrcc:mscf3:getPz3 128

ringpi:mrcc:mscf3:getPz4 128

ringpi:mrcc:mscf3:getPz5 128

ringpi:mrcc:mscf3:getPz6 0

ringpi:mrcc:mscf3:getPz7 0

ringpi:mrcc:mscf3:getPz8 0

ringpi:mrcc:mscf3:getPz9 128

ringpi:mrcc:mscf3:getPz10 128

ringpi:mrcc:mscf3:getPz11 128

ringpi:mrcc:mscf3:getPz12 128

ringpi:mrcc:mscf3:getPz13 0

ringpi:mrcc:mscf3:getPz14 0

ringpi:mrcc:mscf3:getPz15 0

ringpi:mrcc:mscf3:getPz16 0

ringpi:mrcc:mscf4:getThreshold1 244

ringpi:mrcc:mscf4:getThreshold2 244

ringpi:mrcc:mscf4:getThreshold3 244

ringpi:mrcc:mscf4:getThreshold4 244

ringpi:mrcc:mscf4:getThreshold5 244

ringpi:mrcc:mscf4:getThreshold6 244

ringpi:mrcc:mscf4:getThreshold7 244

ringpi:mrcc:mscf4:getThreshold8 244

ringpi:mrcc:mscf4:getThreshold9 244

ringpi:mrcc:mscf4:getThreshold10 244

ringpi:mrcc:mscf4:getThreshold11 244

ringpi:mrcc:mscf4:getThreshold12 244

ringpi:mrcc:mscf4:getThreshold13 244

ringpi:mrcc:mscf4:getThreshold14 244

ringpi:mrcc:mscf4:getThreshold15 244

ringpi:mrcc:mscf4:getThreshold16 244

ringpi:mrcc:mscf4:getPz1 100

ringpi:mrcc:mscf4:getPz2 100

ringpi:mrcc:mscf4:getPz3 100

ringpi:mrcc:mscf4:getPz4 100

ringpi:mrcc:mscf4:getPz5 100

ringpi:mrcc:mscf4:getPz6 0

ringpi:mrcc:mscf4:getPz7 0

ringpi:mrcc:mscf4:getPz8 0

ringpi:mrcc:mscf4:getPz9 100

ringpi:mrcc:mscf4:getPz10 100

ringpi:mrcc:mscf4:getPz11 100

ringpi:mrcc:mscf4:getPz12 100

ringpi:mrcc:mscf4:getPz13 0

ringpi:mrcc:mscf4:getPz14 0

ringpi:mrcc:mscf4:getPz15 0

ringpi:mrcc:mscf4:getPz16 0

ringpi:mrcc:mscf5:getThreshold1 50

ringpi:mrcc:mscf5:getThreshold2 50

ringpi:mrcc:mscf5:getThreshold3 50

ringpi:mrcc:mscf5:getThreshold4 50

ringpi:mrcc:mscf5:getThreshold5 150

ringpi:mrcc:mscf5:getThreshold6 150

ringpi:mrcc:mscf5:getThreshold7 150

ringpi:mrcc:mscf5:getThreshold8 150

ringpi:mrcc:mscf5:getThreshold9 150

ringpi:mrcc:mscf5:getThreshold10 150

ringpi:mrcc:mscf5:getThreshold11 150

ringpi:mrcc:mscf5:getThreshold12 150

ringpi:mrcc:mscf5:getThreshold13 150

ringpi:mrcc:mscf5:getThreshold14 150

ringpi:mrcc:mscf5:getThreshold15 150

ringpi:mrcc:mscf5:getThreshold16 150

ringpi:mrcc:mscf5:getPz1 100

ringpi:mrcc:mscf5:getPz2 100

ringpi:mrcc:mscf5:getPz3 100

ringpi:mrcc:mscf5:getPz4 100

ringpi:mrcc:mscf5:getPz5 100

ringpi:mrcc:mscf5:getPz6 100

ringpi:mrcc:mscf5:getPz7 100

ringpi:mrcc:mscf5:getPz8 100

ringpi:mrcc:mscf5:getPz9 100

ringpi:mrcc:mscf5:getPz10 100

ringpi:mrcc:mscf5:getPz11 100

ringpi:mrcc:mscf5:getPz12 100

ringpi:mrcc:mscf5:getPz13 100

ringpi:mrcc:mscf5:getPz14 100

ringpi:mrcc:mscf5:getPz15 100

ringpi:mrcc:mscf5:getPz16 100

ringpi:mrcc:mscf1:getSingleChMode 0

ringpi:mrcc:mscf2:getSingleChMode 0

ringpi:mrcc:mscf3:getSingleChMode 0

ringpi:mrcc:mscf4:getSingleChMode 0

ringpi:mrcc:mscf5:getSingleChMode 1

ringpi:mrcc:mscf1:getRcMode 1

ringpi:mrcc:mscf2:getRcMode 1

ringpi:mrcc:mscf3:getRcMode 1

ringpi:mrcc:mscf4:getRcMode 1

ringpi:mrcc:mscf5:getRcMode 1

ringpi:mrcc:mscf1:getAutoPZ 0

ringpi:mrcc:mscf2:getAutoPZ 0

ringpi:mrcc:mscf3:getAutoPZ 0

ringpi:mrcc:mscf4:getAutoPZ 1

ringpi:mrcc:mscf5:getAutoPZ 0

ringpi:mrcc:mscf1:getMultiplicityHi 8

ringpi:mrcc:mscf2:getMultiplicityHi 1

ringpi:mrcc:mscf3:getMultiplicityHi 1

ringpi:mrcc:mscf4:getMultiplicityHi 1

ringpi:mrcc:mscf5:getMultiplicityHi 4

ringpi:mrcc:mscf1:getMultiplicityLo 8

ringpi:mrcc:mscf2:getMultiplicityLo 0

ringpi:mrcc:mscf3:getMultiplicityLo 0

ringpi:mrcc:mscf4:getMultiplicityLo 0

ringpi:mrcc:mscf5:getMultiplicityLo 4

ringpi:mrcc:mscf1:getSumTrgThresh 0

ringpi:mrcc:mscf2:getSumTrgThresh 0

ringpi:mrcc:mscf3:getSumTrgThresh 0

ringpi:mrcc:mscf4:getSumTrgThresh 0

ringpi:mrcc:mscf5:getSumTrgThresh 0

ringpi:mrcc:mscf1:getBlrOn 1

ringpi:mrcc:mscf2:getBlrOn 1

ringpi:mrcc:mscf3:getBlrOn 1

ringpi:mrcc:mscf4:getBlrOn 1

ringpi:mrcc:mscf5:getBlrOn 1

ringpi:mrcc:mscf1:getCoincTime 121

ringpi:mrcc:mscf2:getCoincTime 0

ringpi:mrcc:mscf3:getCoincTime 0

ringpi:mrcc:mscf4:getCoincTime 0

ringpi:mrcc:mscf5:getCoincTime 0

ringpi:mrcc:mscf1:getThreshOffset 0

ringpi:mrcc:mscf2:getThreshOffset 0

ringpi:mrcc:mscf3:getThreshOffset 0

ringpi:mrcc:mscf4:getThreshOffset 0

ringpi:mrcc:mscf5:getThreshOffset 0

ringpi:mrcc:mscf1:getShaperOffset 0

ringpi:mrcc:mscf2:getShaperOffset 0

ringpi:mrcc:mscf3:getShaperOffset 0

ringpi:mrcc:mscf4:getShaperOffset 0

ringpi:mrcc:mscf5:getShaperOffset 0

ringpi:mrcc:mscf1:getBlrThresh 20

ringpi:mrcc:mscf2:getBlrThresh 20

ringpi:mrcc:mscf3:getBlrThresh 25

ringpi:mrcc:mscf4:getBlrThresh 25

ringpi:mrcc:mscf5:getBlrThresh 25

ringpi:mrcc:mscf1:getECLDelay 0

ringpi:mrcc:mscf2:getECLDelay 0

ringpi:mrcc:mscf3:getECLDelay 0

ringpi:mrcc:mscf4:getECLDelay 0

ringpi:mrcc:mscf5:getECLDelay 0

|

| Attachment 2: det_mapping.png

|

|

|

180

|

Tue Dec 8 15:47:07 2020 |

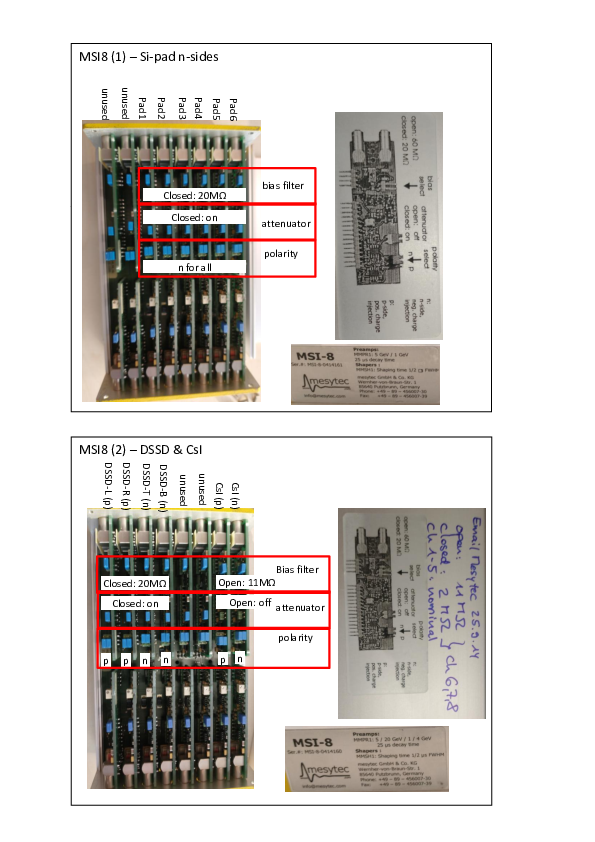

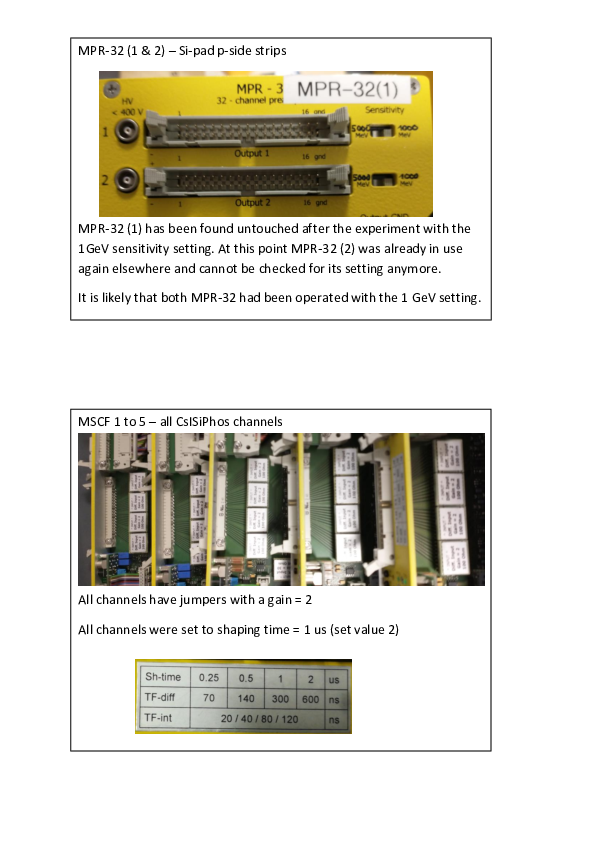

Jan | Detectors | manual preamp & shaper settings for CsISiPhos | attached is a document showing fotos of all involved amplifiers in the chain to document the manual settings active during the experiment.

Summary:

Si-pad n-sides [MSI-8 (1)] were set to 5 GeV (expected E-deposition ~2 GeV)

Si-pad p-sides [MPR-32 (1 & 2)] were set to 1 GeV (expected E-deposition ~2 GeV)

DSSD channels [MSI-8 (2)] were set to 5 GeV (expected E-deposition ~1.2 GeV)

CsI channels [MSI-8 (2)] were set to 4 GeV (expected E-deposition 46 GeV)

It seems we got clipped signals from the Si-pad p-sides, because the MPR-32 were saturated due to a wrong gain setting.

This might explain, why there was not real influence on the spectra when adjusting MSCF settings for those channels.

I cannot comment on the CsI gain setting, because i don't know whether the given GeV-range by MesyTec directly applies for CsI & photodiode.

However, for DSSD and Si-pad n-sides the settings look okay. |

| Attachment 1: amp_settings.pdf

|

|

|

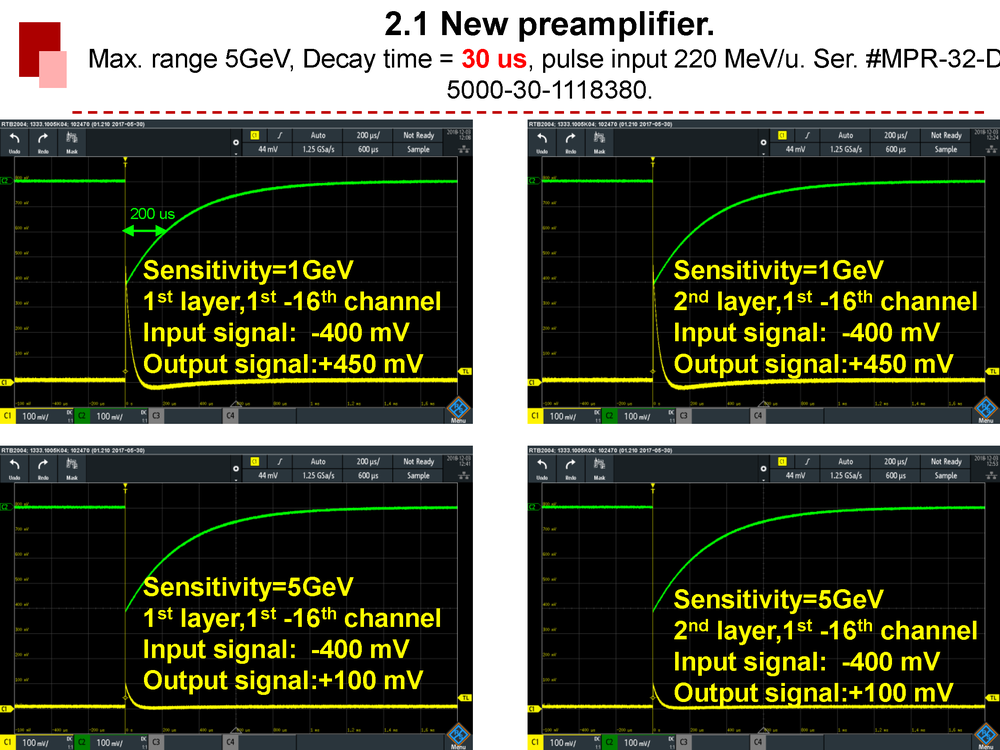

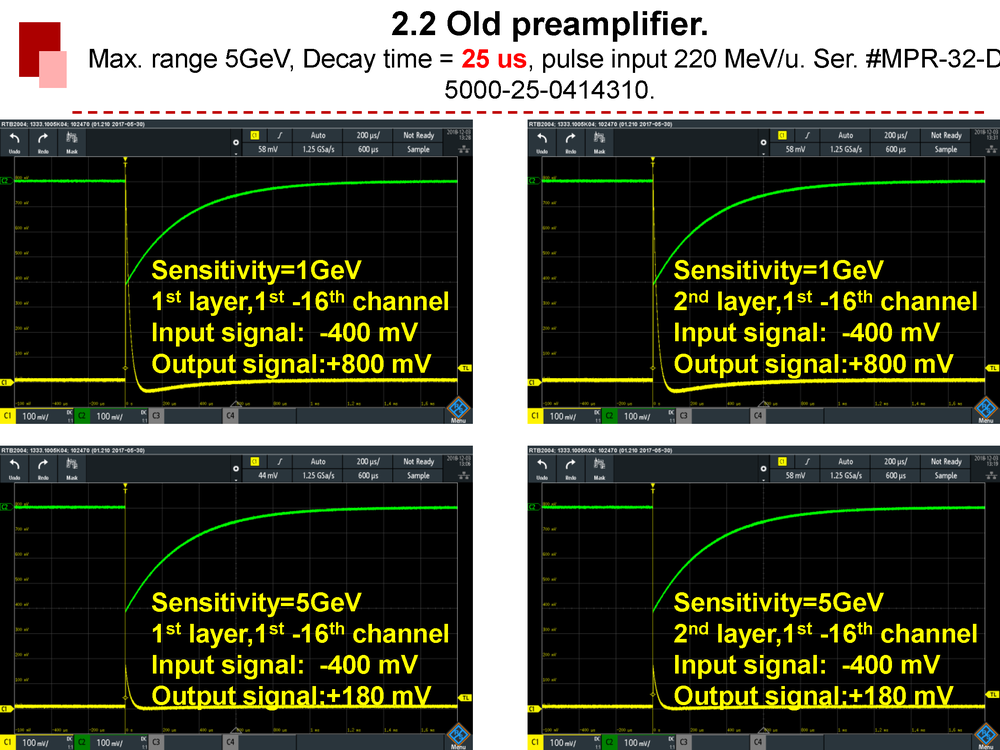

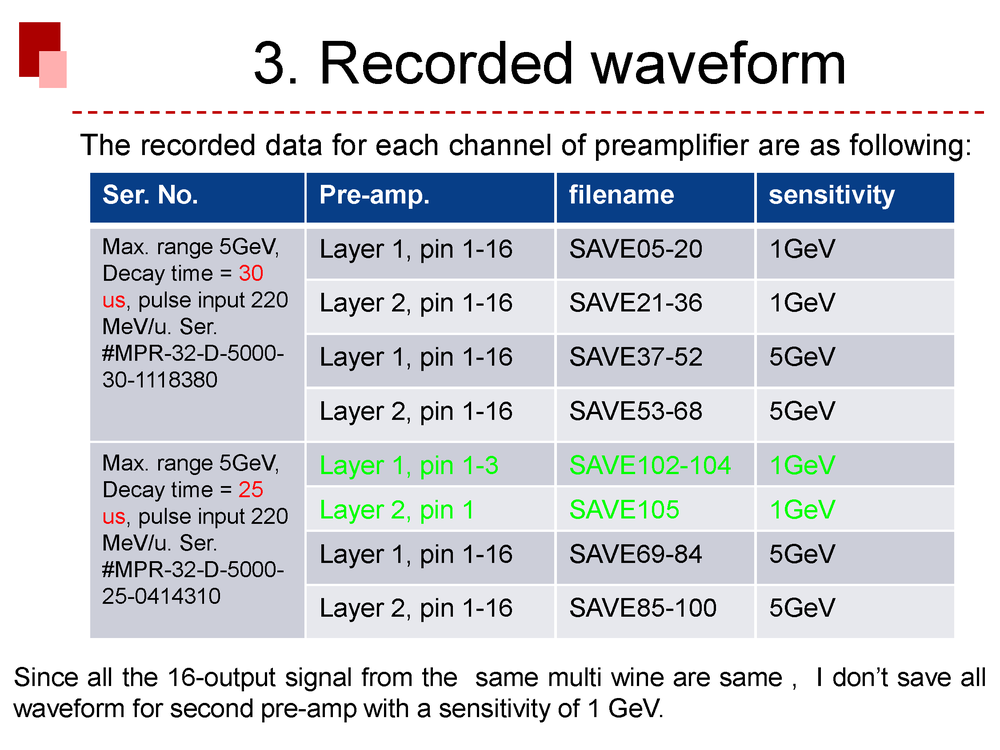

2

|

Mon Dec 3 15:06:04 2018 |

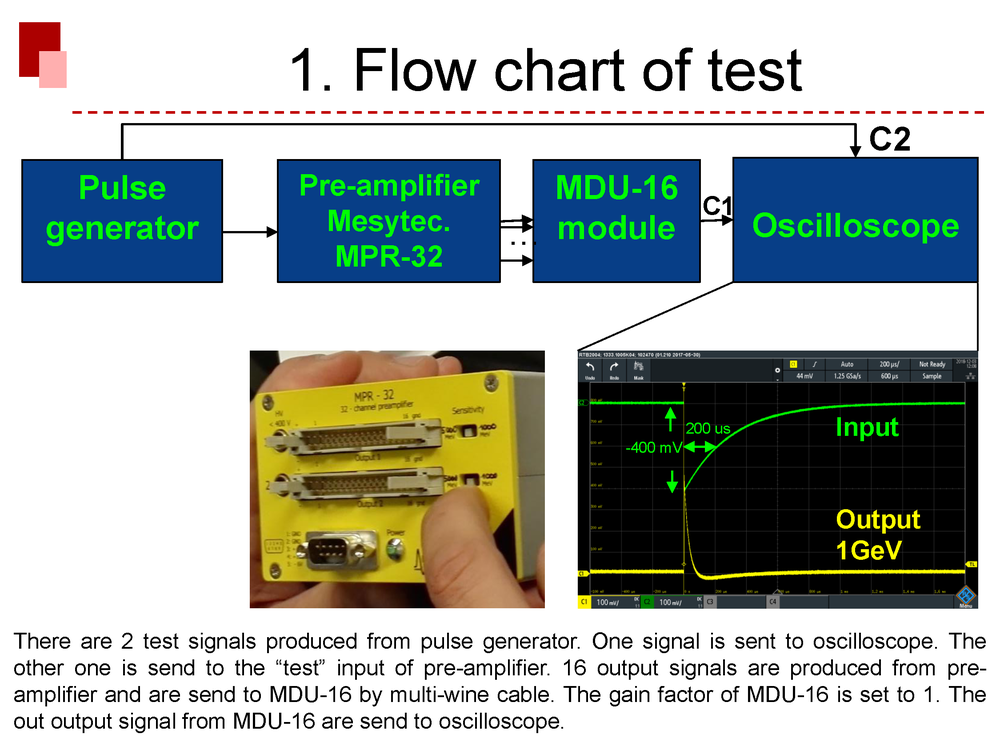

Chen, Sidhu | DAQ | Test of two preamplifier. | Description:

We have two pre-amplifiers:

New: Max. range 5GeV, Two sensitivity options: 1 GeV and 5 GeV, Decay time = 30 us, pulse input 220 MeV/u, Ser. #MPR-32-D-5000-30-1118380.

Old: Max. range 5GeV, Two sensitivity options: 1 GeV and 5 GeV, Decay time = 25 us, pulse input 220 MeV/u. Ser. #MPR-32-D-5000-25-0414310.

Conclusion:

Both pre-amplifiers work well.

The summary is attached in the followings:

|

|

7

|

Tue Mar 12 12:54:58 2019 |

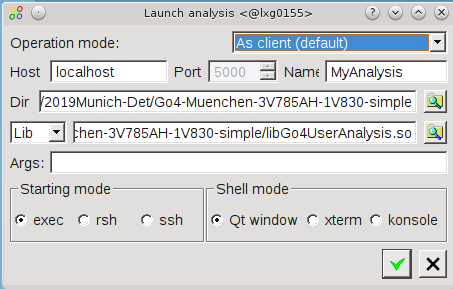

Chen, Sidhu | DAQ | how to start DAQ and plot histogram. | 1. login litv-exp account

rchen@lxg1254:/data.local2/2002_238UIMS$ ssh -X litv-exp@lxg0155.gsi.de

(don't login on lx-pool.)

litv-exp@lx-pool.gsi.de's password: ViValasVegas@****

2.login r4l-47 account

litv-exp@lxi087:~$ ssh r4l-47

litv-exp@r4l-47's password:ViValasVegas@****

3.start mbs

R4L-47 litv-exp > mbs

mbs>

mbs> -R4L-47 :msg_log :Message logger running

3.1 Initilizing, show, start and stop the acq

mbs> @startup

-R4L-47  ispatch :Task "m_util" not started! ispatch :Task "m_util" not started!

mbs> @startup

-R4L-47 :util :task m_util started

-R4L-47 :util :setup file setup.usf successfully loaded

-R4L-47 :util :trigger module set up as MASTER, crate nr: 0

-R4L-47 :util :enabled interrupt

-R4L-47 :collector  ipe type 2 or 4: virtual mapping ipe type 2 or 4: virtual mapping

-R4L-47 :transport :task m_transport started

-R4L-47 :read_meb  ipe type 2 or 4: virtual mapping ipe type 2 or 4: virtual mapping

-R4L-47 :transport :starting server in inclusive mode

-R4L-47 :transport :waiting for client (port 6000)

mbs> -R4L-47 :read_meb :task m_read_meb started

-R4L-47 :stream_serv:task m_stream_serv started

-R4L-47 :collector :task m_collector started

mbs> show acq

-R4L-47  ispatch :Task "m_util" not started! ispatch :Task "m_util" not started!

mbs> show acq

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :ACQUISITION INITIALIZED 12-Mar-19 13:44:09: active tasks:

-R4L-47 :util :m_util m_transport m_daq_rate m_collector m_stream_serv

-R4L-47 :util :m_read_meb

-R4L-47 :util :SB setup LOADED from setup.usf.

-R4L-47 :util :Readout table NOT LOADED, acquisition STOPPED.

-R4L-47 :util :There are 32 streams with 32 buffers a 32768 each.

-R4L-47 :util :Current crate is 0, event builder is RIO4.

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Crate 0: ID= 20, LOCAL SYNC SYNC , subevent slots=200000.

-R4L-47 :util : trig 1: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 2: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 3: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 4: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 5: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 6: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 7: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 8: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 9: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 10: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 11: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 12: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 13: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 14: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util : trig 15: cvt= 300, fclrt= 12 [usec], max se length=100000 b

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Name of output device =

-R4L-47 :util :Tape label = , Dismounted, file CLOSED

-R4L-47 :util : 0.000 [MB] written to tape, 0.000 to file

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Collected: 0.0000 MB, 0 Buffers, 0 Events.

-R4L-47 :util :Rate : 0 KB/s, 0 Buffers/s, 0 Events/s

-R4L-47 :util :--------------------------------------------------------------

mbs> start acq

mbs> stop acq

-R4L-47 :util :stop acquisition

mbs> -R4L-47 :collector :acquisition NOT running

-R4L-47 :read_meb :found trig type 15 == stop acquisition

4. plot the histogram

litv-exp@lxi087:~/2019Munich-Det/Go4-Muenchen-3V785AH-1V830-simple$ go4

Go4 v5.3.2, build with ROOT 6.12/06 and Qt 4.8.6

Using Qt settings at /u/litv-exp/.config/GSI/go4.conf (default)

|

|

9

|

Tue May 28 08:36:14 2019 |

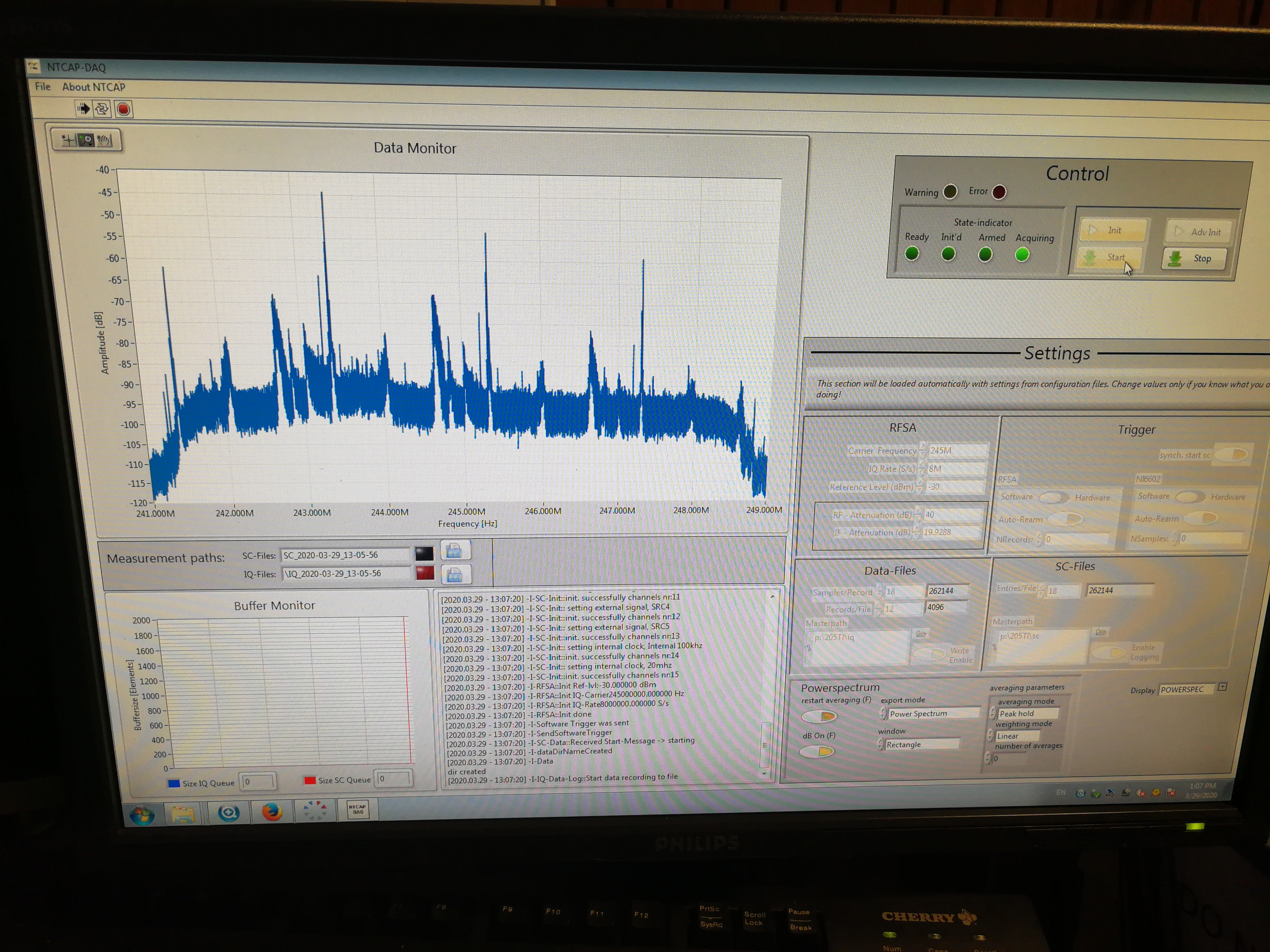

Jan | DAQ | MBS start & RFIO server | You need a DAQ-PC and the RIO crate computer.

All of the DAQ proceedures laid out here are operated from inside the DAQ screen session.

Right now for e121 the following DAQ-setup is used: (might change in the future)

DAQ-PC: lxg0155

screen session: e121_daq @ lxg0155

RIO: r4l-47

DAQ dir: /esr/usr/litv-exp/2019Munich-Det

The most important commands:

on DAQ-PC

mbs - start mbs DAQ

rawDispRFIO64 - start RFIO server

in MBS shell

@startup - initialize MBS (only inside DAQ dir)

@connect - connect RFIO server (only if server running)

@runstart - open file for data writing

@runstop - close file

start acq - start DAQ

show acq - status of DAQ

show file - status of current file/RFIO server

The full proceedure for the DAQ:

- on DAQ-PC enter screen session:

litv-exp@lxg____:~$ screen -x e121_daq or create new screen session if non is exisiting:litv-exp@lxg____:~$ screen -S e121_daq - inside screen: go to 1st tab (MBS) and login to RIO if not yet done:

<Ctrl-a 0>

litv-exp@lxg____:~$ ssh r4l-47

- on RIO reset and start MBS

R4L-47 litv-exp > cd 2019Munich-Det

R4L-47 litv-exp > resl

R4L-47 litv-exp > mbs

mbs > @startup

- inside screen go to 2nd tab (RFIO)

<Ctrl-a 1> or create 2nd tab if not exisiting<Ctrl-a c> - start RFIO server on DAQ-PC

litv-exp@lxg____:~$ cd /u/litv-exp/rfio

litv-exp@lxg____:~$ ./rawDispRFIO64-wheezy

-I- 64 bit RFIO test server (lxg0155) listening on port 1974

forks './rawServRFIO64-wheezy' for each client request - inside screen go to 1st tab and connect MBS to RFIO server

<Ctrl-a 0>

mbs > @connect

mbs> show file

mbs> -R4L-47 :transport :Name of output device = RFIO

-R4L-47 :transport :current tape label = lxg0155 , opened

-R4L-47 :transport :current file name = , closed

-R4L-47 :transport : 0.000 MBytes written to tape

-R4L-47 :transport : 0.000 MBytes written to current file - start acquisition

mbs > start acq

mbs > show acq

...

-R4L-47 :util :Name of output device = RFIO

-R4L-47 :util :RFIO server lxg0155, file CLOSED

-R4L-47 :util : 0.000 [MB] written to tape, 0.000 to file

-R4L-47 :util :--------------------------------------------------------------

-R4L-47 :util :Collected: 61.1451 MB, 1866 Buffers, 131990 Events.

-R4L-47 :util :Rate : 33 KB/s, 1 Buffers/s, 71 Events/s

-R4L-47 :util :-------------------------------------------------------------- - open file / start a run

mbs > @runstart

-R4L-47 :transport :open file at server lxg0155::

-R4L-47 :transport :/data.local1/E121/predata/e121_run_1239.lmd - close file / stop a run

mbs > @runstop

-R4L-47 :transport :Rfio server lxg0155: closed file after 0.262 MB written:

-R4L-47 :transport :-I- remote output file /data.local1/E121/predata/e121_run_1239.lmd closed

mbs> -R4L-47 :transport :/data.local1/E121/predata/e121_run_1239.lmd

|

|

10

|

Wed Jun 26 16:20:31 2019 |

Jan | DAQ | unpacker: lmd > root | I have written an unpacker for the lmd data taken with the current daq-system for E121.

The crate configuration is as follows:

ADC1 channels 1-32 (Caen 785)

ADC2 channels 1-32 (Caen 785)

ADC3 channels 1-32 (Caen 785)

SCALER channels 1-32 (Caen 830)

The unpacker binary can be found here

/u/litv-exp/unpacker/unpackexps/E121/E121

The current spec file is attached.

To convert lmd-files to root-files, please use it as follows:litv-exp@lxg___: E121_unpacker /path/to/file.lmd --ntuple=RAW,/path/to/new_file.root |

| Attachment 1: E121.spec

|

// -*- C++ -*-

ADC(start)

{

MEMBER(DATA12 data[32]);

list(0 <= ch < 32)

{

UINT32 item NOENCODE

{

0_15: channel;

16_27: value;

28_31: 0;

ENCODE(data[channel - start], (value=value));

}

}

}

SCALER(start)

{

MEMBER(DATA32 data[32]);

list(0 <= ch < 32)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel / 2) - start], (value=(high.value << 16) | low.value));

}

}

SUBEVENT(ESR)

{

adc[0] = ADC(start = 0);

adc[1] = ADC(start = 32);

adc[2] = ADC(start = 64);

select optional {

scaler[0] = SCALER(start = 0x100);

}

}

EVENT

{

esr = ESR(type = 10, subtype = 1);

}

#include "det_mapping.hh"

|

| Attachment 2: det_mapping.hh

|

SIGNAL( ADC1_1, esr.adc[0].data[0],

ADC1_32, esr.adc[0].data[31], DATA12);

SIGNAL( ADC2_1, esr.adc[1].data[0],

ADC2_32, esr.adc[1].data[31], DATA12);

SIGNAL( ADC3_1, esr.adc[2].data[0],

ADC3_32, esr.adc[2].data[31], DATA12);

//SIGNAL( SC_1, esr.scaler[0].data[0],

// SC_32, esr.scaler[0].data[31],DATA32);

|

|

15

|

Tue Feb 25 15:48:31 2020 |

ruijiu chen | DAQ | Important folders of e121 eperiments: | 1. slow control:

1.1. program file:

litv-exp@ringpi:~/epics/mrcc_ioc/db $

1.2 user interface:

litv-exp@lxg1298:~/E121/scripts/GUIe121_new

2. mbs:

2.1 user interface

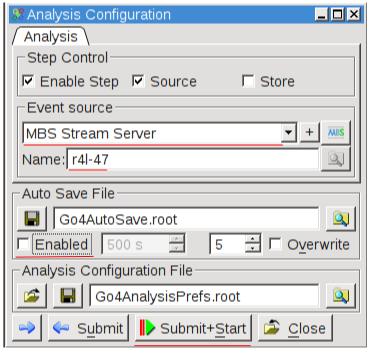

litv-exp@lxg1298:~/E121/scripts$ ./e121_gui.py

2.2 source

R4L-47 litv-exp > pwd

/esr/usr/litv-exp/2020_e121/

3. go4:

litv-exp@lxg1298:~/2019Munich-Det/Go4-Muenchen-3V785AH-1V830-simple$ go4

4. experimenal data:

litv-exp@lxg1298:/data.local1/E121 |

|

16

|

Tue Feb 25 15:49:58 2020 |

ruijiu chen | DAQ | changing scaling factor. | How to change scaling factor?

The parameters is in f_user.c file:

1. open the f_user.C with emacs :

R4L-47 litv-exp > emacs -nw f_user.c

2. change the parameters "MWPC_downscale".

#define MWPC_downscale 0 // reduction = 2**MWPC_downscale

3.compile the program.

4. restart mbs. |

|

33

|

Sat Mar 28 12:19:21 2020 |

Ragan, RuiJiu | DAQ | Change of the polarity of Amplifiers | Since last night, the signals from the p-side of all the Si pads were seen as negative on picoscope.

The signals from DSSSD, all n-sides of Si pads and CsI were positive which all are in MSCF-5.

Thus, I and RuiJiu, changed the polarity jumpers of MSCF 1,2,3 and 4(all the four jumpers inside the mentioned MSCF) and now hope to see positive signals from the p-side of all the Si pads. |

| Attachment 1: 7888530B-DE66-4D37-A0A8-933307DD2AB8.MOV

|

|

37

|

Sat Mar 28 15:07:40 2020 |

ruijiu | DAQ | start run | |

|

41

|

Sat Mar 28 16:12:25 2020 |

ruijiu, ragan | DAQ | enter ESR and turn on the HV crate. | |

|

44

|

Sun Mar 29 09:40:35 2020 |

ruijiu | DAQ | restart go4 | go4 crush up.

the problem is

due to mbs.

restart mbs.

see an error.

restart again.

the mbs and go4

are working

working. |

| Attachment 1: IMG_20200329_093354.jpg

|

|

|

51

|

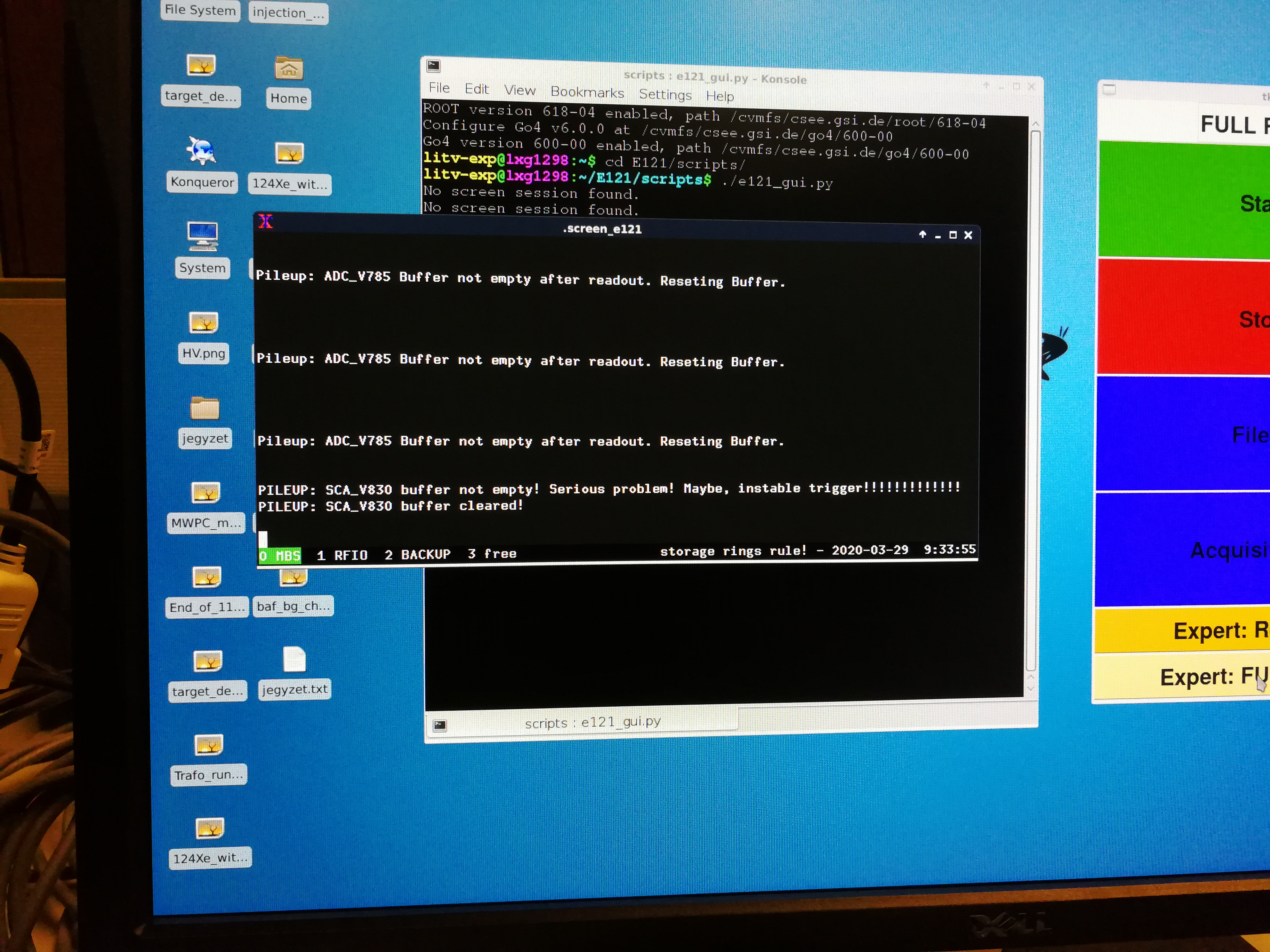

Sun Mar 29 13:05:36 2020 |

ruijiu | DAQ | start ntcap | IQ_2020-03-29_13-05-

56

SC_2020-03-29_13-05-

56 |

| Attachment 1: IMG_20200329_130438.jpg

|

|

|

98

|

Mon Mar 30 14:24:46 2020 |

ruijiu | DAQ | stop taking data. | 1. stop run0272.lmd.

2. stop NTCAP.

NTCAp file:

SC_2020-03-30_09-28-14

IQ_2020-03-30_09-28-14

(saved in drive: p) |

|

175

|

Thu Oct 1 22:20:03 2020 |

Jan | DAQ | final unpacker config | We identified an issue with randomly missing adc channels in all lmd-files before run 0273.

This led to errors in the unpacking process.

This issue is solved with the new config and mapping for the unpacker.

The respective files are attached here.

The unpacker is ready to use in /u/litv-exp/unpacker/unpackexps/E121

The adc issue is also understood. We deactivated the internal adc thresholds during the experiment, because we encountered the very same unpacker errors. This solved the problem for all later runs, but we forgot to think about a solution for the earlier runs.

Mea culpa.

Jan |

| Attachment 1: E121.spec

|

// -*- C++ -*-

ADC_CH(start, id)

{

MEMBER(DATA12 data[96]);

UINT32 item NOENCODE

{

0_15: channel = MATCH(id);

16_27: value;

28_31: unknown;

ENCODE(data[channel - start], (value=value));

}

}

SCALER(start)

{

MEMBER(DATA32 data[32]);

list(0 <= ch < 32)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel - start) / 2], (value=(high.value << 16) | low.value));

}

}

TDC(start)

{

MEMBER(DATA32 data);

UINT32 high NOENCODE

{

0_15: channel = MATCH(start);

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data,(value=(high.value << 16) | low.value));

}

TBOX(start)

{

MEMBER(DATA32 data[16]);

list(0 <= ch < 16)

{

UINT32 high NOENCODE

{

0_15: channel;

16_31: value;

}

UINT32 low NOENCODE

{

0_15: channel;

16_31: value;

}

ENCODE(data[(high.channel - start) / 2], (value=(high.value << 16) | low.value));

}

}

SUBEVENT(ESR)

{

tb_in[0] = TBOX(start = 0x300);

tb_inhibit[0] = TBOX(start = 0x380);

tb_red[0] = TBOX(start = 0x400);

// adc[0] = ADC(start = 0);

// adc[1] = ADC(start = 32);

// adc[2] = ADC(start = 64);

select several {

adc[0] = ADC_CH(start = 0 , id = 0);

adc[0] = ADC_CH(start = 0 , id = 1);

adc[0] = ADC_CH(start = 0 , id = 2);

adc[0] = ADC_CH(start = 0 , id = 3);

adc[0] = ADC_CH(start = 0 , id = 4);

adc[0] = ADC_CH(start = 0 , id = 5);

adc[0] = ADC_CH(start = 0 , id = 6);

adc[0] = ADC_CH(start = 0 , id = 7);

adc[0] = ADC_CH(start = 0 , id = 8);

adc[0] = ADC_CH(start = 0 , id = 9);

adc[0] = ADC_CH(start = 0 , id = 10);

adc[0] = ADC_CH(start = 0 , id = 11);

adc[0] = ADC_CH(start = 0 , id = 12);

adc[0] = ADC_CH(start = 0 , id = 13);

adc[0] = ADC_CH(start = 0 , id = 14);

adc[0] = ADC_CH(start = 0 , id = 15);

adc[0] = ADC_CH(start = 0 , id = 16);

adc[0] = ADC_CH(start = 0 , id = 17);

adc[0] = ADC_CH(start = 0 , id = 18);

adc[0] = ADC_CH(start = 0 , id = 19);

adc[0] = ADC_CH(start = 0 , id = 20);

adc[0] = ADC_CH(start = 0 , id = 21);

adc[0] = ADC_CH(start = 0 , id = 22);

adc[0] = ADC_CH(start = 0 , id = 23);

adc[0] = ADC_CH(start = 0 , id = 24);

adc[0] = ADC_CH(start = 0 , id = 25);

adc[0] = ADC_CH(start = 0 , id = 26);

adc[0] = ADC_CH(start = 0 , id = 27);

adc[0] = ADC_CH(start = 0 , id = 28);

adc[0] = ADC_CH(start = 0 , id = 29);

adc[0] = ADC_CH(start = 0 , id = 30);

adc[0] = ADC_CH(start = 0 , id = 31);

adc[1] = ADC_CH(start = 32, id = 32);

adc[1] = ADC_CH(start = 32, id = 33);

adc[1] = ADC_CH(start = 32, id = 34);

adc[1] = ADC_CH(start = 32, id = 35);

adc[1] = ADC_CH(start = 32, id = 36);

adc[1] = ADC_CH(start = 32, id = 37);

adc[1] = ADC_CH(start = 32, id = 38);

adc[1] = ADC_CH(start = 32, id = 39);

adc[1] = ADC_CH(start = 32, id = 40);

adc[1] = ADC_CH(start = 32, id = 41);

adc[1] = ADC_CH(start = 32, id = 42);

adc[1] = ADC_CH(start = 32, id = 43);

adc[1] = ADC_CH(start = 32, id = 44);

adc[1] = ADC_CH(start = 32, id = 45);

adc[1] = ADC_CH(start = 32, id = 46);

adc[1] = ADC_CH(start = 32, id = 47);

adc[1] = ADC_CH(start = 32, id = 48);

adc[1] = ADC_CH(start = 32, id = 49);

adc[1] = ADC_CH(start = 32, id = 50);

adc[1] = ADC_CH(start = 32, id = 51);

adc[1] = ADC_CH(start = 32, id = 52);

adc[1] = ADC_CH(start = 32, id = 53);

adc[1] = ADC_CH(start = 32, id = 54);

adc[1] = ADC_CH(start = 32, id = 55);

adc[1] = ADC_CH(start = 32, id = 56);

adc[1] = ADC_CH(start = 32, id = 57);

adc[1] = ADC_CH(start = 32, id = 58);

adc[1] = ADC_CH(start = 32, id = 59);

adc[1] = ADC_CH(start = 32, id = 60);

adc[1] = ADC_CH(start = 32, id = 61);

adc[1] = ADC_CH(start = 32, id = 62);

adc[1] = ADC_CH(start = 32, id = 63);

adc[2] = ADC_CH(start = 64, id = 64);

adc[2] = ADC_CH(start = 64, id = 65);

adc[2] = ADC_CH(start = 64, id = 66);

adc[2] = ADC_CH(start = 64, id = 67);

adc[2] = ADC_CH(start = 64, id = 68);

adc[2] = ADC_CH(start = 64, id = 69);

adc[2] = ADC_CH(start = 64, id = 70);

adc[2] = ADC_CH(start = 64, id = 71);

adc[2] = ADC_CH(start = 64, id = 72);

adc[2] = ADC_CH(start = 64, id = 73);

adc[2] = ADC_CH(start = 64, id = 74);

adc[2] = ADC_CH(start = 64, id = 75);

adc[2] = ADC_CH(start = 64, id = 76);

adc[2] = ADC_CH(start = 64, id = 77);

adc[2] = ADC_CH(start = 64, id = 78);

adc[2] = ADC_CH(start = 64, id = 79);

adc[2] = ADC_CH(start = 64, id = 80);

adc[2] = ADC_CH(start = 64, id = 81);

adc[2] = ADC_CH(start = 64, id = 82);

adc[2] = ADC_CH(start = 64, id = 83);

adc[2] = ADC_CH(start = 64, id = 84);

adc[2] = ADC_CH(start = 64, id = 85);

adc[2] = ADC_CH(start = 64, id = 86);

adc[2] = ADC_CH(start = 64, id = 87);

adc[2] = ADC_CH(start = 64, id = 88);

adc[2] = ADC_CH(start = 64, id = 89);

adc[2] = ADC_CH(start = 64, id = 90);

adc[2] = ADC_CH(start = 64, id = 91);

adc[2] = ADC_CH(start = 64, id = 92);

adc[2] = ADC_CH(start = 64, id = 93);

adc[2] = ADC_CH(start = 64, id = 94);

adc[2] = ADC_CH(start = 64, id = 95);

}

select optional {

scaler[0] = SCALER(start = 0x100);

}

select several {

tdc[0] = TDC(start = 0x200);

tdc[1] = TDC(start = 0x202);

tdc[2] = TDC(start = 0x204);

tdc[3] = TDC(start = 0x206);

tdc[4] = TDC(start = 0x208);

tdc[5] = TDC(start = 0x20a);

tdc[6] = TDC(start = 0x20c);

tdc[7] = TDC(start = 0x20e);

tdc[8] = TDC(start = 0x210);

tdc[9] = TDC(start = 0x212);

}

}

EVENT

{

esr = ESR(type = 10, subtype = 1);

}

#include "det_mapping.hh"

|

| Attachment 2: det_mapping.hh

|

SIGNAL( ADC1_1, esr.adc[0].data[0],

ADC1_32, esr.adc[0].data[31], DATA12);

SIGNAL( ADC2_1, esr.adc[1].data[0],

ADC2_32, esr.adc[1].data[31], DATA12);

SIGNAL( ADC3_1, esr.adc[2].data[0],

ADC3_32, esr.adc[2].data[31], DATA12);

SIGNAL( SC_1, esr.scaler[0].data[0],

SC_32, esr.scaler[0].data[31],DATA32);

SIGNAL( TDC_1, esr.tdc[0].data,

TDC_10, esr.tdc[9].data,DATA32);

SIGNAL( TB_SI_IN, esr.tb_in[0].data[0],DATA32);

SIGNAL( TB_SI_RED, esr.tb_red[0].data[0],DATA32);

SIGNAL( TB_MWPC_IN, esr.tb_in[0].data[1],DATA32);

SIGNAL( TB_MWPC_RED, esr.tb_red[0].data[1],DATA32);

|

|

176

|

Mon Nov 2 16:45:55 2020 |

Jan | DAQ | f_user & mbslog | Attached is the f_user.c and the mbslog.l files.

The readout function is for the following setup:

3x ADC CAEN V785

1x SCA CAEN V830

1x TDC CAEN V1190

1x Vulom TRB5 (triggerbox)

1x Vulom4b PEV (priority encoder)

1x TRIVA7

1x RIO4 R4L-47 |

| Attachment 1: f_user.c

|

/* CAEN V785 32 channel ADC*/

#include "stdio.h"

#include "s_veshe.h"

//----------------------------------------------

#define MWPC_downscale 0 // reduction = 2**MWPC_downscale

#define SI_downscale 0

#define VME_BASE 0x00000000

#define TB__OFFSET 0x05000000

#define TB__No_Ch 16

#define TB__No_Ch_enabled 16

#define TB__lmd_offset 0x300

#define ADC_V785__VME_OFFSET 0x00200000

#define ADC_V785__VME_SIZE 0x10000

#define ADC_V785__No_Ch 32

#define ADC_V785__lmd_offset 0x00

#define ADC_V785__No_Mod 3

#define SCA_V830_VME_OFFSET 0x00000000

#define SCA_V830_VME_SIZE 0x10000

#define SCA_V830__No_Ch 32

#define SCA_V830__lmd_offset 0x100

#define TDC_V1190a__OFFSET 0x01200000

#define TDC_V1190a__VME_SIZE 0x10000

#define TDC_V1190a__No_Ch 128

#define TDC_V1190a__No_hit_per_Ch 1 //only single hit allowed

#define TDC_V1190a__lmd_offset 0x200

#define TDC_V1190a__win_width 200

#define TDC_V1190a__win_offset -180

const long TB_Ch_enable_reg_F_0 = 0x00FF ;

//------------//

// scale down: ch00, ch01, ch02

const long TB_scale_down_0_F[TB__No_Ch] ={ SI_downscale,MWPC_downscale,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

const long ADC_threshold_value = 0x0000 ;

/*****************************************************************************/

/*

* all pointer wllhich are used for read/write operations in the functions

* f_user_init and f_user_readout must be defined here as static variables

*/

static long volatile *pl_VME_virtual_mem_base ;

static long volatile *pl_trig_vme_str; // triva status register

static long ll_evt_ctr = 0;

/* TB - Triggerbox on Vulom3 */

static long volatile *pl_TB__base ;

static long volatile *pl_TB__Ch_enable_reg_F_0 ;

static long volatile *pl_TB__scale_down_7_0 ;

static long volatile *pl_TB__scale_down_F_8 ;

static long volatile *pl_TB__latch_reg ;

static long volatile *pl_TB__version ;

static long volatile *pl_TB__scaler_inp [TB__No_Ch];

static long volatile *pl_TB__scaler_inhib [TB__No_Ch] ;

static long volatile *pl_TB__scaler_after_reduction [TB__No_Ch] ;

long TB__scaler_inp_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

long TB__scaler_inhib_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

long TB__scaler_after_reduction_old [TB__No_Ch] = { 0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0} ;

/* ADC - Analog to Digital Converter CAEN V785AH */

static long volatile *pl_ADC_V785__base [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__firm_rev [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__geo_adr [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__oui_msb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__oui [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__oui_lsb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__version [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id_msb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__board_id_lsb [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__revision [ADC_V785__No_Mod] ;

static short volatile *ps_ADC_V785__serial_msb [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__serial_lsb [ADC_V785__No_Mod];

static long volatile *pl_ADC_V785__outp_buffer [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_set_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_clr_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__stat_reg_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__ctrl_reg_1 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__stat_reg_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_set_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__bit_clr_2 [ADC_V785__No_Mod];

static short volatile *ps_ADC_V785__threshs[ADC_V785__No_Ch] [ADC_V785__No_Mod];

/* SCA - Scaler CAEN V830 */

static long volatile *pl_SCA_V830__base;

static long volatile *pl_SCA_V830__outp_buffer;

static long volatile *pl_SCA_V830__counter[SCA_V830__No_Ch];

static short volatile *ps_SCA_V830__scaler_clr;

static short volatile *ps_SCA_V830__scaler_status_reg;

static short volatile *ps_SCA_V830__fixed_code;

static short volatile *ps_SCA_V830__manuf_mod_type;

static short volatile *ps_SCA_V830__version_series;

static short volatile *ps_SCA_V830__firm_rev;

static short volatile *ps_SCA_V830__geo_adr;

static short volatile *ps_SCA_V830__oui_msb ;

static short volatile *ps_SCA_V830__oui ;

static short volatile *ps_SCA_V830__oui_lsb ;

static short volatile *ps_SCA_V830__version ;

static short volatile *ps_SCA_V830__board_id_msb ;

static short volatile *ps_SCA_V830__board_id ;

static short volatile *ps_SCA_V830__board_id_lsb ;

static short volatile *ps_SCA_V830__revision ;

static short volatile *ps_SCA_V830__serial_msb;

static short volatile *ps_SCA_V830__serial_lsb;

static short volatile *ps_SCA_V830__bit_set_1 ;

static short volatile *ps_SCA_V830__bit_clr_1 ;

static short volatile *ps_SCA_V830__stat_reg_1;

static short volatile *ps_SCA_V830__ctrl_reg_1;

static short volatile *ps_SCA_V830__sw_clr_reg ;

long SCA_V830__data_old [SCA_V830__No_Ch] ;

/* TDC - Time to Digital Converter CAEN V1190a */

static long volatile *pl_TDC_V1190a__base ;

static long volatile *pl_TDC_V1190a__outp_buffer ;

static short volatile *ps_TDC_V1190a__ctrl_reg_1 ;

static short volatile *ps_TDC_V1190a__stat_reg_1 ;

static short volatile *ps_TDC_V1190a__geo_adr ;

static short volatile *ps_TDC_V1190a__module_reset ;

static short volatile *ps_TDC_V1190a__sw_clr ;

static short volatile *ps_TDC_V1190a__sw_evt_reset ;

static short volatile *ps_TDC_V1190a__sw_trig ;

static short volatile *pl_TDC_V1190a__evt_cnt ;

static short volatile *ps_TDC_V1190a__firmware_rev ;

static short volatile *ps_TDC_V1190a__micro_reg ;

static short volatile *ps_TDC_V1190a__micro_hdshk_reg ;

static short volatile *ps_TDC_V1190a__oui_2 ;

static short volatile *ps_TDC_V1190a__oui_1 ;

static short volatile *ps_TDC_V1190a__oui_0 ;

static short volatile *ps_TDC_V1190a__board_ver ;

static short volatile *ps_TDC_V1190a__board_id_2 ;

static short volatile *ps_TDC_V1190a__board_id_1 ;

static short volatile *ps_TDC_V1190a__board_id_0 ;

static short volatile *ps_TDC_V1190a__revision_3 ;

static short volatile *ps_TDC_V1190a__revision_2 ;

static short volatile *ps_TDC_V1190a__revision_1 ;

static short volatile *ps_TDC_V1190a__revision_0 ;

static short volatile *ps_TDC_V1190a__serial_1 ;

static short volatile *ps_TDC_V1190a__serial_0 ;

int l_mod;

int l_ch;

long l_event_counter;

/*****************************************************************************/

/*****************************************************************************/

int f_user_get_virt_ptr (long *pl_loc_hwacc, long pl_rem_cam[])

{

int i;

long l_i, l_j;

/*

* create virtual pointer to be used in f_user_init and f_user_readout

*/

l_event_counter = 0;

//***************

// CAEN mapping

//***************

{ //#ifdef CAEN

pl_VME_virtual_mem_base = (long*) ((long)pl_loc_hwacc) ;

} //#endif // CAEN

// *****************************************************************************/

{

// * create virtual pointer to be used in f_user_init and f_user_readout

/*------------------------------------------------------------------------------*/

/* TB on VULOM3 */

/*------------------------------------------------------------------------------*/

{

pl_TB__base = (long*) ((long) pl_VME_virtual_mem_base + TB__OFFSET ) ;

pl_TB__Ch_enable_reg_F_0 = (long*) ( (long) pl_TB__base + 0x0000 );

pl_TB__scale_down_7_0 = (long*) ( (long) pl_TB__base + 0x0004 );

pl_TB__scale_down_F_8 = (long*) ( (long) pl_TB__base + 0x0008 ) ;

pl_TB__latch_reg = (long*) ( (long) pl_TB__base + 0x000c );

pl_TB__version = (long*) ( (long) pl_TB__base + 0x003c );

long l_ch ;

for (l_ch=0; l_ch<TB__No_Ch; l_ch++)

{ pl_TB__scaler_inp[l_ch] =

(long*) ( (long) pl_TB__base + 0x0040 +(l_ch*4));

pl_TB__scaler_inhib[l_ch] =

(long*) ( (long) pl_TB__base + 0x0080 +(l_ch*4));

pl_TB__scaler_after_reduction[l_ch] =

(long*) ( (long) pl_TB__base + 0x00c0 +(l_ch*4));

}

}

/*------------------------------------------------------------------------------*/

/* ADC CAEN 785AH */

/*------------------------------------------------------------------------------*/

for (l_mod = 0 ; l_mod < ADC_V785__No_Mod; l_mod++)

{

pl_ADC_V785__base[l_mod] = (long*) ( (long) pl_VME_virtual_mem_base + ADC_V785__VME_OFFSET + l_mod * ADC_V785__VME_SIZE) ;

ps_ADC_V785__firm_rev[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1000 );

ps_ADC_V785__geo_adr[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1002 );

ps_ADC_V785__oui_msb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8026 );

ps_ADC_V785__oui[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802a );

ps_ADC_V785__oui_lsb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802e );

ps_ADC_V785__version[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8032 );

ps_ADC_V785__board_id_msb[l_mod]= (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8036 );

ps_ADC_V785__board_id[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802a );

ps_ADC_V785__board_id_lsb[l_mod]= (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x802e );

ps_ADC_V785__revision[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x804e );

ps_ADC_V785__serial_msb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8f02 );

ps_ADC_V785__serial_lsb[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x8f06 );

pl_ADC_V785__outp_buffer[l_mod]= (long*) ( (long) pl_ADC_V785__base[l_mod] + 0x0000 );

ps_ADC_V785__bit_set_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1006 );

ps_ADC_V785__bit_clr_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1008 );

ps_ADC_V785__stat_reg_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x100e );

ps_ADC_V785__ctrl_reg_1[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1010 );

ps_ADC_V785__stat_reg_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1022 );

ps_ADC_V785__bit_set_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1032 );

ps_ADC_V785__bit_clr_2[l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1034 );

for (l_ch=0; l_ch<ADC_V785__No_Ch; l_ch++)

{

ps_ADC_V785__threshs[l_ch][l_mod] = (short*) ( (long) pl_ADC_V785__base[l_mod] + 0x1080 + l_ch * 0x0002 );

}

}

/*------------------------------------------------------------------------------*/

/* Scaler CAEN V830 */

... 832 more lines ...

|

| Attachment 2: mbslog.l

|

22-Oct-18 16:39:14#R4-54 :msg_log :Message logger running

22-Oct-18 16:39:21+R4-54 :dispatch :>>> Start procedure "startup.scom" break mode 1

22-Oct-18 16:39:21#R4-54 :dispatch :start task m_util

22-Oct-18 16:39:22#R4-54 :util :task m_util started

22-Oct-18 16:39:22#R4-54 :util :load setup setup.usf

22-Oct-18 16:39:22#R4-54 :util :setup file setup.usf successfully loaded

22-Oct-18 16:39:22+R4-54 :util :load setup finished (x0)

22-Oct-18 16:39:22#R4-54 :util :set trig_mod

22-Oct-18 16:39:22#R4-54 :util :trigger module set up as MASTER, crate nr: 0

22-Oct-18 16:39:22+R4-54 :util :set trig_mod finished (x0)

22-Oct-18 16:39:22#R4-54 :util :enable irq

22-Oct-18 16:39:23+R4-54 :util :enable irq finished (x0)

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_read_meb "./m_read_meb"

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_collector

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_transport

22-Oct-18 16:39:23#R4-54 :dispatch :start task m_stream_serv

22-Oct-18 16:39:24#R4-54 :dispatch :start task m_daq_rate

22-Oct-18 16:39:26!R4-54 :read_meb :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:39:27!R4-54 :collector :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:39:27#R4-54 :read_meb :task m_read_meb started

22-Oct-18 16:39:27#R4-54 :stream_serv:task m_stream_serv started

22-Oct-18 16:39:27#R4-54 :collector :task m_collector started

22-Oct-18 16:39:27#R4-54 :transport :task m_transport started

22-Oct-18 16:39:27#R4-54 :transport :enable tcp

22-Oct-18 16:39:27#R4-54 :transport :starting server in inclusive mode

22-Oct-18 16:39:27+R4-54 :transport :enable tcp finished (x0)

22-Oct-18 16:39:27+R4-54 :dispatch :>>> End procedure "startup.scom"

22-Oct-18 16:39:27#R4-54 :transport :waiting for client (port 6000)

22-Oct-18 16:39:30#R4-54 :util :start acquisition

22-Oct-18 16:39:30+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:39:31#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:39:31#R4-54 :collector :acquisition running

22-Oct-18 16:42:19#R4-54 :util :stop acquisition

22-Oct-18 16:42:21+R4-54 :util :stop acquisition finished (x0)

22-Oct-18 16:42:21#R4-54 :collector :acquisition NOT running

22-Oct-18 16:42:21#R4-54 :read_meb :found trig type 15 == stop acquisition

22-Oct-18 16:45:08#R4-54 :util :start acquisition

22-Oct-18 16:45:08+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:45:09#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:45:10#R4-54 :collector :acquisition running

22-Oct-18 16:45:19!R4-54 :dispatch :Key "events" > invalid value "v"!

22-Oct-18 16:45:19!R4-54 :dispatch :Command not executed

22-Oct-18 16:45:19!R4-54 :dispatch :Command "type event v 10" finished with argument error (20)

22-Oct-18 16:45:34#R4-54 :transport :type event -v 10

22-Oct-18 16:45:34+R4-54 :transport :type event finished (x0)

22-Oct-18 16:45:41#R4-54 :util :stop acquisition

22-Oct-18 16:45:43+R4-54 :util :stop acquisition finished (x0)

22-Oct-18 16:45:43#R4-54 :collector :acquisition NOT running

22-Oct-18 16:45:43#R4-54 :read_meb :found trig type 15 == stop acquisition

22-Oct-18 16:45:52#R4-54 :util :start acquisition

22-Oct-18 16:45:52+R4-54 :util :start acquisition finished (x0)

22-Oct-18 16:45:52#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 16:45:53#R4-54 :collector :acquisition running

22-Oct-18 16:46:36#R4-54 :transport :type event -v 10

22-Oct-18 16:46:36+R4-54 :transport :type event finished (x0)

22-Oct-18 16:52:38#R4-54 :stream_serv:140.181.81.77 connected

22-Oct-18 16:55:03!R4-54 :stream_serv:received CLOSE, client disconnected!

22-Oct-18 16:55:25#R4-54 :msg_log :Message logger running

22-Oct-18 16:58:29+R4-54 :dispatch :>>> Start procedure "startup.scom" break mode 1

22-Oct-18 16:58:29#R4-54 :dispatch :start task m_util

22-Oct-18 16:58:30#R4-54 :util :task m_util started

22-Oct-18 16:58:30#R4-54 :util :load setup setup.usf

22-Oct-18 16:58:30#R4-54 :util :setup file setup.usf successfully loaded

22-Oct-18 16:58:30+R4-54 :util :load setup finished (x0)

22-Oct-18 16:58:30#R4-54 :util :set trig_mod

22-Oct-18 16:58:30#R4-54 :util :trigger module set up as MASTER, crate nr: 0

22-Oct-18 16:58:30+R4-54 :util :set trig_mod finished (x0)

22-Oct-18 16:58:30#R4-54 :util :enable irq

22-Oct-18 16:58:30+R4-54 :util :enable irq finished (x0)

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_read_meb "./m_read_meb"

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_collector

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_transport

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_stream_serv

22-Oct-18 16:58:30#R4-54 :dispatch :start task m_daq_rate

22-Oct-18 16:58:34!R4-54 :read_meb :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:58:35!R4-54 :collector :Pipe type 0: smem_create for base 0x8000000

22-Oct-18 16:58:37#R4-54 :read_meb :task m_read_meb started

22-Oct-18 16:58:37#R4-54 :collector :task m_collector started

22-Oct-18 16:58:37#R4-54 :stream_serv:task m_stream_serv started

22-Oct-18 16:58:37#R4-54 :transport :task m_transport started

22-Oct-18 16:58:37#R4-54 :transport :enable tcp

22-Oct-18 16:58:37#R4-54 :transport :starting server in inclusive mode

22-Oct-18 16:58:37+R4-54 :transport :enable tcp finished (x0)

22-Oct-18 16:58:37+R4-54 :dispatch :>>> End procedure "startup.scom"

22-Oct-18 16:58:37#R4-54 :transport :waiting for client (port 6000)

22-Oct-18 16:59:50#R4-54 :stream_serv:140.181.81.77 connected

22-Oct-18 17:00:03#R4-54 :util :start acquisition

22-Oct-18 17:00:03+R4-54 :util :start acquisition finished (x0)

22-Oct-18 17:00:03#R4-54 :read_meb :found trig type 14 == start acquisition

22-Oct-18 17:00:03#R4-54 :collector :acquisition running

22-Oct-18 17:01:26!R4-54 :dispatch :Key "events" > invalid value "v"!

22-Oct-18 17:01:26!R4-54 :dispatch :Command not executed

22-Oct-18 17:01:26!R4-54 :dispatch :Command "type event v" finished with argument error (20)

22-Oct-18 17:01:29#R4-54 :transport :type event -v

22-Oct-18 17:01:29+R4-54 :transport :type event finished (x0)

22-Oct-18 17:02:29#R4-54 :transport :type event -v

22-Oct-18 17:02:29+R4-54 :transport :type event finished (x0)

23-Oct-18 10:47:03#R4-54 :transport :type event -v 5

23-Oct-18 10:47:03+R4-54 :transport :type event finished (x0)

23-Oct-18 14:07:59!R4-54 :stream_serv:NODATA, client disconnected!

23-Oct-18 14:37:32#R4-54 :msg_log :Message logger running

23-Oct-18 14:38:37!R4-54 :dispatch :>>> Procedure "startup.scom" not found!

23-Oct-18 14:38:43#R4-54 :util :data acquisition was already started ���

23-Oct-18 14:39:03#R4-54 :util :show acquisition

23-Oct-18 14:39:04+R4-54 :util :show acquisition finished (x0)

23-Oct-18 14:41:16!R4-54 :dispatch :Command not found: "-R4-54"!

23-Oct-18 14:41:23!R4-54 :dispatch :Command key missing: type

23-Oct-18 14:41:55#R4-54 :transport :type event -v

23-Oct-18 14:42:11#R4-54 :transport :type event -v 3

23-Oct-18 14:59:29#R4-54 :util :start acquisition

23-Oct-18 14:59:29+R4-54 :util :start acquisition finished (x0)

23-Oct-18 14:59:45#R4-54 :transport :type event -v

23-Oct-18 15:00:39#R4-54 :util :show acquisition

23-Oct-18 15:00:40+R4-54 :util :show acquisition finished (x0)

23-Oct-18 15:49:53#R4-54 :util :show acquisition

23-Oct-18 15:49:54+R4-54 :util :show acquisition finished (x0)

23-Oct-18 15:50:15+R4-54 :transport :type event finished (x0)

23-Oct-18 15:55:44!R4-54 :stream_serv:received CLOSE, client disconnected!

23-Oct-18 16:11:45!R4-54 :stream_serv:received CLOSE, client disconnected!

23-Oct-18 16:17:30#R4-54 :stream_serv:show stream_serv

23-Oct-18 16:17:30#R4-54 :stream_serv:Streams: total 7622, sent 3811 (50.0%), free 8.

23-Oct-18 16:17:58#R4-54 :stream_serv:set stream_serv 1

23-Oct-18 16:17:58+R4-54 :stream_serv:set stream_serv finished (x0)

23-Oct-18 16:18:04#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:18:04+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:18:15#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:18:15+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:10#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:10+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:14#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:14+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:22#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:22+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:25#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:19:25+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:19:34!R4-54 :dispatch :value 0

23-Oct-18 16:19:34!R4-54 :dispatch :Command not executed

23-Oct-18 16:19:41#R4-54 :stream_serv:set stream_serv 1

23-Oct-18 16:19:41+R4-54 :stream_serv:set stream_serv finished (x0)

23-Oct-18 16:20:03#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:03+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:20:08#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:08+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:20:11#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:20:11+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:24:14#R4-54 :stream_serv:Client (asynch), keep none, scale=1

23-Oct-18 16:24:14+R4-54 :stream_serv:show stream_serv finished (x0)

23-Oct-18 16:26:57#R4-54 :stream_serv:140.181.81.77 connected

24-Oct-18 15:05:22#R4-54 :util :stop acquisition

24-Oct-18 15:05:24#R4-54 :collector :acquisition NOT running

26-Oct-18 14:38:49#R4-55 :msg_log :Message logger running

26-Oct-18 14:38:59+R4-55 :dispatch :>>> Start procedure "startup.scom" break mode 1

26-Oct-18 14:38:59#R4-55 :dispatch :start task m_util

26-Oct-18 14:39:02#R4-55 :util :task m_util started

26-Oct-18 14:39:02#R4-55 :util :load setup setup.usf

26-Oct-18 14:39:02#R4-55 :util :setup file setup.usf successfully loaded

26-Oct-18 14:39:02+R4-55 :util :load setup finished (x0)

26-Oct-18 14:39:02#R4-55 :util :set trig_mod

26-Oct-18 14:39:02#R4-55 :util :trigger module set up as MASTER, crate nr: 0

26-Oct-18 14:39:02+R4-55 :util :set trig_mod finished (x0)

26-Oct-18 14:39:02#R4-55 :util :enable irq

26-Oct-18 14:39:02+R4-55 :util :enable irq finished (x0)

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_read_meb "./m_read_meb"

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_collector

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_transport

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_stream_serv

26-Oct-18 14:39:02#R4-55 :dispatch :start task m_daq_rate

26-Oct-18 14:39:07!R4-55 :read_meb :Pipe type 0: smem_create for base 0x8000000

26-Oct-18 14:39:07!R4-55 :collector :Pipe type 0: smem_create for base 0x8000000

26-Oct-18 14:39:08#R4-55 :read_meb :task m_read_meb started

26-Oct-18 14:39:09#R4-55 :stream_serv:task m_stream_serv started

26-Oct-18 14:39:09#R4-55 :collector :task m_collector started

26-Oct-18 14:39:09#R4-55 :transport :task m_transport started

26-Oct-18 14:39:09#R4-55 :transport :enable tcp

26-Oct-18 14:39:09#R4-55 :transport :starting server in inclusive mode

26-Oct-18 14:39:09+R4-55 :transport :enable tcp finished (x0)

26-Oct-18 14:39:09+R4-55 :dispatch :>>> End procedure "startup.scom"

26-Oct-18 14:39:09#R4-55 :transport :waiting for client (port 6000)

26-Oct-18 14:39:23#R4-55 :util :start acquisition

26-Oct-18 14:39:23+R4-55 :util :start acquisition finished (x0)

26-Oct-18 14:39:23#R4-55 :read_meb :found trig type 14 == start acquisition

26-Oct-18 14:39:24#R4-55 :collector :acquisition running

26-Oct-18 14:39:30#R4-55 :transport :type event -v 4

26-Oct-18 14:39:30+R4-55 :transport :type event finished (x0)

26-Oct-18 14:39:33#R4-55 :transport :type event -v 4

26-Oct-18 14:39:33+R4-55 :transport :type event finished (x0)

26-Oct-18 14:49:28#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 14:56:07!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 14:58:24#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 15:11:09!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 15:11:54#R4-55 :stream_serv:140.181.81.77 connected

26-Oct-18 15:13:41!R4-55 :stream_serv:received CLOSE, client disconnected!

26-Oct-18 15:46:38#R4-55 :util :stop acquisition

26-Oct-18 15:46:40+R4-55 :util :stop acquisition finished (x0)

26-Oct-18 15:46:40#R4-55 :collector :acquisition NOT running

26-Oct-18 15:46:40#R4-55 :read_meb :found trig type 15 == stop acquisition

28-Nov-18 10:43:17#R4L-60 :msg_log :Message logger running

28-Nov-18 10:43:22+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_util

28-Nov-18 10:43:22#R4L-60 :util :task m_util started

28-Nov-18 10:43:22#R4L-60 :util :load setup setup.usf

28-Nov-18 10:43:22#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 10:43:22+R4L-60 :util :load setup finished (x0)

28-Nov-18 10:43:22#R4L-60 :util :set trig_mod

28-Nov-18 10:43:22#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 10:43:22+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 10:43:22#R4L-60 :util :enable irq

28-Nov-18 10:43:22+R4L-60 :util :enable irq finished (x0)

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_collector

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_transport

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 10:43:22#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 10:43:22!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:43:22#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:43:23!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:43:23#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:43:23#R4L-60 :transport :task m_transport started

28-Nov-18 10:43:23#R4L-60 :transport :enable tcp

28-Nov-18 10:43:23#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 10:43:23+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 10:43:23+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 10:43:23#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 10:43:23#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 10:48:22#R4L-60 :msg_log :Message logger running

28-Nov-18 10:48:25+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_util

28-Nov-18 10:48:25#R4L-60 :util :task m_util started

28-Nov-18 10:48:25#R4L-60 :util :load setup setup.usf

28-Nov-18 10:48:25#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 10:48:25+R4L-60 :util :load setup finished (x0)

28-Nov-18 10:48:25#R4L-60 :util :set trig_mod

28-Nov-18 10:48:25#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 10:48:25+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 10:48:25#R4L-60 :util :enable irq

28-Nov-18 10:48:25+R4L-60 :util :enable irq finished (x0)

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_collector

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_transport

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 10:48:25#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 10:48:25!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:48:25#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:48:25!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 10:48:25#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 10:48:25#R4L-60 :transport :task m_transport started

28-Nov-18 10:48:25#R4L-60 :transport :enable tcp

28-Nov-18 10:48:25#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 10:48:25+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 10:48:25+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 10:48:25#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 10:48:25#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 10:48:41#R4L-60 :msg_log :exiting.. SIGTERM (kill) signal ���

28-Nov-18 11:01:34#R4L-60 :msg_log :Message logger running

28-Nov-18 11:01:37+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_util

28-Nov-18 11:01:37#R4L-60 :util :task m_util started

28-Nov-18 11:01:37#R4L-60 :util :load setup setup.usf

28-Nov-18 11:01:37#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 11:01:37+R4L-60 :util :load setup finished (x0)

28-Nov-18 11:01:37#R4L-60 :util :set trig_mod

28-Nov-18 11:01:37#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 11:01:37+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 11:01:37#R4L-60 :util :enable irq

28-Nov-18 11:01:37+R4L-60 :util :enable irq finished (x0)

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_collector

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_transport

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 11:01:37#R4L-60 :dispatch :start task m_daq_rate

28-Nov-18 11:01:38!R4L-60 :collector :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 11:01:38#R4L-60 :collector :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 11:01:38!R4L-60 :read_meb :Pipe type 0: smem_create for base 0x8000000

28-Nov-18 11:01:38#R4L-60 :read_meb :failed to open /dev/mem for mbs_se_pipe, �[7m�[5mexiting..�[0m ��

28-Nov-18 11:01:38#R4L-60 :transport :task m_transport started

28-Nov-18 11:01:38#R4L-60 :transport :enable tcp

28-Nov-18 11:01:38#R4L-60 :transport :starting server in inclusive mode

28-Nov-18 11:01:38+R4L-60 :transport :enable tcp finished (x0)

28-Nov-18 11:01:38+R4L-60 :dispatch :>>> End procedure "startup.scom"

28-Nov-18 11:01:38#R4L-60 :transport :waiting for client (port 6000)

28-Nov-18 11:01:38#R4L-60 :stream_serv:task m_stream_serv started

28-Nov-18 11:01:55!R4L-60 :dispatch :Command not found: "ls"!

28-Nov-18 11:01:57!R4L-60 :dispatch :Command not found: "cd .."!

28-Nov-18 11:44:45#R4L-60 :msg_log :Message logger running

28-Nov-18 11:44:51+R4L-60 :dispatch :>>> Start procedure "startup.scom" break mode 1

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_util

28-Nov-18 11:44:51#R4L-60 :util :task m_util started

28-Nov-18 11:44:51#R4L-60 :util :load setup setup.usf

28-Nov-18 11:44:51#R4L-60 :util :setup file setup.usf successfully loaded

28-Nov-18 11:44:51+R4L-60 :util :load setup finished (x0)

28-Nov-18 11:44:51#R4L-60 :util :set trig_mod

28-Nov-18 11:44:51#R4L-60 :util :trigger module set up as MASTER, crate nr: 0

28-Nov-18 11:44:51+R4L-60 :util :set trig_mod finished (x0)

28-Nov-18 11:44:51#R4L-60 :util :enable irq

28-Nov-18 11:44:51+R4L-60 :util :enable irq finished (x0)

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_read_meb "./m_read_meb"

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_collector

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_transport

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_stream_serv

28-Nov-18 11:44:51#R4L-60 :dispatch :start task m_daq_rate

... 21082 more lines ...

|

|